四组合逻辑电路的设计

- 格式:doc

- 大小:176.50 KB

- 文档页数:2

组合逻辑电路的设计和逻辑功能验证一、实验目的1.控制组合逻辑电路的设计主意。

2.学会使用集成电路的逻辑功能表。

二、实验仪器及材料1.数字电路实验箱、双踪示波器、数字万用表。

2.元器件:双输入与门CD4081 1片四异或门CD4070 2片四位数值比较器CD4063 1片三、注重事项及说明1.CMOS门电路的电源电压为+3V—+15V,有些可达18V,实验前应先验证或调节准确,才可给门电路通电,本实验可选+5V供电。

2.门电路的输出端不可直接并联,也不可直接联连电源+5V和电源地,否则将造成门电路永远性损坏。

3.CMOS集成电路的多余输入端不可悬空。

4.实验时应仔细检查,仅当各条联线所有准确无误时,方可通电。

四、实验内容、原理及步骤(1)设计一个一位比较器(大、同、小)的组合电路并验证其逻辑功能。

(2)验证四位数值比较器的逻辑功能。

(3)设计一个八位二进制奇偶检测器的组合电路并验证其逻辑功能。

(4)设计一个两位二进制数比较器(大、同、小)的组合电路(选做)。

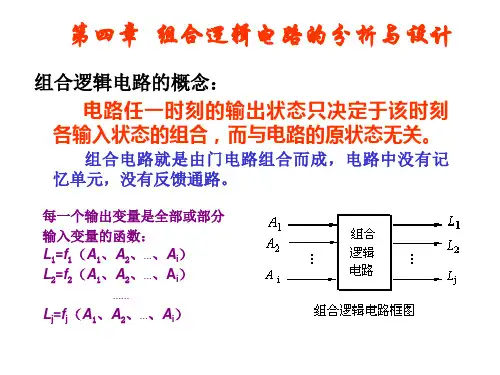

CD4081为四双输入与门;CD4070为四异或门,CD4063为四位数值比较器,它们均为CMOS集成电路。

图4-1为上述三种集成电路的引脚功能描述。

第1 页/共5 页图 6-11.一位(大、同、小)比较器的设计及其逻辑功能的验证 ① 按照命题要求列真值表设A 、B 为两个二进制数的某一位,即比较器的输入,M 、 G 、L 为比较器的输出,分离表示两个二进制数比较后的大、同、小结果,其逻辑功能真值表见表4.1。

② 写表达式按照表4.1的真值表,并为了减少门电路的种类,我们做如下的运算: 同 B A B A B A AB B A G ⊕=+=+= 大 )()(B A A B A B A A B A M ⊕=+== 小 )()(B A B B A B A B B A L ⊕=+== X X =⊕1 ③ 画逻辑图按照上述表达式,读者可用两个异或门和两个与门实现上述的大、同、小比较器,并将逻辑图画在表4.1右边的空白处。

实验四组合逻辑电路研究(设计性实验)一、实验目的1.掌握用SSI器件实现组合逻辑电路的方法。

2.熟悉各种MSI组合逻辑器件的工作原理和引脚功能。

3.掌握用MSI组合逻辑器件实现组合逻辑电路的方法。

4.进一步熟悉测试环境的构建和组合逻辑电路的测试方法。

二、实验所用仪器设备1.Multisim10中的虚拟仪器2.Quartus II中的功能仿真工具3.GW48-EDA实验开发系统三、实验说明1. 组合逻辑电路的设计一般可按以下步骤进行(1)逻辑抽象:将文字描述的逻辑命题转换成真值表。

(2)选择器件类型:根据命题的要求和器件的功能决定采用哪种器件。

(3)根据真值表和所选用的逻辑器件写出相应的逻辑表达式:当采用SSI集成门电路设计时,为了使电路最简,应将逻辑表达式化简,并变换成与门电路相对应的最简式;当采用MSI组合逻辑器件设计时,则不用化简,只需将由最小项构成的函数式变换成MSI器件所需要的函数形式。

(4)根据化简或变换后的逻辑表达式及选用的逻辑器件画出逻辑电路图。

2. 常见的SSI和MSI的型号(1)常见的SSI:四2输入异或门74LS86,四2输入与非门74LS00,六非门74LS04,二4输入与非门74LS20,四2输入或非门74LS02,四2输入与门74LS08等。

(2)常见的MSI:二2-4译码器74LS139,3-8译码74LS138,4-16译码器74LS154,8-3线优先编码器74LS148,七段字符译码器74LS248,四位全加器74LS283,四2选1数据选择器74LS157,双4选1数据选择器74LS153,8选1数据选择器74LS151,16选1数据选择器74LS150等。

四、实验内容(一)基本命题1.设计一个多输出的逻辑网络,它的输入是8421BCD码,它的输出定义为:(1)F1:检测到输入数字能被3整除。

(2)F2:检测到输入数字大于或等于4。

(3)F3:检测到输入数字小于7。

实验一组合逻辑电路的设计

1.实验目的

1,掌握组合逻辑电路的功能分析与测试

2,学会设计以及实现一位全/减加器电路,以及舍入与检测电路设计。

2.实验器材

74LS00 二输入四与非门

74LS04 六门反向器

74LS10 三输入三与非门

74LS86 二输入四异或门

74LS73 负沿触发JK触发器

74LS74 双D触发器

3.实验内容

1>.设计舍入与检测的逻辑电路:

1. 输入:4位8421码,从0000-1001

输入信号接4个开关,从开关输入。

2. 输出:

当8421码>=0101(5)时,有输出F1=1

当8421码中1的个数是奇数时,有输出F2=1,

2>,设计一位全加/全减器

如图所视:

电路框图

当s=1,时做减法运算,s=0时做加法运算。

A,B,C分别表示减数,被减数,借位(加数,被加数,进位)

4.实验步骤

1>.设计一个舍入与检测逻辑电路:

做出真值表:

作出卡诺图,并求出F1,F2

根据F1F2的表达式做出电路图:

按照电路图连接号电路,并且验证结果是否与设计相符。

2,>设计一位全加/全减器

做出真值表:

F1的卡诺图

F1卡诺图:

F2的卡诺图

按照电路图连接号电路,并且验证结果是否与设计相符。

5.实验体会

通过这次试验,我了解了用仪器拼接电路的基本情况。

懂得了从电路图到真实电路的基本过程。

在连接的时候,很容易因为线或者门出现问题。

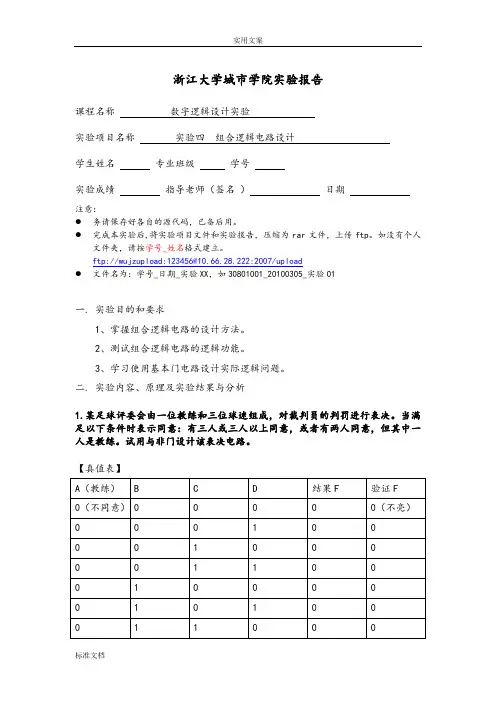

浙江大学城市学院实验报告课程名称数字逻辑设计实验实验项目名称实验四组合逻辑电路设计学生姓名专业班级学号实验成绩指导老师(签名)日期注意:●务请保存好各自的源代码,已备后用。

●完成本实验后,将实验项目文件和实验报告,压缩为rar文件,上传ftp。

如没有个人文件夹,请按学号_姓名格式建立。

ftp://wujzupload:123456@10.66.28.222:2007/upload●文件名为:学号_日期_实验XX,如30801001_20100305_实验01一. 实验目的和要求1、掌握组合逻辑电路的设计方法。

2、测试组合逻辑电路的逻辑功能。

3、学习使用基本门电路设计实际逻辑问题。

二. 实验内容、原理及实验结果与分析1.某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。

当满足以下条件时表示同意:有三人或三人以上同意,或者有两人同意,但其中一人是教练。

试用与非门设计该表决电路。

【真值表】【逻辑表达式】【最简逻辑表达式】F=AB+AD+AC+BCD 【原理图】【功能波形图】【实验照片】2. 设计一个保密锁电路,保密锁上有三个键钮A、B、C。

要求当三个键钮都不按下时既不开锁也不报警;当三个键钮同时按下时,或A、B两个同时按下时,锁就能被打开即开锁指示灯亮;而当不符合上列组合状态时,报警指示灯亮。

试设计此电路,列出真值表,写出函数式,画出最简的实验电路。

(用最少的与非门实现)。

(注:取A、B、C三个键钮状态为输入变量,开锁信号和报警信号为输出变量,分别用F1用F2表示。

设键钮按下时为“1”,不按时为“0”;报警时为“1”,不报警时为“0”,A、B、C都不按时,应不开锁也不报警。

)【真值表】【逻辑表达式】【最简逻辑表达式】F1=AB【原理图】【功能波形图】【实验照片】3. 某雷达站有三部雷达A、B、C,其中A、B功率消耗相等,C的功率是A的两倍。

这些雷达由两台发电机X和Y供电,发电机X的最大输出功率等于雷达A 的功率消耗,发电机Y的最大功率是X的三倍。

实验四 组合逻辑电路的设计(二)

一、实验目的

1. 熟悉各种常用MSI 组合逻辑电路的功能与使用方法; 2. 掌握多片MSI 组合逻辑电路的级联、功能扩展; 3. 学会使用MSI 逻辑器件设计组合电路;

4. 进一步培养查找和排除数字电路常见故障的能力。

二、实验器件

1. 74LS151 八选一数据选择器 2. 74LS283 四位二进制全加器 三、实验原理

见实验三。

四、设计举例

例:使用全加器实现四位二进制相减。

原理:减去某个二进制数就是加上该数的补码(即反码加“1”),所以二进制数A 和B 相加,先将B 变为反码,然后与数A 相加,并令C1=1,即可。

电路如图4—1示:

A 0A 2A 3

A 1

被减数

减数

B 0 B 1B 2B 3

V CC

C 4

C 1

C 0∑

∑1

∑2∑3

∑0图 4-1

例:设计一四变量输入组合逻辑电路。

当四个输入中有奇数个高电平“1”时

输出高电平“1”,否则输出低电平“0”。

原理:设输入四变量为DCBA ,输出为Y ,其真值表入图4—2(a )所示,输出函数Y 为:

Y

B C

D

A B

C

D 1D 2D 3D 4D 5D 6D 7

D 0∙∙∙

∙

∙∙

A

(b)

用八选一数据选择器实现四变量逻辑函数时,以其中3个变量做地址,另外一个变量做数据。

选DCB三变量作为地址,A为数据,画出电路图如图4—2(b):五、实验内容

1.用八选一数据选择器74LS151设计一个8421BCD非法码检测电路,当输入为非法码组时,输出为1,否则为零。

2.用全加器实现2位二进制数相乘。

六、实验报告要求

1.画出各实验步骤的实验电路逻辑图,并分析实验结果。

2.总结MSI器件的功能及使用方法。