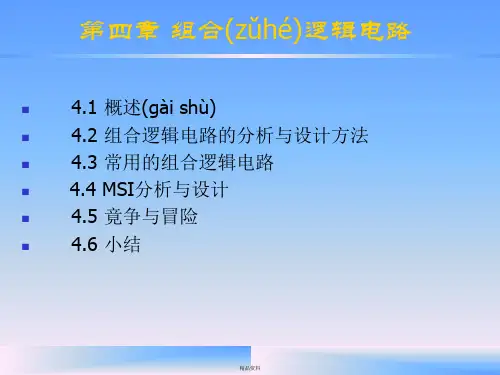

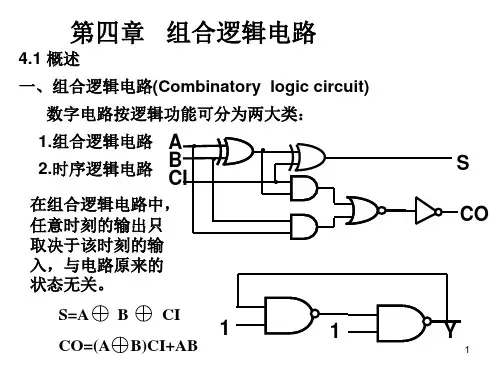

模块4组合逻辑电路

- 格式:pdf

- 大小:5.81 MB

- 文档页数:20

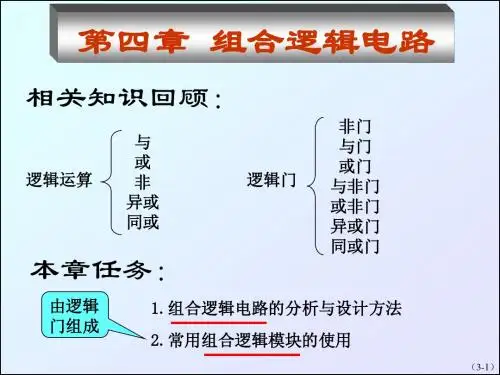

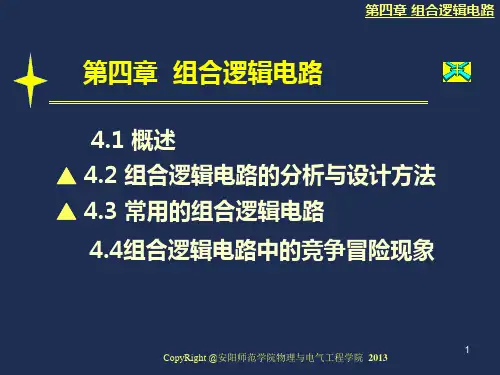

组合逻辑电路的基本单元组合逻辑电路是由组合逻辑门组成的电路,是数字电子电路的一种。

组合逻辑门是组合逻辑电路的基本单元,可以执行基本的逻辑运算,并将输入值转换为输出值。

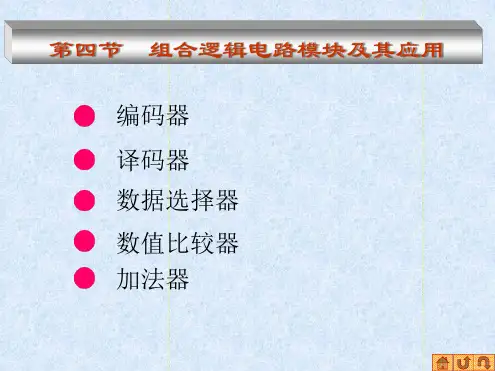

组合逻辑电路常用于构建数学和逻辑表达式的计算机程序,并在数字系统中用于数据加工、数据编码、决策进程等方面。

组合逻辑门基本上由若干个输入和一个输出组成。

组合逻辑门有以下四种类型:1. 与门(AND Gate):当输入信号全部为高电平时,输出信号才为高电平,否则输出信号为低电平。

2. 或门(OR Gate):当输入信号中至少有一个高电平时,输出信号就会为高电平,否则输出信号为低电平。

3. 非门(NOT Gate):将输入信号取反,如输入为高电平,则输出为低电平,反之亦然。

4. 与非门(NAND Gate):若输入信号全部为高电平,则输出为低电平,否则输出为高电平。

它们的实现可以通过逻辑门的组合或串联来达成,以实现更加复杂的逻辑运算。

例如,在数字系统中,可以通过组合逻辑门来实现加法器、减法器等算术运算,也可以用于实现复杂的控制逻辑,如电路的选择、流程控制和存储器单元等。

在现实应用中,组合逻辑门还会涉及到时序、噪声、功率、热等问题,因此电路设计人员必须考虑这些问题。

同时,由于逻辑门的工作原理是建立在开关电路的基础上的,因此在实际使用过程中,需要考虑电路的实际应用,包括运行速度、电源噪波、阻抗匹配和测试等技术问题。

总而言之,组合逻辑门是组合逻辑电路的基本单元,通过不同类型的逻辑运算得出输出信号。

在数字系统中,组合逻辑电路的应用潜力广泛,可以应用于各种数据处理、数据编码和数据解码等方面。

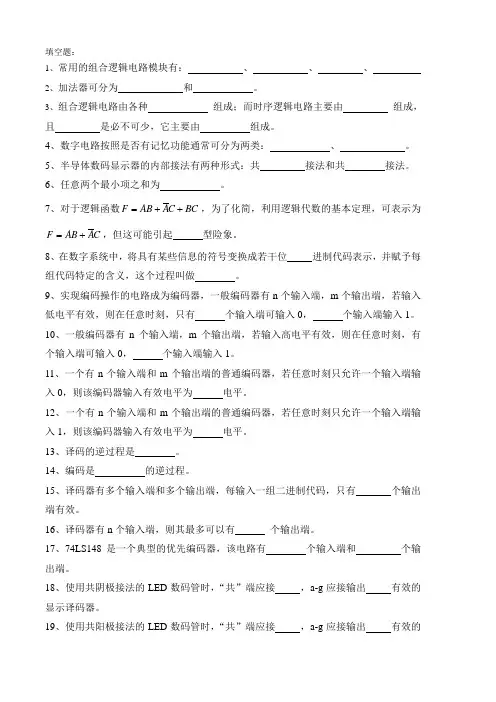

填空题:1、常用的组合逻辑电路模块有:、、、2、加法器可分为和。

3、组合逻辑电路由各种组成;而时序逻辑电路主要由组成,且是必不可少,它主要由组成。

4、数字电路按照是否有记忆功能通常可分为两类:、。

5、半导体数码显示器的内部接法有两种形式:共接法和共接法。

6、任意两个最小项之和为。

7、对于逻辑函数BC+=,为了化简,利用逻辑代数的基本定理,可表示为CF+ABAF+AB=,但这可能引起型险象。

AC8、在数字系统中,将具有某些信息的符号变换成若干位进制代码表示,并赋予每组代码特定的含义,这个过程叫做。

9、实现编码操作的电路成为编码器,一般编码器有n个输入端,m个输出端,若输入低电平有效,则在任意时刻,只有个输入端可输入0,个输入端输入1。

10、一般编码器有n个输入端,m个输出端,若输入高电平有效,则在任意时刻,有个输入端可输入0,个输入端输入1。

11、一个有n个输入端和m个输出端的普通编码器,若任意时刻只允许一个输入端输入0,则该编码器输入有效电平为电平。

12、一个有n个输入端和m个输出端的普通编码器,若任意时刻只允许一个输入端输入1,则该编码器输入有效电平为电平。

13、译码的逆过程是。

14、编码是的逆过程。

15、译码器有多个输入端和多个输出端,每输入一组二进制代码,只有个输出端有效。

16、译码器有n个输入端,则其最多可以有个输出端。

17、74LS148是一个典型的优先编码器,该电路有个输入端和个输出端。

18、使用共阴极接法的LED数码管时,“共”端应接,a-g应接输出有效的显示译码器。

19、使用共阳极接法的LED数码管时,“共”端应接,a-g应接输出有效的显示译码器。

20、组合逻辑电路的特点是:电路在任一时刻输出信号稳态值由 决定(a 、该时刻电路输入信号;b 、信号输入前电路原状态),与 无关(a 、该时刻电路输入信号;b 、信号输入前电路原状态),属于 (a 、有;b 、非)记忆逻辑电路。

21、逻辑表达式))((C A B A Z ++=可能会产生 型险象。