4-4组合逻辑电路

- 格式:ppt

- 大小:1.57 MB

- 文档页数:26

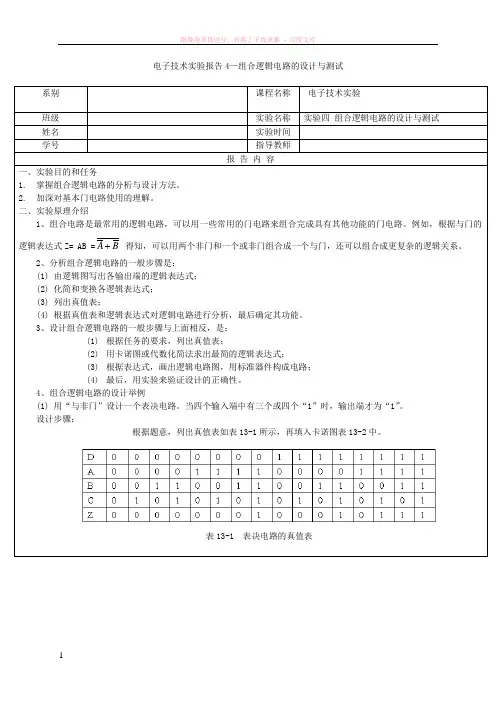

电子技术实验报告4—组合逻辑电路的设计与测试系别课程名称电子技术实验班级实验名称实验四组合逻辑电路的设计与测试姓名实验时间学号指导教师报告内容一、实验目的和任务1.掌握组合逻辑电路的分析与设计方法。

2.加深对基本门电路使用的理解。

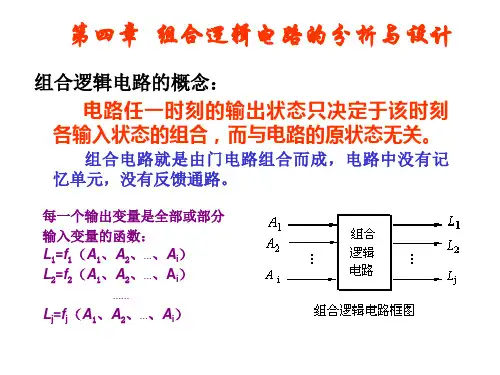

二、实验原理介绍1、组合电路是最常用的逻辑电路,可以用一些常用的门电路来组合完成具有其他功能的门电路。

例如,根据与门的得知,可以用两个非门和一个或非门组合成一个与门,还可以组合成更复杂的逻辑关系。

逻辑表达式Z= AB =A B2、分析组合逻辑电路的一般步骤是:(1)由逻辑图写出各输出端的逻辑表达式;(2)化简和变换各逻辑表达式;(3)列出真值表;(4)根据真值表和逻辑表达式对逻辑电路进行分析,最后确定其功能。

3、设计组合逻辑电路的一般步骤与上面相反,是:(1)根据任务的要求,列出真值表;(2)用卡诺图或代数化简法求出最简的逻辑表达式;(3)根据表达式,画出逻辑电路图,用标准器件构成电路;(4)最后,用实验来验证设计的正确性。

4、组合逻辑电路的设计举例(1) 用“与非门”设计一个表决电路。

当四个输入端中有三个或四个“1”时,输出端才为“1”。

设计步骤:根据题意,列出真值表如表13-1所示,再填入卡诺图表13-2中。

表13-1 表决电路的真值表表13-2 表决电路的卡诺图然后,由卡诺图得出逻辑表达式,并演化成“与非”的形式: ABD CDA BCD ABC Z +++=最后,画出用“与非门”构成的逻辑电路如图13-1所示:图13-1 表决电路原理图输入端接至逻辑开关(拨位开关)输出插口,输出端接逻辑电平显示端口,自拟真值表,逐次改变输入变量,验证逻辑功能。

三、实验内容和数据记录1、设计一个四人无弃权表决电路(多数赞成则提议通过,即三人以上包括三人),要求用2四输入与非门来实现。

用74LS20实现逻辑函数的接线图实验测得真值表如下:D C B A Z0 0 0 0 00 0 0 1 00 0 1 0 00 0 1 1 00 1 0 0 00 1 0 1 00 1 1 0 10 1 1 1 01 0 0 0 01 0 0 1 01 0 1 0 01 0 1 1 11 1 0 0 01 1 0 1 11 1 1 0 11 1 1 1 1四、实验结论与心得1. 该实验存在一定测量误差,误差来源于电路箱中得误差,但是误差实验允许范围内,故该实验有效。

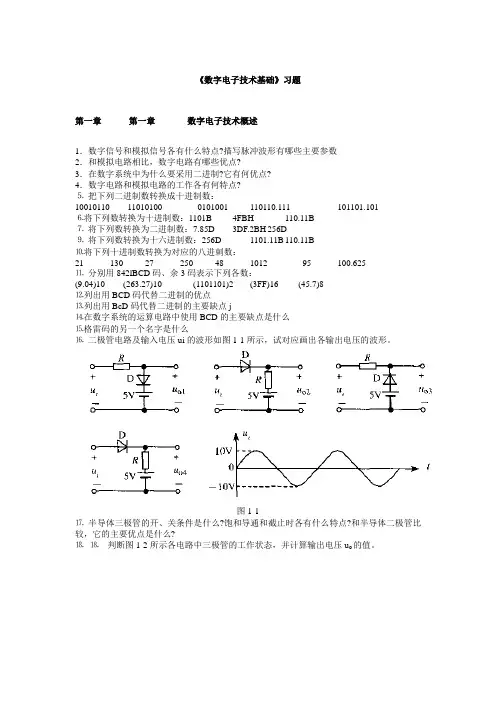

《数字电子技术基础》习题第一章第一章数字电子技术概述1.数字信号和模拟信号各有什么特点?描写脉冲波形有哪些主要参数2.和模拟电路相比,数字电路有哪些优点?3.在数字系统中为什么要采用二进制?它有何优点?4.数字电路和模拟电路的工作各有何特点?⒌把下列二进制数转换成十进制数:10010110 11010100 0101001 110110.111 101101.101⒍将下列数转换为十进制数:1101B 4FBH 110.11B⒎将下列数转换为二进制数:7.85D 3DF.2BH 256D⒐将下列数转换为十六进制数:256D 1101.11B 110.11B⒑将下列十进制数转换为对应的八进刺数:21 130 27 250 48 1012 95 100.625⒒分别用842lBCD码、余3码表示下列各数:(9.04)10 (263.27)10 (1101101)2 (3FF)16 (45.7)8⒓列出用BCD码代替二进制的优点⒔列出用BcD码代替二进制的主要缺点j⒕在数字系统的运算电路中使用BCD的主要缺点是什么⒖格雷码的另一个名字是什么⒗二极管电路及输入电压ui的波形如图1-1所示,试对应画出各输出电压的波形。

图1-1⒘半导体三极管的开、关条件是什么?饱和导通和截止时各有什么特点?和半导体二极管比较,它的主要优点是什么?⒙⒙判断图1-2所示各电路中三极管的工作状态,并计算输出电压u o的值。

图1-2⒚N沟造增强型MOS管的开、关条件是什么?导通和截止时各有什么特点?和P沟道增强型MOS管比较,两者的主要区别是什么?第二章第二章集成逻辑门电路⒈请举出生活中有关“与”、“或”、“非”的逻辑概念.并各举两个例子说明。

⒉如图2-1所示,是二极管门电路,请分析各电路的逻辑功能.并写出其表达式。

图2-1⒊电路如图2-2所示,写出输出L的表达式。

设电路中各元件参数满足使三极管处于饱和及截止的条件。

图2-2⒋TTL与非门典型电路中输出电路一般采用电路。

4用小规模集成电路进行组合逻辑电路设计小规模集成电路(Small Scale Integrated Circuits,SSI)是指集成电路芯片中的逻辑门数量相对较少的类型。

在组合逻辑电路设计中,SSI可用于实现各种逻辑功能,如逻辑门、多路选择器等。

首先,我们需要了解一些基本的逻辑门。

1. 与门(AND Gate):该门有两个或多个输入端和一个输出端。

只有当所有输入都为高电平时,输出才为高电平。

2. 或门(OR Gate):该门有两个或多个输入端和一个输出端。

只要有一个输入为高电平,输出就为高电平。

3. 非门(NOT Gate):该门只有一个输入端和一个输出端。

输出和输入相反,即输入为高电平时,输出为低电平;输入为低电平时,输出为高电平。

4. 异或门(XOR Gate):该门有两个输入端和一个输出端。

只有当输入相同时,输出为低电平;当输入不同时,输出为高电平。

利用以上逻辑门,我们可以进行组合逻辑电路设计。

以下是一个例子:设计一个2位全加器(Full Adder)。

全加器是一种组合逻辑电路,可用于将两个二进制数字相加。

它有两个输入A和B,分别代表两个二进制位,还有一个输入Cin,代表低位的进位。

输出有两位,S代表和的位,Cout代表进位。

我们可以使用AND门、OR门和XOR门来实现全加器。

以下是全加器的真值表:Cin , A , B , S , Cout:---:,:---:,:---:,:-:,:--:0,0,0,0,00,0,1,1,00,1,0,1,00,1,1,0,11,0,0,1,01,0,1,0,11,1,0,0,11,1,1,1,1根据真值表,我们可以得到全加器的逻辑表达式:S = A XOR B XOR Cin (第一个异或门)Cout = (A AND B) OR (Cin AND (A XOR B))然后,我们可以使用小规模集成电路实现该逻辑电路。

以74LS86为例,它是一个4个2输入异或门的小规模集成电路,每个异或门具有两个输入和一个输出。

维修电工高级工试题库单选四4-1、当74 LS94 的SL与Q0 相连时,电路实现的功能为( A )。

A、左移环形计数器B、右移环形计数器C、保持D、并行置数4-2、集成译码器与七段发光二极管构成( C )译码器。

A、变量B、逻辑状态C、数码显示D、数值4-3、时序逻辑电路的清零端有效,则电路为( D )状态。

A、计数B、保持C、置1D、清04-4、组合逻辑电路常采用的分析方法有( D )。

A、逻辑代数化简B、真值表C、逻辑表达式D、以上都是4-5、组合逻辑电路的译码器功能有( D )。

A、变量译码器B、显示译码器C、数码译码器D、以上都是4-6、时序逻辑电路的波形图是( A )。

A、各个触发器的输出随时钟脉冲变化的波形B、各个触发器的输入随时钟脉冲变化的波形C、各个门电路的输出随时钟脉冲变化的波形D、各个门的输入随时钟脉冲变化的波形4-7、移位寄存器可分为( D )。

A、左移B、右移C、可逆D、以上都是4-8、555定时器构成的多谐振荡电路的脉冲频率由( C )决定。

A、输入信号B、输出信号C、电路充放电电阻及电容D、555定时器结构4-9、当74 LS94 的控制信号为11时,该集成移位寄存器处于( D )状态。

A、左移B、右移C、保持D、并行置数4-10、当74 LS94 的Q0 经非门的输出与SL相连时,电路实现的功能为( A )。

A、左移扭环形计数器B、右移扭环形计数器C、保持D、并行置数4-11、集成译码器74LS42是( D )译码器。

A、变量B、显示C、符号D、二--十进制4-12、集成译码器74LS48可点亮( A )显示器。

A、共阴七段B、共阳七段C、液晶D、等离子4-13、集成二--十进制计数器74LS90是( A )计数器。

A、异步二--五--十进制加法B、同步十进制加法C、异步十进制减法D、同步十进制可逆4-14、一片集成二—十进制计数器74L160可构成( C )进制计数器。