4组合逻辑电路

- 格式:pdf

- 大小:661.13 KB

- 文档页数:64

GDOU-B-11-112广东海洋大学学生实验报告书(学生用表)实验名称组合和逻辑电路的设计课程名称电工学课程号学院(系)专业班级学生姓名学号实验地点实验日期一、实验目的掌握组合逻辑电路的设计与测试方法二、实验原理使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。

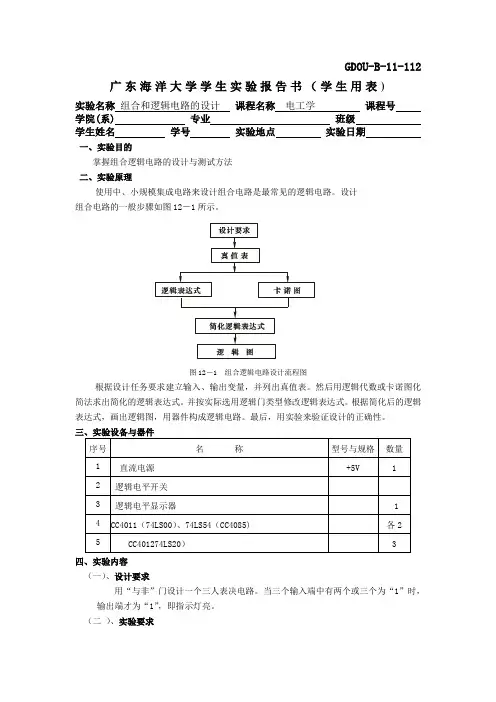

设计组合电路的一般步骤如图12-1所示。

图12-1 组合逻辑电路设计流程图根据设计任务要求建立输入、输出变量,并列出真值表。

然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。

并按实际选用逻辑门类型修改逻辑表达式。

根据简化后的逻辑表达式,画出逻辑图,用器件构成逻辑电路。

最后,用实验来验证设计的正确性。

三、实验设备与器件序号名称型号与规格数量1 直流电源+5V 12 逻辑电平开关3 逻辑电平显示器 14 CC4011(74LS00)、74LS54(CC4085)各25 CC401274LS20) 3四、实验内容(一)、设计要求用“与非”门设计一个三人表决电路。

当三个输入端中有两个或三个为“1”时,输出端才为“1”,即指示灯亮。

(二)、实验要求1、根据控制要求写出真值表和逻辑表达式;2、画出用与非门(学生自选)实现其逻辑功能的逻辑电路图,并交实验指导教师审阅;3、经实验指导教师审阅后,按逻辑电路图接线并带上负载(指示灯),调试电路,应满足设计要求。

五、实验预习要求1、根据实验要求设计组合电路,并根据所给的标准器件画出逻辑图。

2、如何用最简单的方法验证“与或非”门的逻辑功能是否完好?答:与非门,有零出一,双一出零只要将其一端接高电平,另一端来1时出0,来0时出1即可。

或非门反之,将一端接低电平另一端来1出0,来0时出1,即非。

3、“与或非”门中,当某一组与端不用时,应作如何处理?答:对于本实验,可以悬空,也可以置“1”,但是如果是CMOS要接地。

六、实验报告1、根据设计要求,写出实验的设计过程,画出设计的电路图。

2、通过对所设计的电路进行实验测试,记录测试结果。

实验四组合逻辑电路(半加器全加器及逻辑运算)一、实验目的1.掌握组合逻辑电路的功能调试。

2。

验证半加器和全加器的逻辑功能。

3。

学会二进制数的运算规律。

二、实验仪器及材料器件74LS00 二输入端四与非门3片74LS86 二输入端四异或门1片三、预习要求1.预习组合逻辑电路的分析方法.2.预习用与非门和异或门构成的半加器、全加器的工作原理。

3.预习二进制数的运算。

四、实验内容1.组合逻辑电路功能测试。

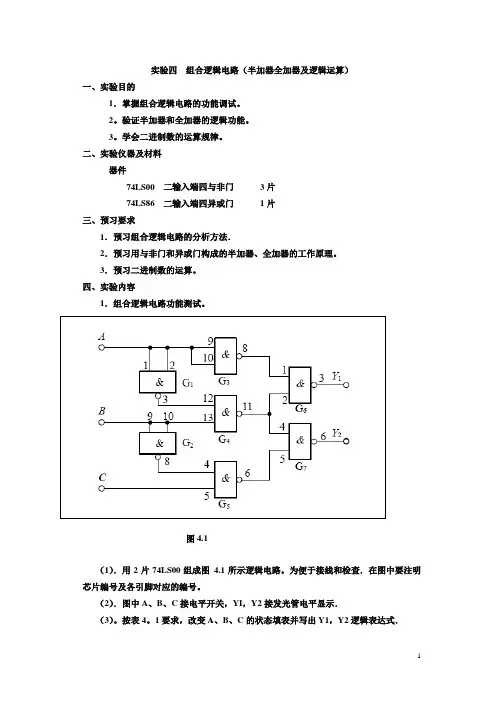

图4.1(1).用2片74LS00组成图4.1所示逻辑电路。

为便于接线和检查.在图中要注明芯片编号及各引脚对应的编号。

(2).图中A、B、C接电平开关,YI,Y2接发光管电平显示.(3)。

按表4。

1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式.(4).将运算结果与实验比较.2.测试用异或门(74LS86)和与非门组成的半加器的逻 辑功能.根据半加器的逻辑表达式可知.半加器Y 是A 、B异或,而进位Z 是A 、B 相与,故半加器可用一个集 成异或门和二个与非门组成如图4.2.(1).在学习机上用异或门和与门接成以上电路. 接电平开关S .Y 、Z 接电平显示.(2).按表4.2要求改变A 、B 状态,填表. 图 4.2 0 1 113.测试全加器的逻辑功能。

(1).写出图4.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表.(3).根据真值表画逻辑函数S i 、 Ci 的卡诺图.图4.3 (4).填写表4.3各点状态(5).按原理图选择与非门并接线进行测试,将测试结果记入表4.4,并与上表进行比较看逻辑功能是否一致.五、实验报告1.整理实验数据、图表并对实验结果进行分析讨论。

2.总结组合逻辑电路的分析方法。

实验四组合逻辑电路研究(设计性实验)一、实验目的1.掌握用SSI器件实现组合逻辑电路的方法。

2.熟悉各种MSI组合逻辑器件的工作原理和引脚功能。

3.掌握用MSI组合逻辑器件实现组合逻辑电路的方法。

4.进一步熟悉测试环境的构建和组合逻辑电路的测试方法。

二、实验所用仪器设备1.Multisim10中的虚拟仪器2.Quartus II中的功能仿真工具3.GW48-EDA实验开发系统三、实验说明1. 组合逻辑电路的设计一般可按以下步骤进行(1)逻辑抽象:将文字描述的逻辑命题转换成真值表。

(2)选择器件类型:根据命题的要求和器件的功能决定采用哪种器件。

(3)根据真值表和所选用的逻辑器件写出相应的逻辑表达式:当采用SSI集成门电路设计时,为了使电路最简,应将逻辑表达式化简,并变换成与门电路相对应的最简式;当采用MSI组合逻辑器件设计时,则不用化简,只需将由最小项构成的函数式变换成MSI器件所需要的函数形式。

(4)根据化简或变换后的逻辑表达式及选用的逻辑器件画出逻辑电路图。

2. 常见的SSI和MSI的型号(1)常见的SSI:四2输入异或门74LS86,四2输入与非门74LS00,六非门74LS04,二4输入与非门74LS20,四2输入或非门74LS02,四2输入与门74LS08等。

(2)常见的MSI:二2-4译码器74LS139,3-8译码74LS138,4-16译码器74LS154,8-3线优先编码器74LS148,七段字符译码器74LS248,四位全加器74LS283,四2选1数据选择器74LS157,双4选1数据选择器74LS153,8选1数据选择器74LS151,16选1数据选择器74LS150等。

四、实验内容(一)基本命题1.设计一个多输出的逻辑网络,它的输入是8421BCD码,它的输出定义为:(1)F1:检测到输入数字能被3整除。

(2)F2:检测到输入数字大于或等于4。

(3)F3:检测到输入数字小于7。

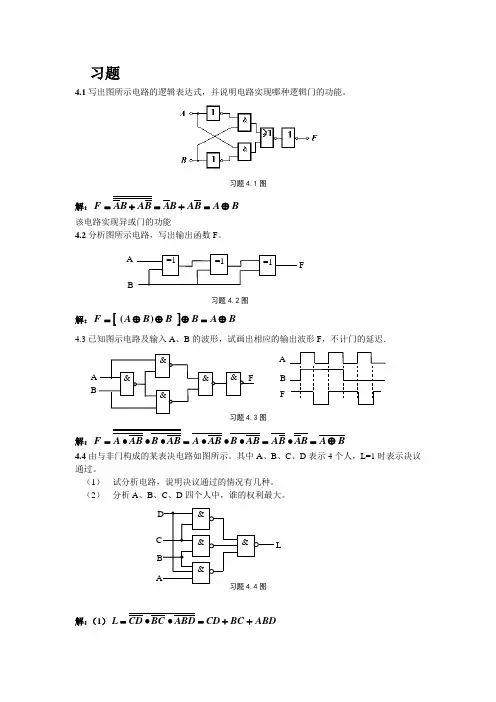

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=∙=∙∙∙=∙∙∙=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

解:(1)ABD BC CD ABD BC CD L ++=∙∙=L B A=1=1=1FFB A(2)(3)根据真值表可知,四个人当中C 的权利最大。

4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕∙⊕= (2)(3)当S 1S 0=00和S 1S 0=11时,该电路实现两输入或门,当S 1S 0=01时,该电路实现两输入或非门,当S 1S 0=10时,该电路实现两输入与非门。

4.6习题4.6图10解:(1)ABC C B A F )(++= (2)电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图 解:(1)根据波形图得到真值表:(2)由真值表得到逻辑表达式为 C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。