第三章中规模组合逻辑器件

- 格式:ppt

- 大小:2.37 MB

- 文档页数:83

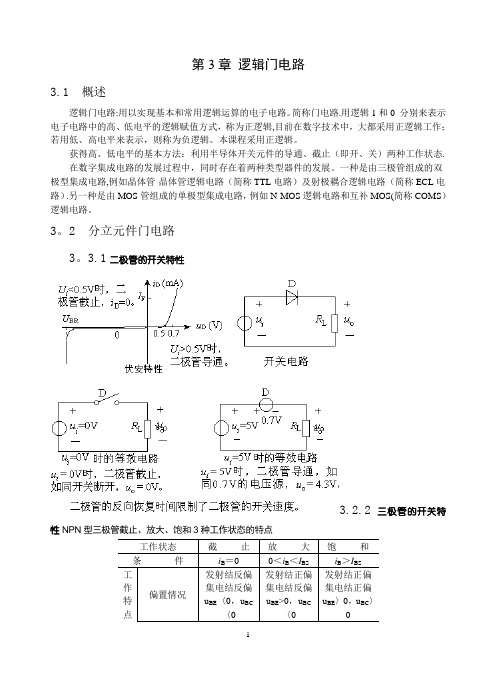

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

《数字电子技术》课程教学大纲课程名称:数字电子技术英文名称:Digital Electronic Technology 课程代码: 课程类别: 必修专业基础学分: 2 学时: 32开课单位: 计算机科学与信息工程学院适用专业: 物联网工程制订人:谭晓东审核人:黄华升审定人: 陶程仁一、课程的性质和目的(一)课程性质本课程是计算机与技术、物联网工程等本科专业的必修专业基础课。

且为主干课程。

本课程主要讲述数字逻辑的基本概念、基本定律和基本分析方法,数字逻辑电路的特性、功能,分析方法及应用。

(二)课程目的课程教学所要达到的目的是:1.能正确理解本课程的基本概念、基本理论;2.掌握数字电路的工作原理、性能和特点;3.掌握数字电路的基本分析方法和设计方法;4.能独立的应用所学的知识去分析和求解从工程中抽象出的逻辑问题以及与专业有关的某些数字电路的实际问题,并具有工程计算和分析能力,为后续专业课程的学习打下基础。

二、与相关课程的联系与分工要求学生具备高等数学、大学物理、电路理论、半导体器件等方面的知识,才能进入该课程的学习,该课程为后续电子计算机及接口技术等方面的课程及专业课程中的电子电路实际应用奠定基础。

三、教学内容及要求第一章数制与代码本章是学习数字逻辑电路及其工作原理的基础,应掌握各种数制、代码的特点及相互之间的转换规律。

1.1 进位计数制1.1.1进位计数制的基本概念1.1.2 常用进位计数制1.2 数制转化1.2.1 非十进制转化成十进制数1.2.2 十进制数转化成其它进制数1.2.3 二进制数转化成八进制数或十六进制数1.2.4 八进制数或十六进制数转化成二进制数1.3 常用代码1.3.1 二—十进制码(BCD码)1.3.2 可靠性编码1.3.3 字符代码【重点与难点】本章主要讲述简单的逻辑运算及常用的逻辑门。

重点是熟练掌握基本逻辑运算、各种门电路的图形符号及其输出函数表达式,正确处理各种门电路使用中的实际问题。

组合逻辑电路是数字电路中的一种重要类型,主要用于实现逻辑运算和计算功能。

其中,半加器和全加器是组合逻辑电路的两种基本结构,通过它们可以实现数字加法运算。

本文将详细介绍组合逻辑电路的相关知识,包括半加器、全加器以及逻辑运算的原理和应用。

一、半加器半加器是一种简单的数字电路,用于对两个输入进行加法运算,并输出其和及进位。

其结构由两个输入端(A、B)、两个输出端(S、C)组成,其中S表示和,C表示进位。

半加器的真值表如下:A B S C0 0 0 00 1 1 01 0 1 01 1 0 1从真值表可以看出,半加器只能实现单位加法运算,并不能处理进位的问题。

当需要进行多位数的加法运算时,就需要使用全加器来实现。

二、全加器全加器是用于多位数加法运算的重要逻辑电路,它能够处理两个输入以及上一位的进位,并输出本位的和以及进位。

全加器由三个输入端(A、B、Cin)和两个输出端(S、Cout)组成,其中Cin表示上一位的进位,S表示和,Cout表示进位。

全加器的真值表如下:A B Cin S Cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1通过全加器的应用,可以实现多位数的加法运算,并能够处理进位的问题,是数字电路中的重要组成部分。

三、逻辑运算除了实现加法运算外,组合逻辑电路还可用于实现逻辑运算,包括与、或、非、异或等运算。

这些逻辑运算能够帮助数字电路实现复杂的逻辑功能,例如比较、判断、选择等。

逻辑运算的应用十分广泛,不仅在计算机系统中大量使用,而且在通信、控制、测量等领域也有着重要的作用。

四、组合逻辑电路的应用组合逻辑电路在数字电路中有着广泛的应用,其不仅可以实现加法运算和逻辑运算,还可以用于构建各种数字系统,包括计数器、时序逻辑电路、状态机、多媒体处理器等。

组合逻辑电路还在通信、控制、仪器仪表等领域得到了广泛的应用,为现代科技的发展提供了重要支持。

《数字电路与逻辑设计》课程教学大纲第一篇:《数字电路与逻辑设计》课程教学大纲《数字电路与逻辑设计》课程教学大纲先修课程:高等数学、普通物理、电路与电子学(一)课程地位、性质和任务《数字电路与逻辑设计》是计算机科学与技术专业的主干课程,是一门专业技术基础课。

它不仅为《计算机组成原理与汇编程序设计》、《微机接口技术》、《计算机系统结构》、《数据通信与计算机网络》等后续课程提供必要的基础知识,而且是一门理论与实践结合密切的硬件基础课程。

(二)课程教学基本要求本课程是计算机科学与技术专业的一门专业基础课程,通过本课程的学习,使学生熟悉数字电路的基础理论知识,理解基本数字逻辑电路的工作原理,掌握数字逻辑电路的基本分析和设计方法,具有应用数字逻辑电路,初步解决数字逻辑问题的能力,为学习计算机硬件打下扎实的基础。

(三)课程主要内容及学时分配第一章逻辑代数基础逻辑代数是分析和设计数字电路的数学工具,本章主要介绍逻辑代数的公式、定理及逻辑函数的化简方法,要求掌握常用进制及其转换,基本和常用逻辑运算,逻辑代数的公式、定理,逻辑函数的公式、图形化简化,逻辑函数的五种表示方法及相互之间的转换。

教学重点:逻辑代数的公式、定理,逻辑函数的公式、图形化简法。

教学难点:公式、定理、规则的正确应用,逻辑函数化简的准确性。

方法提示:通过多举例子,多做练习以提高对公式应用的熟练性。

第二章逻辑门电路集成逻辑门是构成数字电路的基本单元,本章主要介绍MOS和TTL集成逻辑门的逻辑功能的电气特性。

要求掌握高、低电平与正、负逻辑的概念,二极管、三极管、MOS管的开关特性,熟悉二极管与门和或门,三极管非门的电路结构及工作原理,掌握其电气特性和功能。

掌握与门、或门、非门、与非门、或非门、与或非门、异或门、三态门、OC门、CMOS传输门的逻辑符号、逻辑功能,熟悉各种门电路的特点和使用方法。

教学重点:CMOS和TTL集成门电路重点是外部特性,即逻辑功能和电气特性。

*数字逻辑o第一章进位计数制o第二章、布尔代数▪第一节、“与”“或”“非”逻辑运算的基本定义▪第二节、布尔代数的基本公式及规则▪第三节、逻辑函数的代数化简法▪第四节、逻辑函数的图解化简法▪第五节、逻辑函数的列表化简法o第三章组合逻辑电路的设计▪第一节、常用门电路▪第二节、半加器和全加器的分析▪第三节译码器的分析▪第四节、其它常用电路分析o第四章组合逻辑函数的设计▪第一节、采用门电路实现组合逻辑电路的设计▪第二节、转化成“与非”“或非”“与或非”形式▪第三节、组合电路设计中几个问题的考虑▪第四节、组合逻辑电路设计举例o第五章大规模集成电路▪第一节、由中规模器件构成的组合逻辑电路▪第二节、由中规模器件构成的组合逻辑电路设计▪第三节、采用只读存贮器实现组合逻辑电路设计▪第四节、组合逻辑电路中的竞争与险象*o第六章时序电路的分析▪第一节、同步时序电路▪第二节、触发器的逻辑符号及外部特性▪第三节、时序电路的状态表和状态图▪第四节、同步时序电路的分析方法o第七章同步时序电路的设计▪第一节、概述▪第二节、形成原始状态表的方法▪第三节、状态化简▪第四节、同步时序电路设计举例▪第五节、状态编码*o第八章异步时序电路的分析和设计▪第一节、脉冲异步电路的分析和设计▪第二节、电平异步电路概述▪第三节、电平异步电路分析▪第四节、电平异步电路的设计▪第五节、时序电路中的竞争与险象*o第九章数字逻辑计算机辅助设计方法▪3 / 205 / 207 / 209 / 2011 / 20A. B. C. D. 参考答案:D13 / 2015 / 2017 / 20。

组合逻辑电路基本概念复习题填空1.消除或减弱组合电路中的竞争冒险,常用的方法是发现并消掉互补变量,增加__________,并在输出端并联 。

冗余项、电容器2.要扩展得到1个16-4线编码器,需要 片74LS148。

23.在组合逻辑电路中,当一个输入信号经过多条路径传递后到达某一逻辑门的输入端时,会有时间先后,这一现象称为_________,由此而产生输出干扰脉冲的现象称为 。

竞争、冒险4.所谓组合逻辑电路是指:在任何时刻,逻辑电路的输出状态只取决于电路各 的组合,而与电路的 无关。

输入状态、原来的状态5.组合逻辑电路由逻辑门电路组成,不包含任何 ,没有 能力。

记忆元件、记忆6.常见的中规模组合逻辑器件有 和 等。

编码器、译码器、数据选择器、数值比较器、加法器任选二个。

7.加法器是一种最基本的算术运算电路,其中的半加器是只考虑本位两个二进制数进行相加不考虑 的加法器。

低位向本位的进位8.全半加器既要考虑本位两个二进制数进行相加,还要考虑 的加法器。

低位向本位的进位9.用全加器组成多位二进制数加法器时,加法器的进位方式通常有、 、 2种。

串行进位、并行进位10.基本译码器电路除了完成译码功能外,还能实现 和 功能。

逻辑函数发生、多路分配11.多路分配器可以直接用 来实现。

译码器12.与4位串行进位加法器比较,使用超前进位全加器的目的是 。

提高运算速度13.在分析门电路组成的组合逻辑电路时,一般需要先根据 写出逻辑表达式。

逻辑电路图14.数据选择器的功能相当于多个输入的数据数据开关,是指经过选择,把 通道的数据传送到 的公共数据通道上去。

多个、唯一15.数据分配器的功能相当于一个多输出的数据开关,是将 数据源来的数据根据需要,送到 不同的通道上去。

经过选择,把通道的数据传送到的公共数据通道上去。

一个、多个16.加法器的超前进位级联方式,高位的运算不必等低位运算的结果,故提高了 ,但结构比较 。

实验四组合逻辑电路实验分析一、实验目的1.掌握组合逻辑电路的分析方法与测试方法;2.了解组合电路的冒险现象及消除方法;3.验证半加器、全加器的逻辑功能。

二、预习要求1.复习组合逻辑电路的分析方法;2.复习用与非门和异或门等构成的半加器、全加器的工作原理;3.复习组合电路冒险现象(险象)的种类、产生原因,如何消除?三、实验原理1.组合逻辑电路由很多常用的门电路组合在一起,实现某种功能的电路,它在任意时刻的输出,仅取决于该时刻输入信号的逻辑取值,而与信号作用前电路原来的状态无关。

2.组合逻辑电路的分析是指根据所给的逻辑电路,写出其输入与输出之间的逻辑函数表达式或真值表,从而确定该电路的逻辑功能。

其分析步骤为:3.组合电路的冒险现象(1)实际情况下,由于器件的延时效应,在一个组合电路中,输入信号发生变化时,输出出现瞬时错误的现象,把这现象叫做组合电路中的冒险现象,简称险象。

这里研究静态险象,即电路达到稳定时,出现的险象。

可分为0型静态险象(如图4-1)和1型静态险象(如图4-2):图4-1 0型静态险象其输出函数Y=A+A,在电路达到稳定时,即静态时,输出Y总是1。

然而在输入A变化时,输出Y的某些瞬间会出现0,Y出现窄脉冲,存在有静态0型险象。

图4-2 1型静态险象其输出函数Y=A+A,在电路达到稳定时,即静态时,输出Y总是O。

然而在输入A变化时,在输出Y的某些瞬间会出现1,Y出现窄脉冲,存在有静态1型险象。

(2)进一步研究得知,对于任何复杂的组合逻辑电路,只要能成为A+A或A A的形式,必然存在险象。

为了消除险象,通常用增加校正项的方法,如果表达式中出现A+A形式的电路,校正项为被赋值各变量的“乘积项”;表达式中出现A A形式的电路,校正项为被赋值各变量的“和项”。

例如:逻辑电路的表达式为Y=A B+AC;当B=C=1时,Y=A+A,Y正常情况下,稳定后应输出1,但实际中出现了0型静态险象。

这时可以添加校正项BC,则Y A B+AC+ BC=A+A+1=1,从而消除了险象。