第二章 组合逻辑电路课后习题答案

- 格式:pdf

- 大小:637.37 KB

- 文档页数:14

《组合逻辑电路》练习题及答案[3.1]分析图P3.1电路的逻辑功能,写出Y1、、Y2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]、Z=0A、1时A3.3所示。

P3.4所示。

M S单独工点时M L和要求电路真值表中的C A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到:C B A M S +=, B M L =(M S 、M L的1状态表示工作,0状态表示停止)。

逻辑图如图A3.4(b)。

[3.5] 设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解] 题3.5的真值表如表A3.5所示。

D 4、D 3与足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图P3.7所示,其功能表如表P3.7所示。

表 P3.7 74LS148的功能表A 、B 、C 、L 1、0为0000~2)工作,P3.10输 入21O 123用外加与非门实现之,如图A3.10所示。

[3.11] 画出用4线-16线译码器74LS154(参见题3.9)和门电路产生如下多输出逻辑函数的逻辑图。

[解]电路图如图A3.11所示。

[3.12] 用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差及向高位的借位信号。

[解] 设a i 为被减数,b i 为减数,c i-1为来自低位的借位,首先列出全减器真值表,然后将Di ,Ci 表达式写成非-与非形式。

最后外加与非门[3.13] 74LS153[解] [3.14]如表P3.14 [解][3.15][解] [3.16] [解] 与4选1[3.17][解] 则 D =41507632 如图A3.17所示。

[3.18] 用8选1数据选择器CC4512(参见题3.14)产生逻辑函数[解] 将Y 变换成最小项之和形式。

第二章组合逻辑1.分析图中所示的逻辑电路,写出表达式并进行化简A BFF = AB + B = ABA B CFF = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC2.分析下图所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明F 与A、B 的关系。

F1=10S B BS A ++F2=32SB A ABS +F=F 1F 2=1SB BS A ++A 0 0 AB A B 00 11 01 1F 1S 1 S 010 0A+B A+B A0 11 01 1F 2S 3 S 2F 0 0 ××1F 1F 1F 10 1 ××1 0 ××1 1 ××F=F 1F 2S 3 S 2 S 1 S 0A ××0 0 A B A B 0××0 1×× 1 0×× 1 1F=F 1F 2S 3 S 2 S 1 S 03.分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解:F1=C B BC A C AB C B A +++=ABCC B A ABC C B A C B A +⊕=++)(真值表如下:当B ≠C 时,F1=A 当B=C=1时,F1=A 当B=C=0时,F1=0裁判判决电路,A 为主裁判,在A 同意的前提下,只要有一位副裁判(B ,C )同意,成绩就有效。

F2=AC BC AB C A C B B A ++=++真值表如下:当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2=1。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=1514131211109876543210A A A A A A A A A A A A A A A A +++只有当变量A0~A15全为0时,F =1;否则,F =0。

习题 2组合逻辑电路基础数字电子技术[题2.1] 什么是逻辑种类?一个数字电子系统中必须用同一逻辑种类的器件吗?答:具有相同的基本门电路,以及相同的构造技术、设计方法及生产工艺等统称为一个逻辑种类。

不同逻辑种类的器件由于它们可能采用不同的电源电压,或采用不同的输出电平,因此相互之间不能随意连接,所以一个数字系统中一般只用同一逻辑种类的器件。

[题2.2] 什么是图腾柱输出?它是如何产生高、低电平的?答:图腾柱输出即输入端无论是何种情况,输出端与地相连的工作管和与电源相连的负载管总有一个导通,另外一个截止,输出级的这种电路结构称为推拉式结构,也称图腾柱结构。

在图腾柱输出电路中,当工作管截止,负载管导通时,输出端对电源通路对地开路,输出高电平;当工作管饱和,负载管截止时,输出端对电源开路对地短路,输出低电平。

[题2.3] 电平信号从前级传递到后级,电流是如何流动的?答:在图腾柱输出电路中,当工作管截止,负载管导通时,输出端对电源通路对地开路,输出高电平,电流自电源经集电极电阻、负载管等从输出端流出。

当工作管饱和,负载管截止时,输出端对电源开路对地短路,输出低电平,电流自外部流入输出端,经工作管到地。

即,输出端输出高电平时供给电流,输出低电平时吸收电流。

[题2.4] 什么是OC输出?它有什么用途?答:当电路输出高电平时,输出电流流经图腾柱上的电阻使电阻发热,而半导体器件对温度比较敏感,所以为了保证正常的逻辑功能,高电平输出电流不能太大,这样就将发热的电阻移到芯片外部,即将图腾柱输出的上半部分去掉,只保留工作管,显然,工作管集电极是开路的。

这种输出称为集电极开路输出(即OC输出)。

因为导致发热的电阻在外部,因此OC输出能提供较大的高电平驱动电流。

另外,多个OC门可以共用一个输出上拉电阻,在逻辑上实现“线与”功能。

[题2.5] 什么是3S输出?它有什么用途?答:3S输出即三态输出,也即输出除了低电平状态和高电平状态外,还有第三种状态—高阻态。

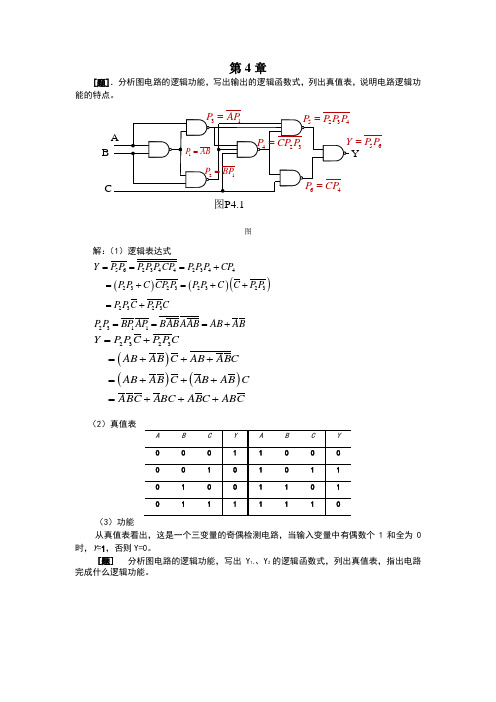

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

2.1题(陈兴)求序列{ 0,1,8,27,3n }的母函数。

解:由序列可得到32333()23n G x x x x n x =+++++因为23111n x x x x x =++++++- 2311()'12341n x x x nx x-=++++++-设 2311()()'23(1)1n np x x x x x n x nx x-==++++-+-2222221[()]'123(1)n n p x x x x n x n x --=+++++-+设 2223212()[()]'23(1)n nq x x p x x x x n x n x -==++++-+3323231[()]'123(1)n n q x x x n x n x --=++++-+ 3233313[()]'23(1)n n x q x x x x n x n x -=+++-+ 由以上推理可知[()]'x q x =,[7*94*(6)],n n +-所以可通过求得[()]'x q x 得到序列的母函数:32()4G x x x x =++2321()()[34(3)]6n H x F x dx x x n x +==++++⎰2.2题(陈兴)已知序列343,,,,333n ⎧+⎛⎫⎛⎫⎛⎫⎫⎨⎬ ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭⎭⎩,求母函数 解: 3*2*14*3*2(3)*(2)*(1)()3*2*13*2*13*2*1nn n n G x x +++=+++=1[3.2.1 4.3.2(3)(2)(1)]6n x n n n x ++++++211()()[3.2 4.3(3)(2)]6n F x G x dx x x n n x +==+++++⎰ 2321()()[34(3)]6n H x F x dx x x n x +==++++⎰3431()()[]6n I x H x dx x X x ++==++⎰因为23111n x x x x+=+++++-所以211()(1)61I x x x x=----所以31()[]'''61x G x x=-就是所求序列的母函数。

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比拟器,输入信号为两个要比拟的一位二进制数,用A 、B 表示,输出信号为比拟结果:Y (A >B ) 、Y (A =B )和Y (A <B ),那么Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

〔√,× 〕 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未到达最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的根本电路结构形式。

3 33习 题1.解: CO =AB +BC +ACAC BC AB C B A ABC CO C B A ABC S +++++=+++=)()(AC BC AB C B A ABC )(+++=AC BC AB C AC BC AB B AC BC AB A ABC +++= A B AB C AC C A B C BC B A ABC +++= C B A C B A C B A ABC +++=真值表A B C S CO A B C S CO 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 011111111电路功能:一位全加器,A 、B 为两个加数,C 为来自低位的进位,S 是相加的和,CO 是进位。

2.解:处于工作状态的译码器C 、D 应输入的状态C D ① 0 0 ② 0 1 ③ 1 0 ④11逻辑功能:由74LS139构成的4线—16线译码器3.解:由图可见,74HC138的功能扩展输入端必须满足E 1=1、032==E E 才能正常译码,因此E 1=A 3=1;542A A E =,即A 4=1,A 5=1; 0763=+=A A E ,即A 6=0,A 7=0。

所以,该地址译码器的译码地址范围为A 7A 6A 5A 4A 3A 2A 1A 0=00111A 2A 1A 0=00111000~3 3400111111,用十六进制表示即为38H ~3FH 。

输入、输出真值表如表P3.3-1所示。

表3.3-1 地址译码器的真值表4.解:由图写出逻辑函数并化简,得02460246L Y Y Y Y Y Y Y Y A BC ABC ABC ABC C ==+++=+++=5. 解:F AB B C A B C AB C ABC ABC =+=+++3 359.解:4选1数据选择器的逻辑表达式为: 301201101001D A A D A A D A A D A A Y +++=将A 1=A ,A 0=B ,D 0=1,D 1=C ,C D =2,D 3=C 代入得 ABC C B A BC A C B A C B A ABC C B A BC A B A Y ++++=+++=根据表达式可画出波形图:C ABL10.解:(1)写出逻辑函数表达式: C AB C B A BC A C B A C B A L ++++=(2)用卡诺图化简3 3611.解:567m m m ABC C B A ABC C AB AC AB L ++=+++=+=13. 解:D C B D C D D C A D C B D C C A F +++=++=)(0⋅+++=+++=CD D C D C A D C AB D C B D C D C A D C A令A 1=C ,A 0=D ,AB D =0,A D =1,D 2=1,D 3=0 连线图:14. 解:3 371。

第二章组合逻辑1.分析图中所示的逻辑电路,写出表达式并进行化简A BFF = AB + B = ABA B CFF = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC2.分析下图所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明F 与A、B 的关系。

F1=10S B BS A ++F2=32SB A ABS +F=F 1F 2=1SB BS A ++A 0 0 AB A B 00 11 01 1F 1S 1 S 010 0A+B A+B A0 11 01 1F 2S 3 S 2F 0 0 ××1F 1F 1F 10 1 ××1 0 ××1 1 ××F=F 1F 2S 3 S 2 S 1 S 0A ××0 0 A B A B 0××0 1×× 1 0×× 1 1F=F 1F 2S 3 S 2 S 1 S 03.分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解:F1=C B BC A C AB C B A +++=ABCC B A ABC C B A C B A +⊕=++)(真值表如下:当B ≠C 时,F1=A 当B=C=1时,F1=A 当B=C=0时,F1=0裁判判决电路,A 为主裁判,在A 同意的前提下,只要有一位副裁判(B ,C )同意,成绩就有效。

F2=AC BC AB C A C B B A ++=++真值表如下:当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2=1。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=1514131211109876543210A A A A A A A A A A A A A A A A +++只有当变量A0~A15全为0时,F =1;否则,F =0。

因此,电路的功能是判断变量是否全部为逻辑“0”。

5.分析下图所示逻辑电路,列出真值表,说明其逻辑功能解:301201101001X A A X A A X A A X A A F +++=真值表如下:F A X 0 X 1X 2X 30 00 11 01 11 A 0因此,这是一个四选一的选择器。

6.下图所示为两种十进制数代码转换器,输入为余三码,输出为什么代码?解:W= AB+ACD X = BC+BD+BCD Y = CD+CD Z = DW X Y Z A B C D 0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 10 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 0这是一个余三码至8421BCD 码转换的电路7.下图是一个受M 控制的4位二进制码和格雷码的相互转换电路。

M=1时,完成自然二进制码至格雷码转换;M=0时,完成相反转换。

请说明之解:Y3=X3322X X Y ⊕=)22(11Y M MX X Y +⊕=)11(00Y M MX X Y +⊕=当M=1时Y3=X3Y2=X2⊕X3Y1=X1⊕X2Y0=X0⊕X1当M=0时Y3=X3Y2=X2⊕X3Y1=X1⊕Y2=X1⊕X2⊕X3Y0=X0⊕Y1=X0⊕X1⊕X2⊕X3Y X 0 0 0 00 0 0 10 0 1 10 0 1 00 1 1 00 1 1 10 1 0 10 1 0 01 1 0 01 1 0 11 1 1 11 1 1 01 0 1 01 0 1 11 0 0 11 0 0 00 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 13Y 2Y 1Y 03X 2X 1X 0M= 1 的真值表Y X 0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10 0 0 00 0 0 10 0 1 10 0 1 00 1 1 00 1 1 10 1 0 10 1 0 01 1 0 01 1 0 11 1 1 11 1 1 01 0 1 01 0 1 11 0 0 11 0 0 03Y 2Y 1Y 03X 2X 1X 0M= 0 的真值表由真值表可知:M=1时,完成8421BCD 码到格雷码的转换;M=0时,完成格雷码到8421BCD 码的转换。

8.已知输入信号A,B,C,D 的波形如下图所示,选择适当的集成逻辑门电路,设计产生输出F 波形的组合电路(输入无反变量)解:列出真值表如下:F A B C D 01011100111110000 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1AB111111111CD 00 01 11 1000011110)(D C A C B A D C B D B B A F 或+++=9.用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示有两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,并选出合适的集成电路来实现。

解:设:三台设备分别为A 、B 、C :“1”表示有故障,“0”表示无故障;红、黄、绿灯分别为Y1、Y2、Y3:“1”表示灯亮;“0”表示灯灭。

据题意列出真值表如下:Y A B C 0 0 11 0 01 0 00 1 01 0 00 1 00 1 01 1 00 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1 1 Y 2 Y 3于是得:CB AC B A Y C B A BC Y CB A Y ++==⊕+=⊕⊕=3)(2110.用两片双四选一数据选择器和与非门实现循环码至8421BCD 码转换。

解:(1)画函数卡诺图;0110010101000011ΦΦΦ0010ΦΦΦ00010111100010010000ABCD0001 11 1000011110(2)写逻辑函数表达式:(1)画逻辑图:A A 1 A0EN ENY 1123WB DY 20123XSTCC MUX EN A 1 AEN C Y 10123YA BY 20123ZSTDMUXC D DD C C 11.用一片74LS148和与非门实现8421BCD 优先编码器Y 001234567ENY 08:3优先编码器Y 1Y 2STI 0I 1I 2I 3I 4I 5I 6I 7I 8I 9Y 1Y 2Y 312.用适当门电路,设计16位串行加法器,要求进位琏速度最快,计算一次加法时间。

解:全加器真值表如下Ai Bi Ci-1Si Ci+10000000110010100110110010101011100111111可以写出以下表达式要使进位琏速度最快,应使用“与或非”门。

具体连接图如下。

若“与或非”门延迟时间为t1,“非门”延迟时间为t2,则完成一次16位加法运算所需时间为:CAB C B A BC A C B A S +++=CAB C B A BC A C B A S +++=11--+=C B C A B A C +11--+=C B C A B A C +11--+=BC AC AB C +11--+=BC AC AB C +)()116(211t t t t ++-=13.用一片4:16线译码器将8421BCD 码转换成余三码,写出表达式解:001100000010001010110011110001001101010111100000100100011010001010110011110001001123456789余三码8421码十进制数)8,6,4,2,0(),,,()8,7,4,3,0(),,,()9,4,3,2,1(),,,()9,8,7,6,5(),,,(∑=∑=∑=∑=D C B A Z D C B A Y D C B A X D C B A WW(A,B,C,D) = Σ(5,6,7,8,9) = Y 5+Y 6+Y 7+Y 8+Y 9= Y 5Y 6Y 7Y 8Y 9X(A,B,C,D) = Σ(1,2,3,4,9) = Y 1+Y 2+Y 3+Y 4+Y 9= Y 1Y 2Y 3Y 4Y 9Y(A,B,C,D) = Σ(0,3,4,7,8) = Y 0+Y 3+Y 4+Y 7+Y 8= Y 0Y 3Y 4Y 7Y 8Z(A,B,C,D) = Σ(0,2,4,6,8) = Y 0+Y 2+Y 4+Y 6+Y 8= Y 0Y 2Y 4Y 6Y 8A 0A 1A 2A 3Y 0Y 1D C B AY 15Y 0Y 15G 1G 2A G 2BY 1. . .. . .4:16线译码器WY 5Y 6Y 7Y 8Y 9X Y 1Y 2Y 3Y 4Y 9Y Y 0Y 3Y 4Y 7Y 8Z Y 0Y 2Y 4Y 6Y 814.使用一个4位二进制加法器设计8421BCD 码转换成余三码转换器:解:A 00B 174LS2830A 1A 2A 3S 0S 1S 2S 3123C O 123C OC I0B 1B 2B 3ΣC I S 0S 1S 2S 38421BCD 码100余三码15.用74LS283加法器和逻辑门设计实现一位8421BCD 码加法器电路。

解:加6判断修正进位和BCD 码加数1(BCD )加数2(BCD )+16.设计二进制码/格雷码转换器解:真值表0 0 0 0 00 0 0 10 0 1 10 0 1 00 1 1 00 1 1 10 1 0 10 1 0 01 1 0 01 1 0 11 1 1 11 1 1 01 0 1 01 0 1 11 0 0 11 0 0 00 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1G 3G 2G 1G 0B 3B 2B 1B 01111100101010011111010000100001011011011011100011100101001100000B 3B 2B 1B 000 0111 1000011110得:10021132233B B G B B G B B G B G ⊕=⊕=⊕==B 0B 1B 2B 3G 0G 1G 2G 3EN17.设计七段译码器的内部电路,用于驱动共阴极数码管。