数电第二章习题教学内容

- 格式:doc

- 大小:3.09 MB

- 文档页数:15

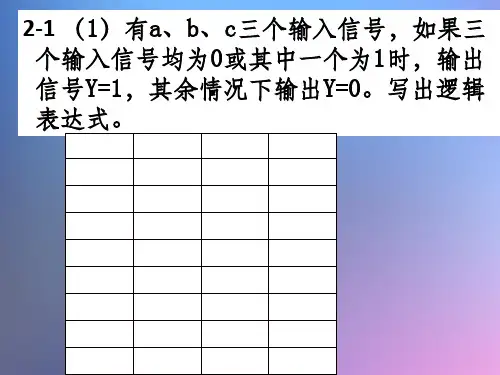

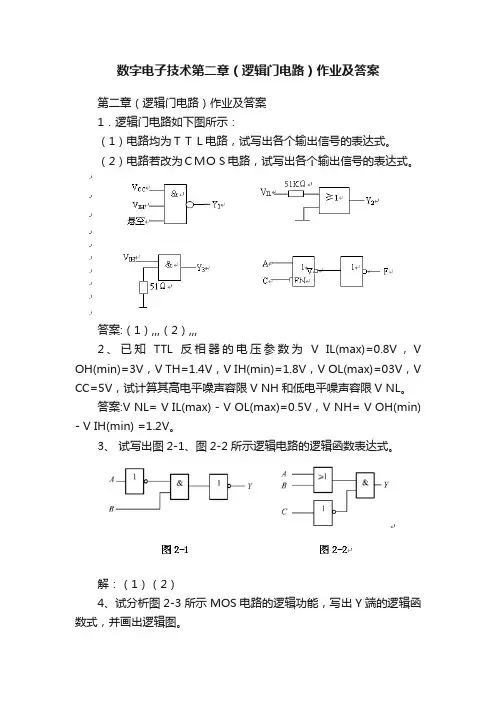

数字电子技术第二章(逻辑门电路)作业及答案第二章(逻辑门电路)作业及答案1.逻辑门电路如下图所示:(1)电路均为TTL电路,试写出各个输出信号的表达式。

(2)电路若改为CMOS电路,试写出各个输出信号的表达式。

答案:(1),,,(2),,,2、已知TTL反相器的电压参数为V IL(max)=0.8V,V OH(min)=3V,V TH=1.4V,V IH(min)=1.8V,V OL(max)=03V,V CC=5V,试计算其高电平噪声容限V NH和低电平噪声容限V NL。

答案:V NL= V IL(max) - V OL(max)=0.5V,V NH= V OH(min) - V IH(min) =1.2V。

3、试写出图2-1、图2-2所示逻辑电路的逻辑函数表达式。

解:(1)(2)4、试分析图2-3所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

5、试简要回答下列问题。

(1)有源(图腾柱)输出与集电极开路(OC)输出之间有什么区别?解:OC门输出端只能输出低电平和开路状态,其输出级需要上拉电阻才能输出高电平,且上拉电源可以与芯片电源不同,因此常用于不同电源电压芯片之间实现信号电平变换,OC门输出端可以并联实现线与;有源输出可以输出低电平与高电平,两个有源输出端连接在一起时,若是一个输出端输出高电平,另外一个输出端输出低电平时,可引起较大电流损坏输出级。

(2)TTL逻辑电路输入端悬空时,可视为输入高电平信号处理,而CMOS逻辑电路输入端则不允许悬空使用,试说明其原因。

解:因为CMOS电路的输入端具有非常高的输入阻抗,容易受到干扰,一旦受到干扰后,会使输出电平发生转换,产生功耗,因此输入端不能悬空,应该连接确定的逻辑电平。

6.请查阅74LS00芯片手册(常规温度范围的),回答如下问题:(1)电源电压范围;(2)输出高电平电压范围;(3)输出低电平电压范围;(4)输入高电平电压范围;(5)输入低电平电压范围;(6)该芯片的电源电流;(7)典型传播延迟时间;(8)扇出系数。

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

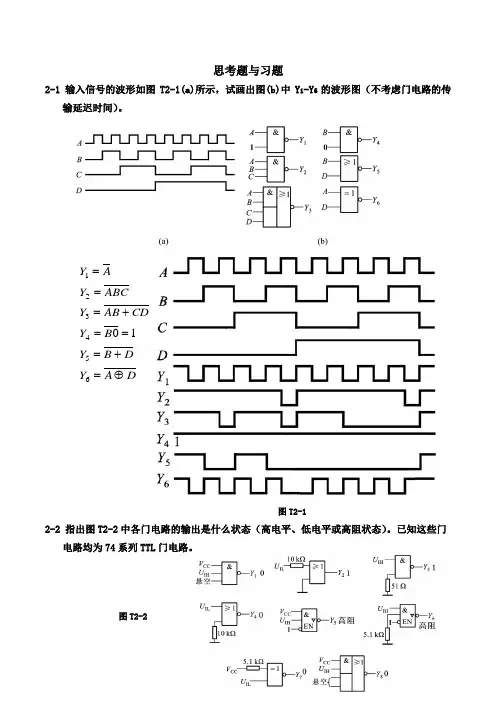

思考题与习题2-1 输入信号的波形如图T2-1(a)所示,试画出图(b)中Y 1-Y 6的波形图(不考虑门电路的传 输延迟时间)。

DA Y DB Y B Y CDAB Y ABCY AY ⊕=+===+===6543211图T2-1 2-2 指出图T2-2中各门电路的输出是什么状态(高电平、低电平或高阻状态)。

已知这些门电路均为74系列TTL 门电路。

图T2-2011110010101011010111874321=⋅+⋅==⊕==+==⋅==+==⋅⋅=Y Y Y Y Y Y Y 5为高阻,Y 6为高阻。

2-3试说明在下列情况下,用内阻为20k Ω/V 的三用表的5V 量程去测量如图T2-3所示的74 系列与非门U I2端的电压应为多少: (1)U I1悬空;U I2=1.4 V (2)U I1接0V ;U I2=0 V (3)U I1接3V ;U I2=1.4 V (4)U I1接5.1Ω电阻到地;U I2=0 V(5) U I1接10k Ω电阻到地。

U I2=1.4 V图T2-3图T2-32-4试说明下列各种门电路中,哪些可以将输出端并联使用(输入端的状态不一定相同 )。

(1) 具有推拉式输出级的电路;×(2) TTL 的OC 门;√线与(3) TTL 的三态门;√总线应用(4) 普通的CMOS 门;×(5) CMOS 三态门。

√2-5 CMOS 门电路不宜将输入端悬空使用,请说明原因。

CMOS 门电路输入阻抗高,很容易受到干扰,并且CMOS 电路为场效应管,是电压控制电流器件,悬空时容易出现静电等瞬时高压烧毁器件的现象,因此输入端不宜悬空,必须根据 实际情况做相应的处理。

2-6 请对应于输入波形画出图T2-6所示电路在下列两种情况下的输出波形:(1)忽略所有门的传输延迟时间;(2)考虑每个门都有传输延迟时间t pd 。

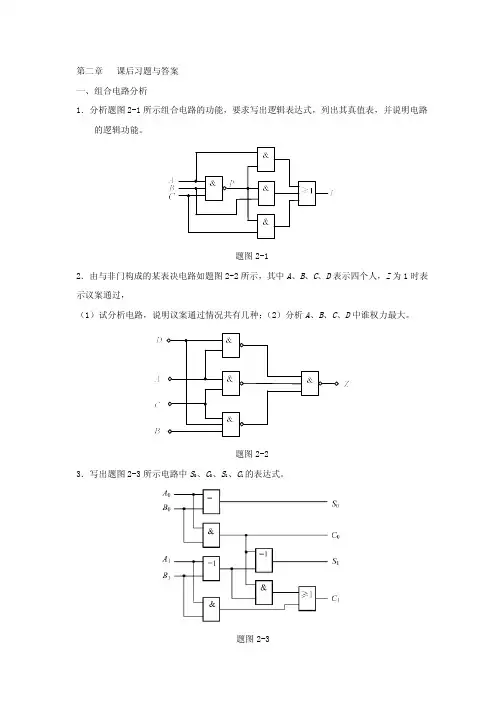

图T2-62-7 电路如图T2-7所示,试分别列出电路的功能真值表以及输出端F 1和F 2的逻辑表达式, 并说明电路实现的逻辑功能。

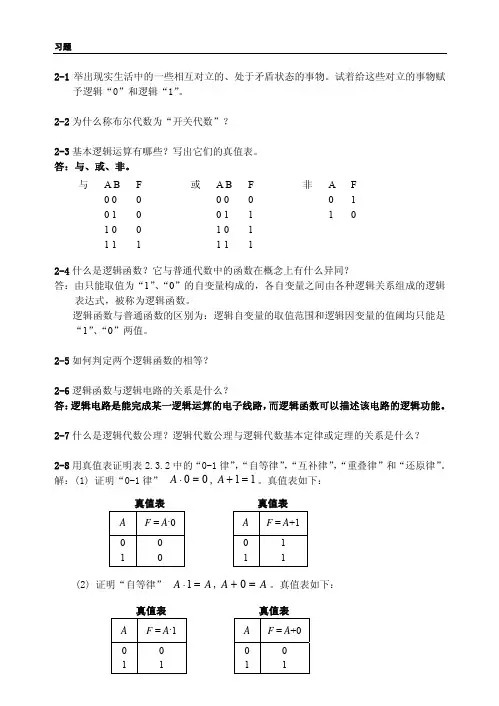

教案注:教师讲稿附后第2章逻辑代数和函数化简教学重点:1.逻辑代数的特殊定理;2.逻辑函数的表示方法及其之间的相互转换;3.逻辑表达式的化简方法。

教学难点:1.逻辑运算基本概念;2.逻辑表达式的图形化简方法。

2-1基本逻辑运算和复合逻辑运算一、基本逻辑运算1.与逻辑(1)逻辑含义:当决定事件成立的所有条件全部具备时,事件才会发生。

(2)电路举例(3)真值表(4)表达式F=A•B运算规则:0•0=0,0•1=0,1•1=1A•0=0(0-1律),A•1=A(自等律),A•A=A(同一律),A•A•A=A(同一律)。

(5)表示符号功能说明:有0出0,全1出1。

2.或逻辑(1)逻辑含义:在决定事件成立的所有条件中,只要具备一个,事件就会发生。

(2)电路举例(3)真值表(4)表达式F=A+B 运算规则:AB国家标准AB以前的符号AB欧美符号0+0=0,0+1=1,1+1=1A +0=A (自等律)A +1=1(0-1律),A +A =A (同一律)。

(5)表示符号逻辑功能:有1出1,全0出0。

3.非逻辑(1)逻辑含义:当决定事件的条件具备时,事件不发生;当条件不具备时,事件反而发生了。

(2)电路举例(3)真值表(4)表达式F =A 运算规则:A =A (还原律);A +A =1、A A =0(互补律)。

(5)逻辑符号:逻辑功能:入0出1,入1出0。

二、复合逻辑运算1.与非运算“与”和“非”的组合。

有专门实现这种运算的实际器件(如TTL 与非门等)。

逻辑符号:表达式:F =AB ;真值表:(略),逻辑功能为:有0出1,全1出0。

A B 国家标准A B 以前的符号AB 欧美符号国家标准以前的符号欧美符号A F AAA 可编程逻辑器件符号A B 国家标准A B 以前的符号A B欧美符号2.或非运算“或”和“非”的组合。

也有专门实现这种运算的实际器件(如TTL 、CMOS 与非门等)。

逻辑符号:表达式:F =BA +;真值表:(略),逻辑功能为:有1出0,全0出1。

第二章一、选择题1.下列表达式中不存在竞争冒险的有 C D 。

A.Y =B +A BB.Y =A B +B CC.Y =A B C +A BD.Y =(A +B )A D2.若在编码器中有50个编码对象,则要求输出二进制代码位数为B 位。

A.5B.6C.10D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A.1B.2C.4D.164.下列各函数等式中无冒险现象的函数式有 D 。

A.B A AC C B F ++=B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++=5.函数C B AB C A F ++=,当变量的取值为 A C D 时,将出现冒险现象。

A.B =C =1B.B =C =0C.A =1,C =0D.A =0,B =06.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有 E 个。

A.1B.2C.3D.4E.88.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A.译码器B.编码器C.全加器D.寄存器9.八路数据分配器,其地址输入端有 C 个。

A.1B.2C.3D.4E.810.组合逻辑电路消除竞争冒险的方法有 A B 。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰11.101键盘的编码器输出 C 位二进制代码。

A.2B.6C.7D.8 12.用三线-八线译码器74L S 138实现原码输出的8路数据分配器,应 A B C 。

A.A ST =1,B ST =D ,C ST =0B. A ST =1,B ST =D ,C ST =DC.A ST =1,B ST =0,C ST =DD. A ST =D ,B ST =0,C ST =013.以下电路中,加以适当辅助门电路, A B 适于实现单输出组合逻辑电路。

A.二进制译码器B.数据选择器C.数值比较器D.七段显示译码器14.用四选一数据选择器实现函数Y =0101A A A A +,应使 A 。

A.D 0=D 2=0,D 1=D 3=1B.D 0=D 2=1,D 1=D 3=0C.D 0=D 1=0,D 2=D 3=1D.D 0=D 1=1,D 2=D 3=015.用三线-八线译码器74L S 138和辅助门电路实现逻辑函数Y =122A A A +,应 B 。

A.用与非门,Y =765410Y Y Y Y Y YB.用与门,Y =32Y YC.用或门,Y =32Y Y +D.用或门,Y =765410Y Y Y Y Y Y +++++16.编码电路和译码电路中,( B )电路的输入是二进制代码A.编码B.译码C.编码和译码17.组合逻辑电路输出状态的改变( A )A.仅与该时刻输入信号的状态有关B.仅与时序电路的原状态有关C.与A 、B 皆有关18.16位输入的二进制编码器,其输出端有( C )位A. 256B. 128C. 4D. 319.对于四位二进制译码器,其相应的输出端共有( B )A.4个B. 16个C. 8个D. 10个20.在下列逻辑电路中,不是组合逻辑电路的有( D )A.译码器B.编码器C.全加器 D .寄存器22.对于输出低电平有效的2—4线译码器来说要实现,Y=A B AB ''+的功能,应外加( D) A.或门 B.与门 C.或非门 D.与非门23.两片8-3线优先编码器(74148)可扩展成( A )线优先编码器。

A. 16-4B. 10-5C. 16-8D. 10-824.两片3-8线译码器(74138)可扩展成( A )线译码器。

A. 4-16B. 5-10C. 8-16D.8-1025.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出70~Y Y ''=( C )A.11101111B.10111111C.11111101D.1111001126.对于三位二进制译码器,其相应的输出端共有( C )A.4个B. 16个C. 8个D. 10个27.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=110时,输出70~Y Y ''=( B )A.11011111B.10111111C.11111101D.1111001128.具有3条地址输入线的选择器含(B )条数据输入线。

A.4B.8C.12D.1629.八选一数据选择器74LS151的地址线为011时,输出Y=( C )A.0B.1C. 3DD. 5D30.1位半加器的输入和输出分别为(B )A. ,,A B CI 和,S COB. ,A B 和SC. ,A B 和,S CO31.半加器的求和的逻辑关系是(D )A.与非B.或非C.与或非D.异或 32.优先编码器74LS148输入为— ,输出为 、 、 。

当使能输入 , ,时,输出 应为( A )A.001B.010C.110D.01133.在下列逻辑电路中,不是组合逻辑电路的有( C )A.译码器B.数据选择器C.计数器D.数值比较器34. 能起到多路开关作用的是( C )A.编码器B.译码器C.数据选择器D.数值比较器35. 能实现对一系列高低电平编成对应的二值代码的器件是(A )A.编码器B.译码器C.加法器D.数据选择器36. 能实现将输入的二进制代码转换成对应的高低电平输出信号的是( B )A.编码器B.译码器C.数据选择器D.数值比较器38. 用3-8译码器设计的组合逻辑函数变量最大数为( B )A.2B.3C.4D.539. 用8选1数据选择器可设计的组合逻辑函数变量最大数为( C )A.2B.3C.4D.540. 用4片74148可扩展成的编码器是( D )A.8线-3线B.16线-4线C.24线-5线D.32线-5线41. 用4片74138可扩展成的译码器是( D )A.3线-8线B.4线-16线C.5线-24线D.5线-32线42. 编码电路和译码电路中,( A )电路的输出是二进制代码。

A. 编码B. 译码C. 编码和译码43. ( B )是构成组合逻辑电路的基本单元。

A. 触发器B. 门电路C. 门电路和触发器44. 下列说法错误的是( C )。

A. 74HC148的输入和输出均以低电平作为有效信号。

B. 74HC138的输出以低电平作为有效信号。

C. 7448的输出以低电平为有效信号。

45. 对于3位二进制译码器,其相应的输出端共有( B )个。

A. 3B. 8C. 6D. 1047. 两个1位二进制数A 和B 相比较,可以用( A )作为A > B 的输出信号Y (A>B )。

A. B A 'B. B A 'C. B A ⊕D. )('⊕B A48. 两个1位二进制数A 和B 相比较,可以用( B )作为A < B 的输出信号Y (A<B )。

A. B A 'B. B A 'C. B A ⊕D. )('⊕B A49. 两个1位二进制数A 和B 相比较,可以用( D )作为A = B 的输出信号Y (A=B )。

A. B A 'B. B A 'C. B A ⊕D. )('⊕B A50. 一个4选1数据选择器的地址端有( D )个。

A. 8B. 1C. 3D. 251. 在8线-3线优先编码器74HC148中,扩展端EX Y '的低电平输出信号表示( A )。

A. “电路工作,但无编码输入”B. “电路工作,而且有编码输入”52.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是(C )。

A .111 B. 010 C. 000 D. 10154.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( C ) 。

A. 11111101B. 10111111C. 11110111D. 1111111156、半加器和的输出端与输入端的逻辑关系是 (D )A 、 与非B 、或非C 、 与或非D 、异或57、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为A 2 A 1 A 0 =101 时,输出:为(B )。

A . 00100000 B. 11011111 C.11110111 D. 0000010058、属于组合逻辑电路的部件是(A )。

A 、编码器 B 、寄存器 C 、触发器 D 、计数器59.以下错误的是(B )a .数字比较器可以比较数字大小b .实现两个一位二进制数相加的电路叫全加器c .实现两个一位二进制数和来自低位的进位相加的电路叫全加器d .编码器可分为普通全加器和优先编码器二、判断题(正确打√,错误的打×)1.优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

(× )2.编码与译码是互逆的过程。

(√ )3.二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路。

(√ )4.液晶显示器的优点是功耗极小、工作电压低。

(√ )5.液晶显示器可以在完全黑暗的工作环境中使用。

(× )6.半导体数码显示器的工作电流大,约10mA 左右,因此,需要考虑电流驱动能力问题。

(√ )7.共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

(√)8.数据选择器和数据分配器的功能正好相反,互为逆过程。

(√ )9.用数据选择器可实现时序逻辑电路。

(× )10.组合逻辑电路中产生竞争冒险的主要原因是输入信号受到尖峰干扰。

(× )11.八路数据分配器的地址输入(选择控制)端有8个。

(× )12.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码. (× )13.译码器哪个输出信号有效取决于译码器的地址输入信号(√)14.组合逻辑电路在任意时刻的输出不仅与该时刻的输入有关,,还与电路原来的状态有关。

(×)15.寄存器、编码器、译存器、加法器都是组合电路逻辑部件。

(× )三、填空题1.半导体数码显示器的内部接法有两种形式:共 阴 接法和共 阳 接法。