- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

1 1 1

C

1 1

B

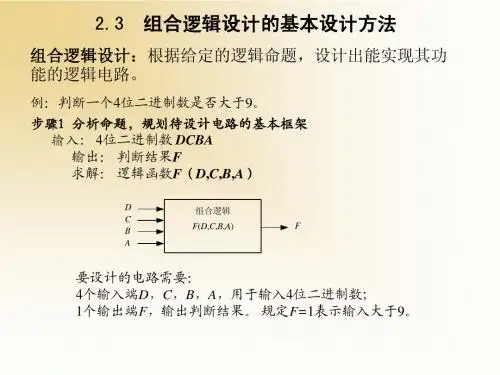

组合逻辑设计

2. 反函数三次反演,一次展开: A

1 1 1 1 1 1 1 1 F

F=ABCD+ABCD D F=ABCD+ABCD =ABCD•ABCD

ABCD ABCD

C

1 1

1 1

1 1

B

组合逻辑设计

逻辑函数的“或非”门实 现 采用“与非”门实现的对偶方法 直接采用对偶规则

数学:7 学分; 英语:5 学Βιβλιοθήκη ; 政治:4 学分; 体育:2 学分

每个学生总计要获得10个以上学分才能通过本学期 考试。要求写出反映学生是否通过本学期考试的逻 辑函数。 设 A、B、C、D 分别为四门课,“1” 表示通过此门 课通过,“0” 表示不通过;F 为“1”时表示本学期 考试通过,“0”为没通过。 A

•• •••

A

1

1 1

1

B

1 1

常用的中规模组合逻辑标准构件

当 m n 时:

例如:用八选一的数据选择器实现函数:

F =AB+AB+AB A B

0 1 1 1

B A

F

A0 多路选择器 A1 A2 D0 D1 D2 D3 D4 D5 D6 D7

•

• •

•••

Vcc

常用的中规模组合逻辑标准构件

当 m n 时: 降维图:如果把某些变量也作为卡诺图小方格内的值, 则会减少图的维数,这种图称为降维图。

考虑特殊问题的逻辑设计

例如:用与非门设计一个判别电路,以判别8421码所 表示的十进制数之值是否大于等于5

A B C D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 0 0 0 0 0 1 1 1 1 1

设:8421码对应输入变量:A,B,C,D, 输出函数为F, ABCD 0101 时,F=1; 当ABCD 0101 时,F=0

F=m(5,6,7,8,9) +(10,11,12,13,14,15)

(10,11,12,13,14,15)=0

0 1 3

C

2

81 5 13 9 1 1 D 7 15 11 1 6 14 10 1

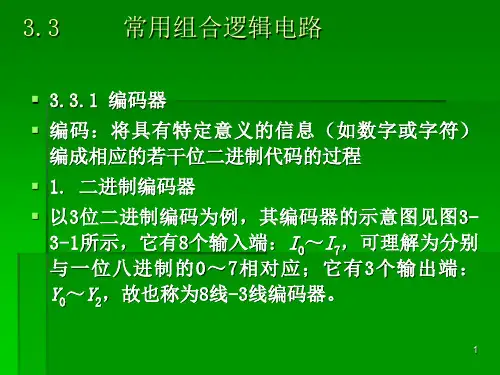

中规模集成电路MSI

12-99门,预先封装

大规模集成电路LSI

大约100-9999门,存储器

超大规模集成电路VLSI

大于9999门,处理器

常用的中规模组合逻辑标准构件

数据选择器

常用的中规模组合逻辑标准构件

由数据选择器构成组合逻辑电路 代数法

例:用四选一数据选择器实现以下逻辑函数: F(X,Y,Z) = m(1,2,3,4,5,6)

组合逻辑分析 组合逻辑设计 考虑特殊问题的逻辑设计 组合逻辑中竟争冒险 常用的中规模组合逻辑标准构件

组合逻辑中的竞争冒险

竞争冒险的概念及其产生的原因

信号经不同的路径到达同一点的时间有先后, 这种现象叫“竞争现象” 产生错误输出或结果的竞争叫“冒险”或者“险象”

组合逻辑中的竞争冒险

消除竞争冒险的方法 加选通脉冲:

4 12

A

F=BD+BC+A= BD•BC•A

B D B C A

F

B

考虑特殊问题的逻辑设计

考虑级数的逻辑设计

例:用与非门、与或非门分别实现以下函数: F=AB+AC F=AB+AC =AB+AC F=AB+AC F=AB+AC

F=AB•AC

2ty

2.5ty

1.5ty

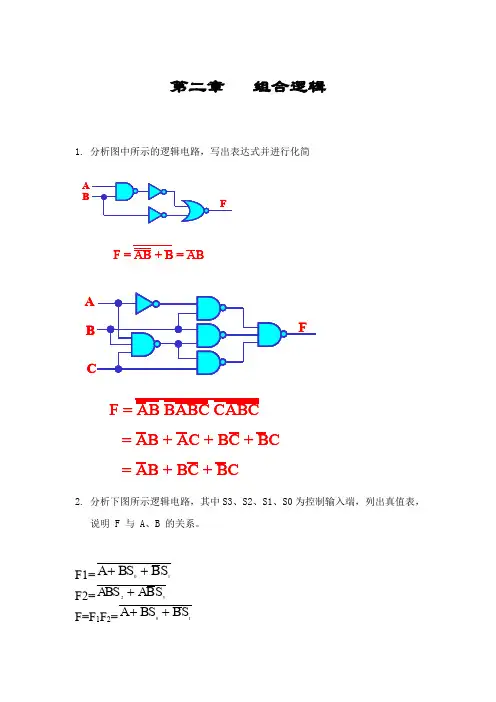

第二章 组合逻辑

四选一数据选择器:

Y=A1A0•D0+ A1A0 •D1+ A1A0 •D2+ A1A0 •D3= miDi

i=0

3

提取函数中两个变量作为地址变量

F

F(X,Y,Z) =XYZ+XY(Z+Z)+XY(Z+Z)+XYZ

Y X

A0

多路选择器

A1 D0 D1 D2 D3

Z 1 1 Z

常用的中规模组合逻辑标准构件

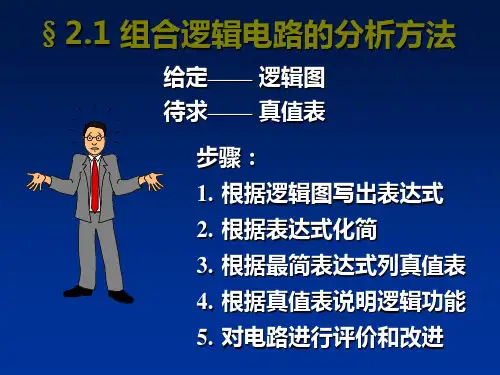

组合逻辑分析

一般分析步骤:

阅读组合逻辑电路图 列写逻辑表达式 列出真值表

指出电路的逻辑功能

做出对逻辑电路图的评价和改进

组合逻辑分析

分析下图逻辑功能

s c s=P1• P2 = P1+ P2 = AB+AB c=P3 =AB

P

1

s

c 0 0 0 1 HA A

c

P

2

P

3

A

B

••

0 4 5 7 6 12 13

1 1 1

8 9 11 10

F=AB+AC+BCD

C

1 3 2

1

15 14

1 1

D

1

B

组合逻辑设计

逻辑函数的“与非”门实 现 1. 原函数二次反演,一次展开:

例如:F=AB+BC+CD+DA A

1 1 1 1 1 1 1 1

F

F=AB+BC+CD+DA

D = AB•BC•CD•DA AB BC CD DA

B A

A 0 0 1 1

B 0 1 0 1

s 0 1 1 0

B

半加器

s= A B

组合逻辑分析

Si=Ai Bi Ci-1 =siCi-1+siCi-1 Si Ci =(AiBi+AiBi)Ci-1+(AiBi+AiBi)Ci-1 =AiBiCi-1+AiBiCi-1+AiBiCi-1+AiBiCi-1

考虑特殊问题的逻辑设计

例如:已知有四个输入变量的三个逻辑函数: F1=m(5,7,8,9,10,11,13) F2=m(1,7,11,15) F3=m(1,6,7,8,9,10,11) 求其一组最简的F1,F2,F3”与-或”表达式。

0 1 3 2 4

1 5 13 9 1 1 1 7 15 11 1 1 6 14 10 1

卡诺图法

用具有m个地址端的数据选择器实现n变量的函数 当 m = n 时:例如:八选一的数据选择器对应的卡诺图 F A2A1 A0 C

D0 D2 D1 D3 D6 D4 D7 D5

B A A0 多路选择器 A1 A2 D0 D1 D2 D3 D4 D5 D6 D7

•

AB C C

Vcc

例如:用八选一的数据选择器 实现函数: F =AB+AC+BC

2-4译码器

译中为“1”输出

译中为“0”输出

n-to-2n的译码器,对于每一种输入可能,只有一个输出信号被译中

n个输入2n个输出, 功能相当于最小项产生器

组合逻辑分析

数据选择器的分析

A 0 0 1 1 B 0 1 0 1 Y D0 D1 D2 D3

D0

D1 D2 D3 4-to-1

数据选择器

D0 D1 D2 D3

组合逻辑中的竞争冒险

A

修改逻辑设计:

F=AB+BC=AB+BC+AC

C

1

B

1

1 1

第二章 组合逻辑

组合逻辑分析 组合逻辑设计 考虑特殊问题的逻辑设计 组合逻辑中竟争冒险 常用的中规模组合逻辑标准构件

常用的中规模组合逻辑标准构件

集成电路规模的划分

小规模集成电路SSI

74系列,1-12门

HA

Ci= siCi-1+ci =(AiBi+AiBi)Ci-1+AiBi =AiBiCi-1+AiBiCi-1+AiBiCi-1+AiBiCi-1

Ai Bi Ci-1 Si Ci

0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 1 0 0 0 1 0 1 1 1

C D

C D

•

F2

A D

F2=ACD+BCD+ABC

C

1 1 1

1

1 1

F2

B

考虑特殊问题的逻辑设计

多输出的逻辑函数的化简步骤:

1. 构成各自函数以及各个函数之间所有组合相 交的卡诺图。 2. 找出每个卡诺图的所有极大块,如果在高一 级以上相交卡诺图已圈过的极大块,在后继 卡诺图中,不再圈出。

3. 构成函数的最小覆盖。对函数有关的所有卡诺 图,从高到低优先选择极大块,如果发现某级 的极大块被其它级极大块包含,此块应删去。 特点:点面相结合

12

8

1

1 1 1 1 1 1

1 1 1 1

F1=ABCD+BCD+AB F2= ABCD+ ABCD+ACD

F1

F2

1 1 1 1 1

F3

F3= ABCD+ ABC+AB

1

1

1

1

1

1

1

F1• F2

F1• F3

F2• F3

F1• F2• F3

考虑特殊问题的逻辑设计

F1 F2 F3

•

•

•

A B BCD ABCD ACD ABCD ABC