第2章(4) 组合逻辑电路-译码器

- 格式:ppt

- 大小:311.50 KB

- 文档页数:24

实验三组合逻辑电路应用——译码器、数据选择器

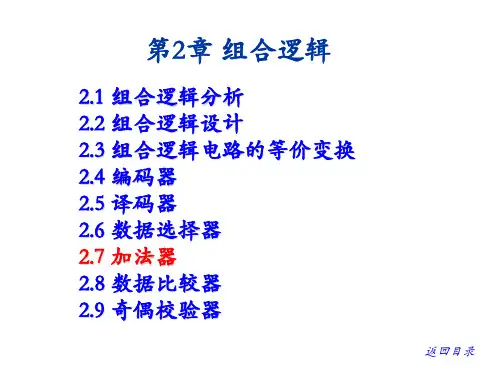

译码器和数据选择器是现代数字电子学中常用的两种组合逻辑电路。

它们可以将输入

的二进制信号转换为对应的输出信号,并且在数字电路中具有广泛的应用。

一、译码器

译码器是一种将输入的二进制信号转换成对应输出信号的数字电路。

译码器的作用是

将输入的地址码转换成溢出电路所能识别的控制信号,通常用来将不同的地址码映射到不

同的设备或功能上。

比如在存储器系统中,根据不同地址码,从RAM或者ROM中取出相应

的数据或指令。

除此之外,译码器还可以用于数据压缩、解码、解密等领域。

在一些数字电路中,译

码器还可以充当多路复用器、选择器等电路的功能。

译码器的分类按照其输入和输出的码制不同,可以分为译码器、BCD译码器、灰码译

码器等。

其中,最常见的是2-4译码器、3-8译码器、4-16译码器等。

二、数据选择器

数据选择器是一种多路选择器,根据控制信号选择输入端中的一个数据输出到输出端。

选择器的控制信号通常由一个二进制码输入到它的控制端,二进制码的大小由选择器的通

道数决定。

数据选择器广泛用于控制、多媒体处理、信号处理等方面。

数据选择器与译码器相比,最主要的区别在于其输出可以不仅限于数字信号。

数据选

择器可以处理模拟信号、复合信号等多种形式的信号,因为它可以作用于信号的幅度、相位、频率等方面。

数据选择器按照输入和输出的端口取数的不同,可以分为单路选择器和多路选择器。

常见的有2-1选择器、4-1选择器、8-1选择器、16-1选择器等。

数字逻辑电路实验实验报告学号:班级:姓名:实验3:组合逻辑电路(3)——组合逻辑电路设计一实验内容利用Quartus II实现0到9的Hamming码编码和解码电路,并在芯片中下载实现。

要求:实现对从0000到1001输入的编码和解码,并可发现并纠正传输中的单错,对双错不做要求。

在芯片中下载电路并在实验板上验证。

二实验原理2.1电路需求分析Hamming码是一套可定位码字传输中单错并纠正单错的编码体系,以4位二进制为例,其编解码和纠错原理如下:将7位二进制数的各位由低到高依次编号为1B、10B、11B、100B、……、111B。

其中为2的整数次幂的位(即1B、10B、100B)位校验位,其他四位作为数据位。

编码时,三个校验位分别与编号特定位为1的位上数字做奇偶校验(即编号位1B、11B、101B、111B的校验结果为1B位的值,10B、10B、100B、110B的校验结果为10B的值,100B、101B、110B和111B的校验结果为100B的值)。

偶校验在电路实现中更直接容易。

译码时,在仅考虑无错或单错的情形下,若三个校验位的校验结果均正确,则结果是四个数据位本身;若某位或某几位校验结果有错,可据此综合定位错误的位置:若仅1位校验结果有错,则错误出于该校验位本身;若2位校验结果有错,则该2位校验位所共同参与校验且不参与另一位校验的数据位结果有错;若三维结果均有错,则必然为111B位有错。

分析可知,编码电路可根据上述原理使用异或门实现,也可根据编码真值表由与门实现;译码电路中可使用3×4次异或运算生成校验结果,再由校验结果定位错误位后对相应位取反实现。

2.2Quartus软件从管脚分配到下载验证的过程Quartus中,在设计好电路的输入输出并选择合适的芯片型号后,可使用Pin Planner工具进行管脚分配:窗口下方有当前设计电路中所有的输入和输出节点,在Location中可选择对应节点对应的管脚。

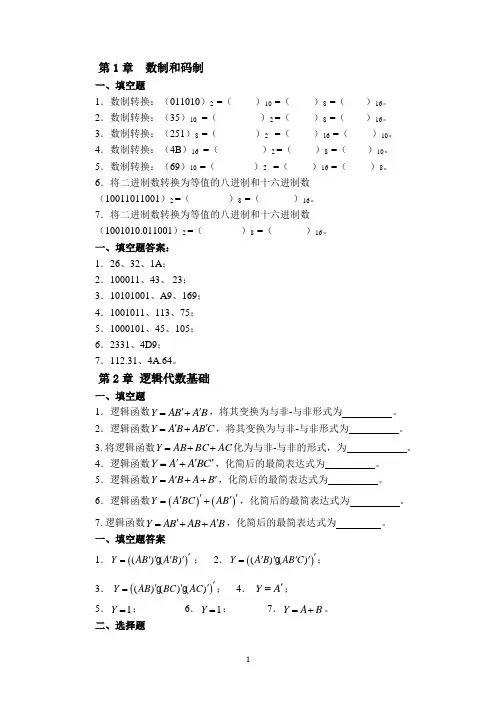

第1章 数制和码制一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数(10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数(1001010.011001)2 =( )8 =( )16。

一、填空题答案:1.26、32、1A ;2.100011、43、 23;3.10101001、A9、169;4.1001011、113、75;5.1000101、45、105;6.2331、4D9;7.112.31、4A.64。

第2章 逻辑代数基础一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=;3. ()()()()Y AB BC AC ''''=; 4. Y A '=;5.1Y =; 6.1Y =; 7.Y A B =+。

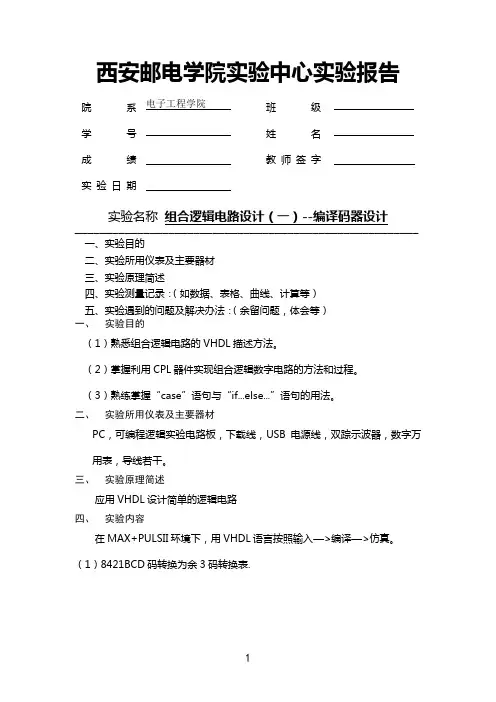

西安邮电学院实验中心实验报告院系电子工程学院班级学号姓名成绩教师签字实验日期实验名称组合逻辑电路设计(一)--编译码器设计_______________________________________________________一、实验目的二、实验所用仪表及主要器材三、实验原理简述四、实验测量记录:(如数据、表格、曲线、计算等)五、实验遇到的问题及解决办法:(余留问题,体会等)一、实验目的(1)熟悉组合逻辑电路的VHDL描述方法。

(2)掌握利用CPL器件实现组合逻辑数字电路的方法和过程。

(3)熟练掌握“case”语句与“if…else…”语句的用法。

二、实验所用仪表及主要器材PC,可编程逻辑实验电路板,下载线,USB电源线,双踪示波器,数字万用表,导线若干。

三、实验原理简述应用VHDL设计简单的逻辑电路四、实验内容在MAX+PULSII环境下,用VHDL语言按照输入—>编译—>仿真。

(1)8421BCD码转换为余3码转换表.在MAX+plusII 环境下,用VHDL 语言描述下列逻辑电路,并编译,仿真。

程序仿真结果:(2)设计一个优先编码器。

程序实现如下:仿真结果:五、实验结果见上述内容。

六、实验心得在本次实验中我学会了使用MAX+PLUSII软件的文本编程的方式设计电路。

在本次实验的文本编译环节中出现不少问题:(1)保存时文件名与实体名不一致,导致程序编译结果不正确。

(2)写程序时没有按照语法规则编写,使得文件编译频繁报错,标点的错误也会导致整个程序无法编译。

经过本次实验,加深了我对VHDL的文本编译设计的理解,今后我应该多练习MAX+PLUSII软件以减少错误。

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23.75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是-100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1。

(√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”。

(√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同。

(√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数。

()三、选择题1、在二进制技术系统中,每个变量的取值为(A)A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为(B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B)A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是(C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是 ( A )A 、加法运算B 、减法运算C 、乘法运算D 、除法运算9、二进制数-1011的补码是 ( D )A 、00100B 、00101C 、10100D 、1010110、二进制数最高有效位(MSB )的含义是 ( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。

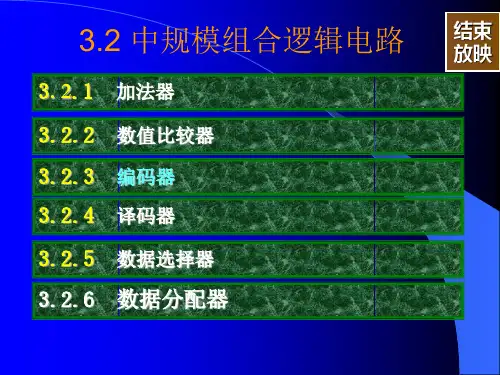

实验二 译码器、编码器及其应用一、实验目的1. 掌握中规模集成译码器、编码器的逻辑功能和使用方法。

2. 熟悉数码管的使用。

二、实验原理译码器是一个少输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器可分为通用译码器和专用译码器两大类。

前者又分为变量译码器和代码变换译码器。

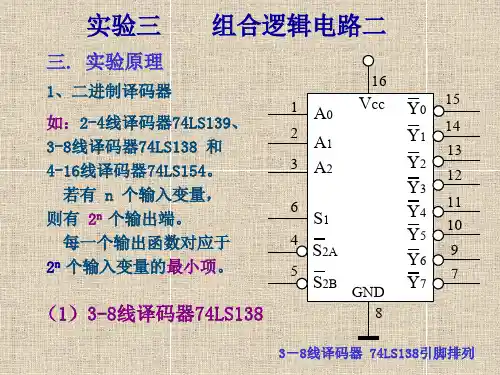

a . 变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线—4线、3线—8线和4线—16线译码器。

若有n 个输入变量,则有2n 个不同的组合状态,就有2n 个输出端供其使用。

而每个输出所代表的函数对应于n 个输入变量的最小项。

以3线—8线译码器74LS138为例进行分析,图9—1 分别为其逻辑图及引脚排列。

其中2A 、1A 、0A 为地址输入端,0Y ~7Y 为译码输出端,1S 、2S 、3S 为使能端。

321S S S A0 A1 A2图9-1 3—8线译码器74LS138逻辑图及引脚排列表9-1为74LS138功能表,当11=S ,032=+S S 时,器件使能,地址码所指定的输出有信号(为0)输出,其他所有输出端均无信号(全为1)输出。

当01=S ,X S S =+32时,或X S =1,132=+S S 时,译码器被禁止,所有输出同时为1。

表9-1A0 A1 A2S3 S2 S1 Y 7 GND(以下删除若干行)。

b.数据显示译码器七段发光二极管(LED)数码管LED数码管是目前最常用的数字显示器,(删除若字)。

一个LED数码管可用来显示一位0~9十进制和一个小数点。

小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2~2.5V,每个发光二极管的点亮电流在5~10mA。

实验二组合逻辑电路编码器译码器的设计与测试一、实验目的1.掌握编码器的原理和基本结构;2.了解译码器的原理和基本结构;3.掌握编码器和译码器的设计方法;4.通过实验,验证编码器和译码器的功能。

二、实验原理编码器是一种将多个输入信号转换为二进制编码输出的组合逻辑电路。

编码器的输入信号可以是多个,输出信号是二进制编码。

编码器主要用于将多个不同的输入信号通过编码转换为数字输出,使得电路的复杂度得到简化。

译码器就是编码器的逆过程,译码器是一种将二进制编码转换为多个输出信号的组合逻辑电路。

译码器的输入信号是二进制编码,输出信号可以是多个。

编码器和译码器是数字电路中非常重要的组合逻辑电路,广泛应用于计算机、通信、控制等领域。

三、实验内容根据所给的真值表,设计并实现一个2-4线的编码器;设计和实现一个4-2线的译码器;验证实验结果。

四、实验仪器和器件五、实验步骤1.编码器的设计和实现根据所给的真值表,设计并实现一个2-4线的编码器。

首先,根据编码器的输入和输出关系,设计出2-4线的编码器的真值表,并根据真值表进行逻辑设计。

编码器的输入信号有2个,输出信号是4位的二进制编码。

最后,将开关和LED灯连接到逻辑电路上,进行测试和验证。

调试完毕后,记录下测试结果。

2.译码器的设计和实现设计和实现一个4-2线的译码器。

首先,根据译码器的输入和输出关系,设计出4-2线的译码器的真值表,并根据真值表进行逻辑设计。

译码器的输入信号是4位的二进制编码,输出信号有2个。

最后,将开关和LED灯连接到逻辑电路上,进行测试和验证。

调试完毕后,记录下测试结果。

3.验证实验结果通过对编码器和译码器的测试,验证实验结果是否符合设计要求。

当输入信号发生变化时,观察LED灯的亮灭情况,确认编码器和译码器的功能是否正确。

六、实验结果与分析经过实验测试,编码器和译码器的功能正常,符合设计要求。

输入信号的变化能够正确地转换为二进制编码输出;输入二进制编码信号能够正确地转换为输出信号。

第2章习题一、单选题1.若在编码器中有50个编码对象,则输出二进制代码位数至少需要( B )位。

A)5 B)6 C)10 D)502.一个16选1的数据选择器,其选择控制(地址)输入端有( C )个,数据输入端有( D )个,输出端有( A )个。

A)1 B)2 C)4 D)163.一个8选1的数据选择器,当选择控制端S2S1S0的值分别为101时,输出端输出( D )的值。

A)1 B)0 C)D4D)D54.一个译码器若有100个译码输出端,则译码输入端至少有( C )个。

A)5 B)6 C)7 D)85.能实现并-串转换的是( C )。

A)数值比较器B)译码器C)数据选择器D)数据分配器6.能实现1位二进制带进位加法运算的是( B )。

A)半加器B)全加器C)加法器D)运算器7.欲设计一个3位无符号数乘法器(即3×3),需要()位输入及( D )位输出信号。

A)3,6 B)6,3 C)3,3 D)6,68.欲设计一个8位数值比较器,需要()位数据输入及( B )位输出信号。

A)8,3 B)16,3 C)8,8 D)16,169. 4位输入的二进制译码器,其输出应有( A )位。

A)16 B)8 C)4 D)1二、判断题1. 在二——十进制译码器中,未使用的输入编码应做约束项处理。

(✓)2. 编码器在任何时刻只能对一个输入信号进行编码。

(✓)3. 优先编码器的输入信号是相互排斥的,不容许多个编码信号同时有效。

(✗)4. 编码和译码是互逆的过程。

(✓)5. 共阴发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

(✓)6. 3位二进制编码器是3位输入、8位输出。

(✗)7. 组合逻辑电路的特点是:任何时刻电路的稳定输出,仅仅取决于该时刻各个输入变量的取值,与电路原来的状态无关。

(✓)8. 半加器与全加器的区别在于半加器无进位输出,而全加器有进位输出。

(✗)9. 串行进位加法器的优点是电路简单、连接方便,而且运算速度快。