同步时序电路设计举例共48页文档

- 格式:ppt

- 大小:2.53 MB

- 文档页数:48

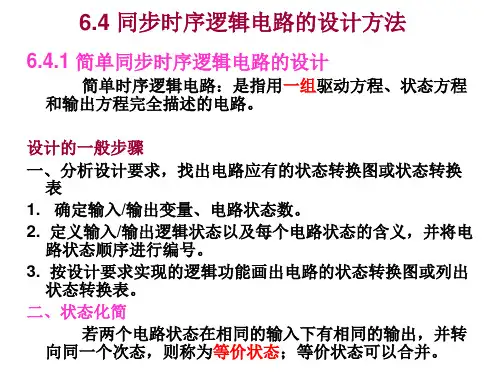

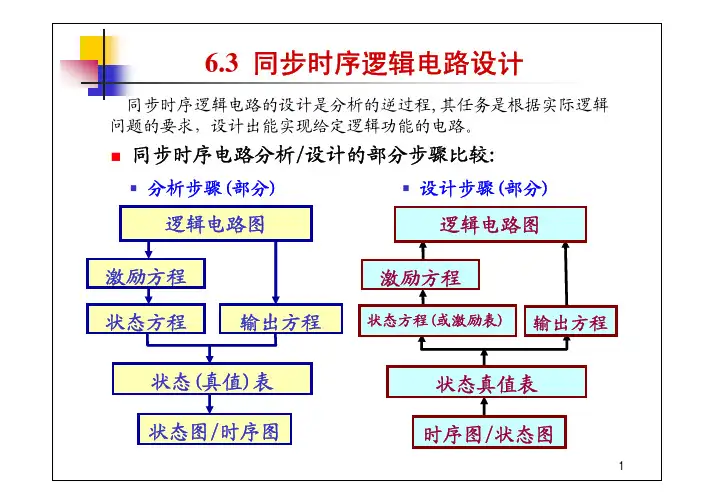

6.3 同步时序逻辑电路设计同步时序逻辑电路的设计是分析的逆过程,其任务是根据实际逻辑 问题的要求,设计出能实现给定逻辑功能的电路。

同步时序电路分析/设计的部分步骤比较: 分析步骤(部分) 设计步骤(部分)逻辑电路图 激励方程 状态方程 输出方程逻辑电路图 激励方程状态方程(或激励表)输出方程状态(真值)表 状态图/时序图状态真值表 时序图/状态图1同步时序电路设计的一般步骤给定逻辑功能 原始状态图/表(符号化) 状态化简 状态编码→ 状态(真值)表 选触发器类型修改激励和输出方程 N能自启动?Y逻辑电路图2原始状态图/表的建立根据给定的逻辑功能建立原始状态图和原始状态表①根据电路的输入条件和相应的输出要求,分别确定输入变量 和输出变量的含义和数目。

②找出所有可能的状态(以符号表示),根据电路的工作过程 和规律确定状态之间的转换关系。

③根据原始状态图建立原始状态表。

建立原始状态图没有统一的方法,但一般可以如下考虑: - 设立初始状态,然后从初始状态出发考虑在各种输入信号作用下的状态转移和输出响应。

- 根据问题中要求记忆和区分的信息去考虑设立每一个状态。

一般说来,若在某个状态下输入信号后不能用已有状态表示 时,应增加一个新的状态。

3状态化简合并等价状态,消去多余状态的过程称为状态化简. 等价状态:在相同的输入下有相同的输出,并且它们的 次态相同或次态等价。

例: 原始状态表 最后简化的状态表现态 (Sn) a b c d e f g 次态/输出(S n+1/Y) A=0 A=1 a/0 b/0 c/0 d/0 a/0 d/0 e/0 f/1 a/0 f/1 g/0 f/1 a/0 f/1 e与g 等价 d与 f 等价 删掉 g与f 现态 (Sn) a b c d e 次态/输出(S n+1/Y) A=0 a/0 c/0 a/0 e/0 a/0 A=1 b/0 d/0 d/0 d/1 d/1(状态化简有时需要经过反复多次检查)4状态编码状态编码(或状态分配) :将每个状态用一个n位二进制代码表示。