数电第五版(阎石)第六章课后习题及答案

- 格式:pptx

- 大小:548.61 KB

- 文档页数:13

第8章 可编程逻辑器件一、选择题1.(多选)关于PROM和PAL的结构,以下叙述正确的是()。

A.PROM的与阵列固定,不可编程B.PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D.PAL的与阵列可编程【答案】AD【解析】PROM由存储矩阵、地址译码器和输出电路组成。

其中与阵列是固定的,不可编程,初始时所有存储单元中都存入了1,可通过将所需内容自行写入PROM而得到要求的ROM,PROM的内容一经写入以后(改变的是或阵列),不能修改。

PAL器件由可编程的与逻辑阵列、固定的或逻辑阵列和输出电路三部分组成。

二、填空题1.与PAL相比,GAL器件有可编程的输出结构,它是通过对______行编程设定其______的工作模式来实现的,而且由于采用了______的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

【答案】机构控制字;输出逻辑宏单元;E2CMOS2.PAL是______可编程,EPROM是______可编程。

【答案】与阵列;或阵列3.GAL 是______可编程,GAL 中的OLMC 称______【答案】与阵列;输出逻辑宏单元4.在图8-1所示的可编程阵列逻辑(PAL )电路中,Y 1=______,Y 3=______。

图8-1【答案】;123234134124I I I I I I I I I I I I +++12I I ⊕【解析】×表示连通,在一条线上的×表示与,然后通过或门连接在一起。

三、简答题1.如图8-2所示为PAL16L8的一部分电路,试分析该电路,写出电路在X 控制下的函数F 对应于输入A 、B 、C 的逻辑表达式。

图8-2答:当X=0时,F所在三态门选通;X=1时,三态门关闭。

故该电路的逻辑关系式为:。

2.下面图8-3所示的3个卡诺图代表3个4变量逻辑的逻辑函数。

(1)用PROM实现,画出码点矩阵图;(2)用PLA实现,画出码点矩阵图。

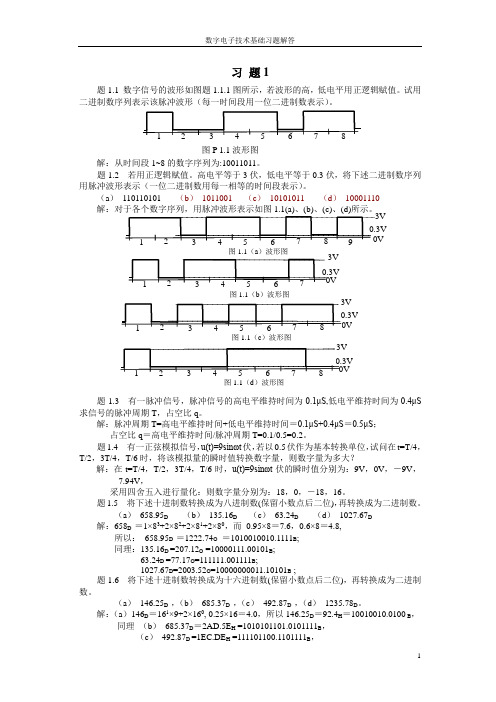

习 题1题1.1 数字信号的波形如图题1.1.1图所示,若波形的高,低电平用正逻辑赋值。

试用二进制数序列表示该脉冲波形(每一时间段用一位二进制数表示)。

解:从时间段1~8的数字序列为:10011011。

题1.2 若用正逻辑赋值。

高电平等于3伏,低电平等于0.3伏,将下述二进制数序列用脉冲波形表示(一位二进制数用每一相等的时间段表示)。

(a ) 110110101 (b ) 1011001 (c ) 10101011 (d ) 10001110解:对于各个数字序列,用脉冲波形表示如图1.1(a)、(b)、(c)、(d)所示。

题1.3 有一脉冲信号,脉冲信号的高电平维持时间为0.1μS,低电平维持时间为0.4μS 求信号的脉冲周期T ,占空比q 。

解:脉冲周期T=高电平维持时间+低电平维持时间=0.1μS+0.4μS =0.5μS ;占空比q =高电平维持时间/脉冲周期T=0.1/0.5=0.2。

题1.4 有一正弦模拟信号,u(t)=9sinωt 伏,若以0.5伏作为基本转换单位,试问在t=T/4,T/2,3T/4,T/6时,将该模拟量的瞬时值转换数字量,则数字量为多大?解:在t=T/4,T/2,3T/4,T/6时,u(t)=9sinωt 伏的瞬时值分别为:9V ,0V ,-9V ,7.94V ,采用四舍五入进行量化:则数字量分别为:18,0,-18,16。

题1.5 将下述十进制数转换成为八进制数(保留小数点后二位),再转换成为二进制数。

(a ) 658.95D (b ) 135.16D (c ) 63.24D (d ) 1027.67D解:658D =1×83+2×82+2×81+2×80,而 0.95×8=7.6,0.6×8=4.8,所以: 658.95D =1222.74O =1010010010.1111B ;同理:135.16D =207.12O =10000111.00101B ;63.24D =77.17O =111111.001111B ;1027.67D =2003.52O =10000000011.10101B ;题1.6 将下述十进制数转换成为十六进制数(保留小数点后二位),再转换成为二进制数。

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

第6章 时序逻辑电路一、选择题1.一个六位二进制减法计数器,初始状态为000000,问经过203个输入脉冲后,此计数器的状态为()。

[电子科技大学2008研]A.110011B.110101C.111000D.110110【答案】B【解析】六位减法器的计数周期为;203%64=11,即从000000经过11个6264计数周期,输出状态变为110101。

2.为了把串行输入的数据转换为并行输出的数据,可以使用()。

[北京科技大学2010研]A.寄存器B.移位寄存器C.计数器D.存储器【答案】B【解析】移位寄存器能能够串行输入串行输出,并行输入并行输出,串行输入并行输出。

3.一个四位二进制码加法计数器的起始值为1001,经过100个时钟脉冲后的值为( )。

[北京邮电大学2010研]A .1110B .1111C .1101D .1100【答案】C【解析】1001经过16的倍数个周期后仍为1001,即96个时钟脉冲后计数器显示1001,再经历4个时钟脉冲,即100个时钟脉冲时,计数为1001+0100(4)=11014.某计数器的状态转换图如下图所示,该计数器的模为( )。

[电子科技大学2010研]A .三B .四C .五D .八图6-1【答案】C【解析】循环状态的有5个,也就是说当计数器使用的过程中只有这5个状态才能保持一直计数。

二、填空题1.8级扭环计数器的状态转换圈中,无效状态有______个。

[电子科技大学2008研]【答案】240【解析】n 级扭环计数器的无效状态共有:个。

22n n 2.用移位寄存器产生1101010序列,至少需要______位的移位寄存器。

[电子科技大学2010研]【答案】6【解析】共七位序列数,由于采用移位寄存器,而且状态在序列中没有循环,移位寄存器在传输过程中数据是一次传递的,所以需要至少6位移位寄存器。

表6-13.一个三级环形计数器的初始状态是Q2Q1Q0=001(Q2为高位),则经过40个时钟周期后的状态Q2Q1Q0=______。

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

第6章 时序逻辑电路6.1 分析图6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图6-1解:电路的驱动方程为12121211J Q ',K J Q ,K ====将驱动方程代入JK 触发器的特性方程''Q JQ K Q *=+,可得电路的状态方程为12111212n n Q Q 'Q ',Q Q Q '++==电路的输出方程为2Y Q =因此,可画出状态转换图及时序图如图6-2所示。

图6-26.2 分析图6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

图6-3解:电路的驱动方程为1321312D Q ',D Q D Q Q ===将驱动方程代入D 触发器的特性方程Q D *=,可得电路的状态方程为1231113112n n n Q Q ',Q Q Q Q Q +++===电路的输出方程为()13Y Q 'Q '=因此,可画出状态转换图如图6-4所示,可见电路可以自启动。

图6-46.3 分析图6-5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图6-5解:电路的驱动方程为11322131233J K Q ',J K Q ,J Q Q ,K Q ======将驱动方程代入JK 触发器的特性方程1''n QJQ K Q +=+,可得电路的状态方程为113131n Q Q 'Q 'Q Q +=+=Q 3⊙Q 12311212121123n n Q Q Q 'Q 'Q Q Q Q Q Q Q '++=+=⊕=电路的输出方程为3Y Q =因此,可画出状态转换图如图6-6所示,可见电路可以自启动。

图6-66.4 试分析图6-7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。