数电第五版(阎石)第六章课后习题及答案资料讲解

- 格式:ppt

- 大小:379.50 KB

- 文档页数:13

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

数字电子技术基础备课笔记汤洪涛一、课程简介《数字电子技术基础》是电力、计算机工程类各专业的一门技术基础课,它是研究各种半导体器件的性能、电路及应用的学科。

数字电子技术包括逻辑代数基础、逻辑门电路、组合逻辑电路、触发器、时序逻辑电路、半导体存储器、可编程逻辑器件、VHDL 语言、脉冲信号的产生与整形和A/D与D/A转换器等内容。

本课程以小规模集成电路为基础,(门电路)以中规模集成电路为主,着重介绍各种逻辑单元电路,逻辑部件的工作原理,分析逻辑功能,介绍逻辑电路的分析方法和一般数字电路的设计方法。

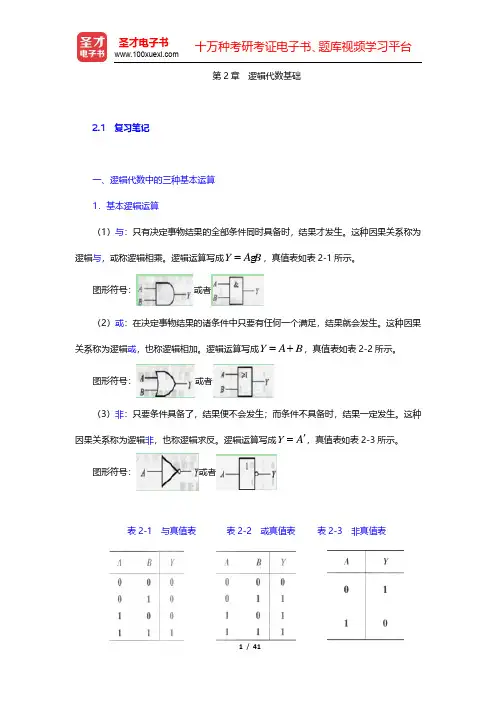

二、各章节主要内容和基本要求第一章数制与码制:它是整个数字逻辑电路的基本知识,要求能够熟练掌握;第二章逻辑代数基础:它是整个数字逻辑电路的分析工具,要求能够熟练掌握和应用,其中逻辑代数化简法和卡诺图化简法是重点掌握内容。

第三章逻辑门电路:是组成逻辑电路的基本单元,它相当于模电中的二极管、三极管。

基本门电路有DTL(二极管门)、TTL(三极管门)、MOS(场效应管门),要求掌握它们的组成原理。

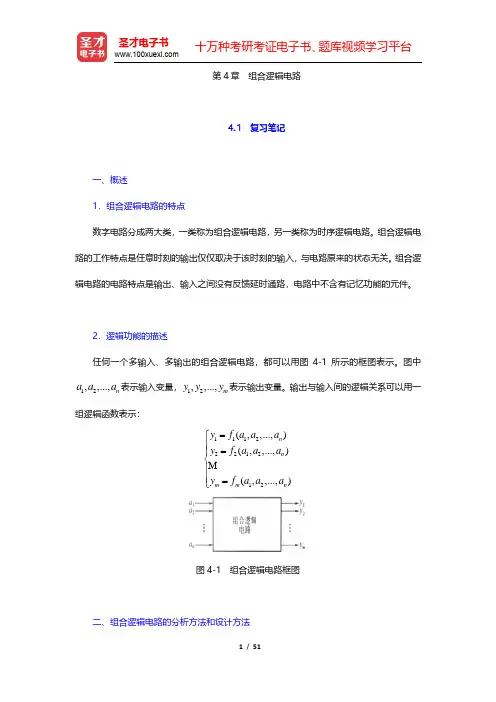

第四章组合逻辑电路:它是数字电子技术的一大类,要求掌握组合逻辑电路的分析和设计方法,即已知逻辑电路,请分析该电路的所能实现的逻辑功能;或已知该电路的所要实现的逻辑功能,请设计逻辑电路的来实现其逻辑功能。

当然,设计电路就有一个电路的优化设计问题,如何选择最少的基本逻辑单元电路或最廉价的或最方便的基本逻辑单元电路来就可以实现所需要的逻辑功能。

(只考虑输入、输出之间的逻辑关系)第五章触发器:触发器是时序逻辑电路的基本逻辑单元,掌握触发器的基本特点、工作原理和分析方法等。

第六章时序逻辑电路:要求掌握时序逻辑电路的分析、波形的绘制等。

第七章半导体存储器:主要讲述动静态的RAM(随机存储器)和ROM(只读存储器)要求掌握它们的基本概念及其应用。

第八章以后的章节不做讲解好要求,让大家以后如果接触到相关知识时可以查阅。

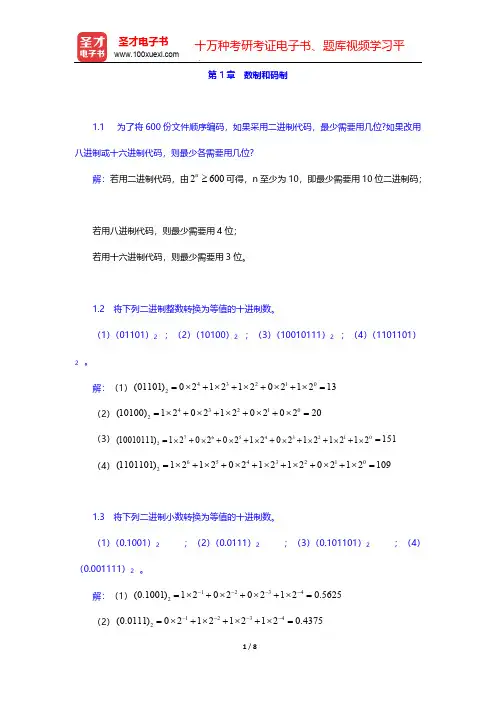

第一章数制和码制本章要求:掌握十进制、二进制、十六进制、八进制之间的转换1.1 概述一、电子信号的分类:电子电路中的信号可分为两类:1、一类是时间和数值上都是连续变化的信号,称为模拟信号,例如音频信号、温度信号等;2、另外一类是在时间或数值上断续变化的信号,即离散信号,称为数字信号,例如工件个数的记数信号,键盘输入的电信号等。

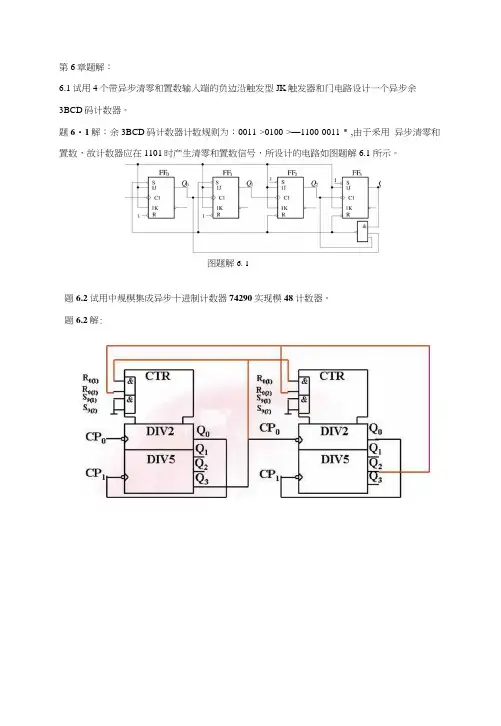

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

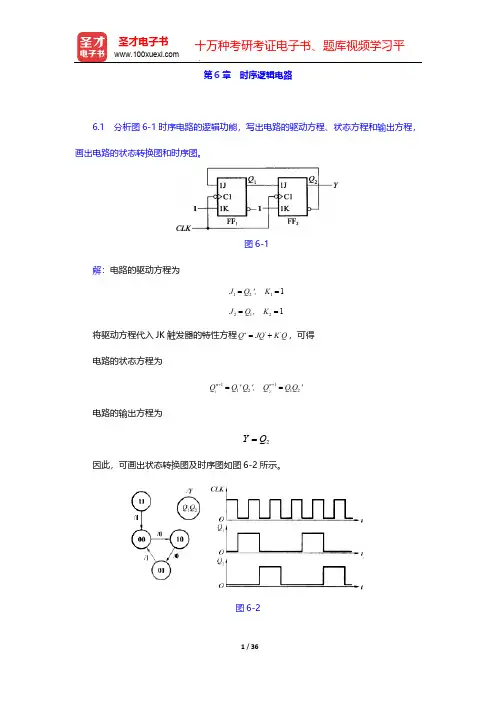

第6章 时序逻辑电路6.1 分析图6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图6-1解:电路的驱动方程为12121211J Q ',K J Q ,K ====将驱动方程代入JK 触发器的特性方程''Q JQ K Q *=+,可得电路的状态方程为12111212n n Q Q 'Q ',Q Q Q '++==电路的输出方程为2Y Q =因此,可画出状态转换图及时序图如图6-2所示。

图6-26.2 分析图6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

图6-3解:电路的驱动方程为1321312D Q ',D Q D Q Q ===将驱动方程代入D 触发器的特性方程Q D *=,可得电路的状态方程为1231113112n n n Q Q ',Q Q Q Q Q +++===电路的输出方程为()13Y Q 'Q '=因此,可画出状态转换图如图6-4所示,可见电路可以自启动。

图6-46.3 分析图6-5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图6-5解:电路的驱动方程为11322131233J K Q ',J K Q ,J Q Q ,K Q ======将驱动方程代入JK 触发器的特性方程1''n QJQ K Q +=+,可得电路的状态方程为113131n Q Q 'Q 'Q Q +=+=Q 3⊙Q 12311212121123n n Q Q Q 'Q 'Q Q Q Q Q Q Q '++=+=⊕=电路的输出方程为3Y Q =因此,可画出状态转换图如图6-6所示,可见电路可以自启动。

图6-66.4 试分析图6-7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。

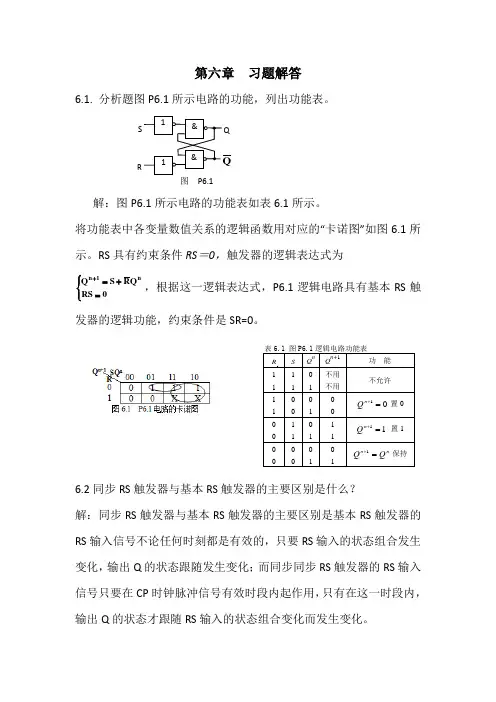

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

第1章数制和码制1.1复习笔记一、数字信号与数字电路1.模拟信号和数字信号模拟信号:幅度和时间连续变化的信号。

例如,正弦波信号。

数字信号:在幅度和时间上取值离散的信号。

例如,统计一座桥上通过的汽车数量。

模拟信号经过抽样、量化、编码后可转化为数字信号。

数字信号的表示方式:(1)采用二值数字来表示,即0、1数字;0为逻辑0,1为逻辑1。

(2)采用逻辑电平来表示,即H(高电平)和L(低电平)。

(3)采用数字波形来表示。

2.模拟电路和数字电路模拟电路:工作在模拟信号下的电路统称为数字电路。

数字电路:工作在数字信号下的电路统称为数字电路。

数字电路的主要研究对象是电路的输入和输出之间的逻辑关系;主要分析工具是逻辑代数关系;表达电路的功能的方法有真值表,逻辑表达式及波形图等。

二、几种常用的进制不同的数码既可以用来表示不同数量的大小,又可以用来表示不同的事物。

在用数码表示数量的大小时,采用的各种计数进位制规则称为数制,主要包括进位制、基数和位权三个方面。

进位制:多位数码每一位的构成以及从低位到高位的进位规则。

基数:在进位制中可能用到的数码个数。

位权:在某一进位制的数中,每一位的大小都对应着该位上的数码乘上一个固定的数,这个固定的数就是这一位的权数,权数是一个幂。

常用的数制有十进制、二进制、八进制和十六进制几种。

1.十进制在十进制数中,每一位有0~9十个数码,所以计数基数为10。

超过9的数必须用多位数表示,其中低位和相邻高位之间的关系是“逢十进一”,故称为十进制。

十进制的展开形式为式中,是第i位的系数,可以是0~9十个数码中的任何一个。

任意N进制的展开形式为式中,是第i位的系数,N为计数的基数,为第i位的权。

2.二进制在二进制数中,每一位仅有0和1两个可能的数码,计数基数为2。

低位和相邻高位间的进位关系是“逢二进一”。

二进制的展开形式为例如,(101.11)2=1×22+0×21+1×20+1×2-1+0×2-2=(5.75)10。

第五章锁存器和触发器1、Q n 1二S RQ n, SR = O2、Q n, 03、324、TCP J I I I I I I I7、4-13题解图8、D= A 二BCP_ I~I I~I I~I I~I I~LI Iz卄I TH 1D i - I i i1 . I | , __ L,I ■ I ______第六章时序逻辑电路1、 输入信号,原来的状态2、 异3、 n 5、反馈清零、反馈置数扌-6、N乂—LJ UU 仑厂 II ~ 7、状态方程和输出方程:㈣ =A®Q'tZ^AQ&激励方程A =Kq = A &/. =e 0=i 状态方程0:戚;忧"无©土死输出方程Z=AQ1Q0根据状态方程组和输出方程可列出状态表,如表题解6 . 2 . 4所示,状态图如图题解2. 4 所示。

Q - M?; + M V ;* Q ; = + “:14、图题解6.2.4Q;・枫"烟00保持,01右移10左移11并行输入当启动信号端输人一低电平时,使S仁1 ,这时有So= Sl= 1 ,移位寄存器74HC194执行并行输人功能,Q3Q2Q1Q0 = D3D2D1D0 = 1110。

启动信号撤消后,由于Q°= 0,经两级与非门后,使S仁0 ,这时有S1S0= 01 ,寄存器开始执行右移操作。

在移位过程中,因为Q3Q2、Q1、Q0中总有一个为0,因而能够维持S1S0=01状态,使右移操作持续进行下去°其移位情况如图题解6, 5, 1所示。

该电路能按固定的时序输出低电平脉冲,是一个四相时序脉冲产生电路。

-JT AAA TL幺I15、状态方程为儿⑷儿個)X(O24、解:74HC194功能由S1S0控制。