数电第五版阎石第六章课后习题及答案

- 格式:pptx

- 大小:548.20 KB

- 文档页数:13

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

第五章-第六章习题习题一1、由与非门组成的基本SR锁存器,输入端分别为S、R为使锁存器处于“置1”状态,其S、R端应为。

(A)SR=00 (B)SR=01 (C)SR=10 (D)SR=112、有一个T触发器,在T=1 时,加上时钟脉冲,则触发器。

(A)保持原态(B)置0 (C)置1 (D)翻转3、假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

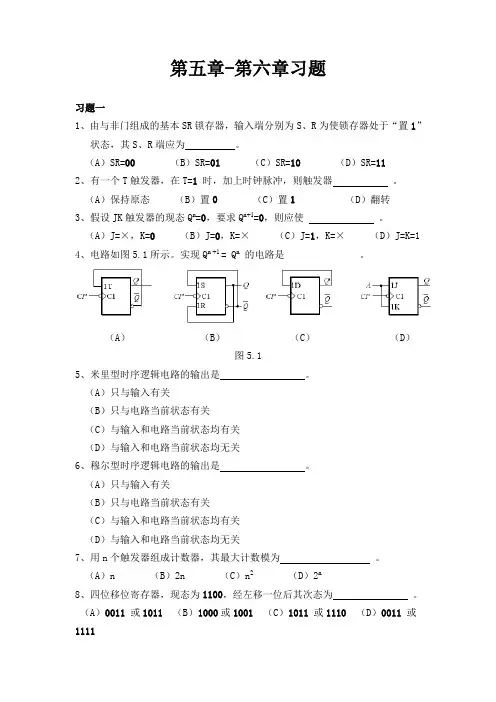

(A)J=×,K=0 (B)J=0,K=×(C)J=1,K=×(D)J=K=1 4、电路如图5.1所示。

实现Q n +1 = Q n的电路是。

(A)(B)(C)(D)图5.15、米里型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关6、穆尔型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关7、用n个触发器组成计数器,其最大计数模为。

(A)n (B)2n (C)n2(D)2n8、四位移位寄存器,现态为1100,经左移一位后其次态为。

(A)0011 或1011 (B)1000或1001 (C)1011 或1110 (D)0011 或11119、下列电路中,不属于时序逻辑电路的是。

(A)计数器(B)全加器(C)寄存器(D)分频器10、一个5 位的二进制加计数器,由00000 状态开始,经过75个时钟脉冲后,此计数器的状态为:(A)01011 (B)01100 (C)01010 (D)00111 11、图5.2所示为某时序电路的时序图,由此可知该时序电路具有的功能。

(A)十进制计数器(B)九进制计数器(C)四进制计数器(D)八进制计数器图5.2习题二5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号;与电路原来所处的状态;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号;与信号作用前电路原来所处的状态。

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E++ +( ) = + +解:A+ABC ACD C D E++ +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式 (3)ABC B( +C)解:ABCB( +C)= + +(A B C B C)( + )=AB AC BB BC CB C+ + + + +=AB C A B B+ ( + + +1)=AB C+(6)(A + + + +B A B AB AB ) ( ) ( )() 解:(A + + + +B A B AB AB ) () ( )( )= A B ⋅+ A B ⋅+(A + B A )(+ B )=AB(9)ABCD ABD BCD ABCBD BC + + + +解:ABCD ABD BCD ABCBD BC +++ +=ABC D D ABD BC D C ( + +) + ( + ) =B AC AD C D ( + + + ) =B A C AD ( + + + ) =B A C D ( + + ) =AB BC BD + +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B = +(1)L AB AC =(2) ( ) L DAC = +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3) ( )() L ABCD=+ +解: ( , , , ) L ABCDBCDBCDBCDABD = + + +(1)ABCD ABCD AB AD ABC+ + + +解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D++ ( + )( + +)( + )( + +)( + )=ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + + + + +(6)L A B C D( , , , )=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L= +A D(7)L A B C D( , , , )=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L AD AC AB= + +已知逻辑函数L AB BC CA=+ + ,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC ⋅ ⋅4>由已知函数的与非-与非表达式画出逻辑图2> 由真值表画出卡诺图3> 由卡诺图,得逻辑表达式 LABBCAC = + +第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

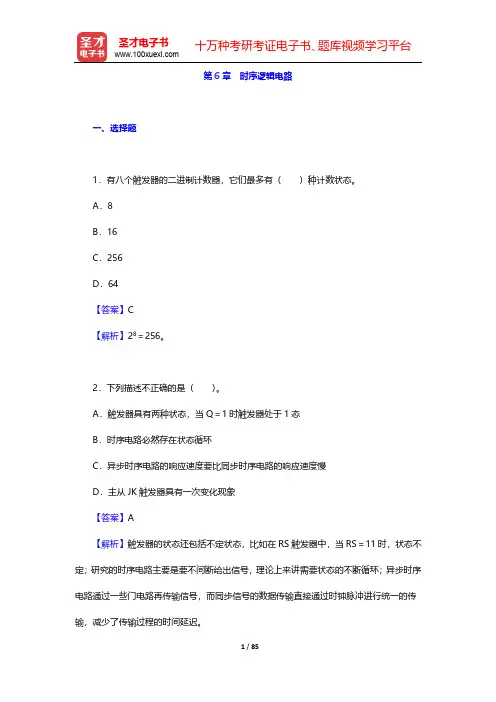

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

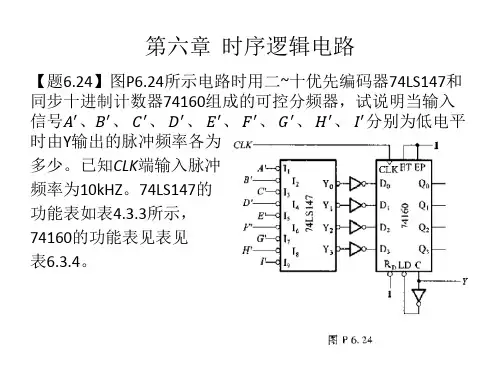

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

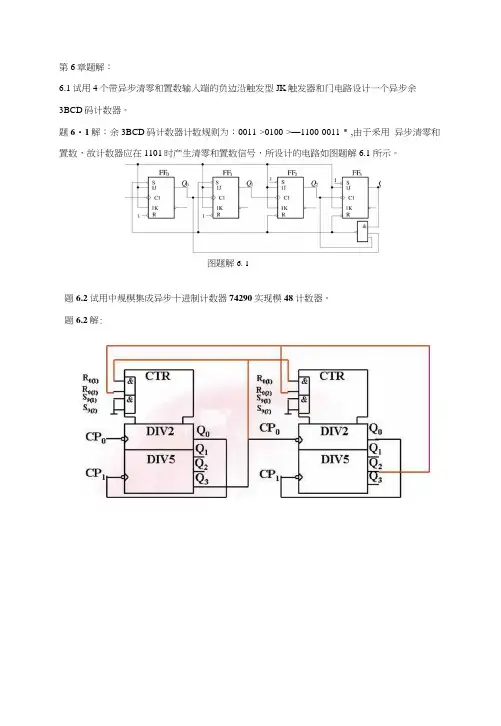

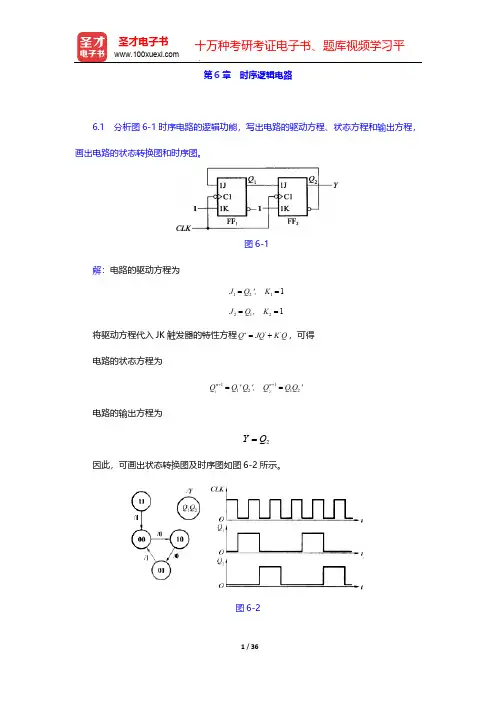

第6章 时序逻辑电路6.1 分析图6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图6-1解:电路的驱动方程为12121211J Q ',K J Q ,K ====将驱动方程代入JK 触发器的特性方程''Q JQ K Q *=+,可得电路的状态方程为12111212n n Q Q 'Q ',Q Q Q '++==电路的输出方程为2Y Q =因此,可画出状态转换图及时序图如图6-2所示。

图6-26.2 分析图6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

图6-3解:电路的驱动方程为1321312D Q ',D Q D Q Q ===将驱动方程代入D 触发器的特性方程Q D *=,可得电路的状态方程为1231113112n n n Q Q ',Q Q Q Q Q +++===电路的输出方程为()13Y Q 'Q '=因此,可画出状态转换图如图6-4所示,可见电路可以自启动。

图6-46.3 分析图6-5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图6-5解:电路的驱动方程为11322131233J K Q ',J K Q ,J Q Q ,K Q ======将驱动方程代入JK 触发器的特性方程1''n QJQ K Q +=+,可得电路的状态方程为113131n Q Q 'Q 'Q Q +=+=Q 3⊙Q 12311212121123n n Q Q Q 'Q 'Q Q Q Q Q Q Q '++=+=⊕=电路的输出方程为3Y Q =因此,可画出状态转换图如图6-6所示,可见电路可以自启动。

图6-66.4 试分析图6-7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

第1章数制和码制1.1复习笔记一、数字信号与数字电路1.模拟信号和数字信号模拟信号:幅度和时间连续变化的信号。

例如,正弦波信号。

数字信号:在幅度和时间上取值离散的信号。

例如,统计一座桥上通过的汽车数量。

模拟信号经过抽样、量化、编码后可转化为数字信号。

数字信号的表示方式:(1)采用二值数字来表示,即0、1数字;0为逻辑0,1为逻辑1。

(2)采用逻辑电平来表示,即H(高电平)和L(低电平)。

(3)采用数字波形来表示。

2.模拟电路和数字电路模拟电路:工作在模拟信号下的电路统称为数字电路。

数字电路:工作在数字信号下的电路统称为数字电路。

数字电路的主要研究对象是电路的输入和输出之间的逻辑关系;主要分析工具是逻辑代数关系;表达电路的功能的方法有真值表,逻辑表达式及波形图等。

二、几种常用的进制不同的数码既可以用来表示不同数量的大小,又可以用来表示不同的事物。

在用数码表示数量的大小时,采用的各种计数进位制规则称为数制,主要包括进位制、基数和位权三个方面。

进位制:多位数码每一位的构成以及从低位到高位的进位规则。

基数:在进位制中可能用到的数码个数。

位权:在某一进位制的数中,每一位的大小都对应着该位上的数码乘上一个固定的数,这个固定的数就是这一位的权数,权数是一个幂。

常用的数制有十进制、二进制、八进制和十六进制几种。

1.十进制在十进制数中,每一位有0~9十个数码,所以计数基数为10。

超过9的数必须用多位数表示,其中低位和相邻高位之间的关系是“逢十进一”,故称为十进制。

十进制的展开形式为式中,是第i位的系数,可以是0~9十个数码中的任何一个。

任意N进制的展开形式为式中,是第i位的系数,N为计数的基数,为第i位的权。

2.二进制在二进制数中,每一位仅有0和1两个可能的数码,计数基数为2。

低位和相邻高位间的进位关系是“逢二进一”。

二进制的展开形式为例如,(101.11)2=1×22+0×21+1×20+1×2-1+0×2-2=(5.75)10。

第五章锁存器和触发器1、Q n 1二S RQ n, SR = O2、Q n, 03、324、TCP J I I I I I I I7、4-13题解图8、D= A 二BCP_ I~I I~I I~I I~I I~LI Iz卄I TH 1D i - I i i1 . I | , __ L,I ■ I ______第六章时序逻辑电路1、 输入信号,原来的状态2、 异3、 n 5、反馈清零、反馈置数扌-6、N乂—LJ UU 仑厂 II ~ 7、状态方程和输出方程:㈣ =A®Q'tZ^AQ&激励方程A =Kq = A &/. =e 0=i 状态方程0:戚;忧"无©土死输出方程Z=AQ1Q0根据状态方程组和输出方程可列出状态表,如表题解6 . 2 . 4所示,状态图如图题解2. 4 所示。

Q - M?; + M V ;* Q ; = + “:14、图题解6.2.4Q;・枫"烟00保持,01右移10左移11并行输入当启动信号端输人一低电平时,使S仁1 ,这时有So= Sl= 1 ,移位寄存器74HC194执行并行输人功能,Q3Q2Q1Q0 = D3D2D1D0 = 1110。

启动信号撤消后,由于Q°= 0,经两级与非门后,使S仁0 ,这时有S1S0= 01 ,寄存器开始执行右移操作。

在移位过程中,因为Q3Q2、Q1、Q0中总有一个为0,因而能够维持S1S0=01状态,使右移操作持续进行下去°其移位情况如图题解6, 5, 1所示。

该电路能按固定的时序输出低电平脉冲,是一个四相时序脉冲产生电路。

-JT AAA TL幺I15、状态方程为儿⑷儿個)X(O24、解:74HC194功能由S1S0控制。

第六章存储器和可编程器件6.1 填空1、按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用 正负剩磁 来存储数据;而半导体存储器利用 器件的开关状态 来存储数据。

两者相比,前者一般容量较 大 ;而后者具有速度 快 的特点。

2、半导体存储器按功能分有 ROM 和 RAM 两种。

3、ROM 主要由 地址译码器 和 存储矩阵 两部分组成。

按照工作方式的不同进行分类,ROM 可分为 固定内容的ROM 、 PROM 和 EPROM 三种。

4、某EPROM 有8数据线,13位地址线,则其存储容量为 213×8 。

5、PLA 一般由 与ROM 、 或ROM 和 反馈逻辑网络 三部分组成。

6.2 D 0A 0D 1m(3,6,9,12,15)D 2A 1A 0D 3m(0,5,9,13)==∑=⋅=∑⎧⎨⎪⎪⎪⎩⎪⎪⎪ 6.3地址译码器A1A0D3 D2 D1 D0B1B0m 0m 156.4 1。

F Q Q Q Q Q Q Q F Q Q Q Q Q Q Q Q Q F Q Q 110212102210210210310=⋅+⋅+⋅=⋅⋅+⋅+⋅⋅=⋅⎧⎨⎪⎪⎩⎪⎪2、CP F1F2F36.5A AB BC C i-1i-1S i C i6.6 用PLA 实现BCD8421码十进制加法计数器和相应的显示译码电路。

D 1Q1Q1D2 Q2 Q2D3 Q3Q3D4Q4Q49 87654 3210a b c d e f ga b cdef g下面资料为赠送的地产广告语不需要的下载后可以编辑删除就可以,谢谢选择,祝您工作顺利,生活愉快!地产广告语1、让世界向往的故乡2、某沿河楼盘:生活,在水岸停泊3、一江春水一种人生4、某钱塘江边楼盘:面对潮流经典依旧5、海景房:站在家里,海是美景;站在海上,家是美景6、以山水为卖点的楼盘:山水是真正的不动产7、某城区的山腰上的楼盘:凌驾尊贵俯瞰繁华8、某地势较高的楼盘:高人,只住有高度的房子9、某学区房:不要让孩子输在起跑线上10、尾盘:最后,最珍贵11、回家就是度假的生活12、生命就该浪费在美好的事情上我们造城——2、我的工作就是享受生活——3、我家的客厅,就是我的生活名片——4、在自己的阳台看上海的未来——5、公园不在我家里我家住在公园里——6、这里的花园没有四季——7、***,装饰城市的风景——8、***,我把天空搬回家——9、房在林中,人在树下——10、生活,就是居住在别人的爱慕里——11、到〖星河湾〗看看好房子的标准——12、好生活在〖珠江〗——13、爱家的男人住〖百合〗城市岸泊:城市的岸泊,生活的小镇生活之美不缺少,在于发现情趣不在于奢华,在于精彩生活有了美感才值得思考……玫瑰庄园:山地生态,健康人生卓越地段,超大社区一种完整且完善的环境,像原生一样和谐原生景象自然天成人本理念精品建筑知名物业智能安防诚信为本实力铸造比华利山庄:海岸生活——引领世界的生活方式海岸生活——22公里的奢华海岸生活——高尚人生的序曲海岸生活——人与自然的融合苹果二十二院街:人文自然现代铺的蔓伸荣和山水美地:让世界向往的故乡香港时代:时代精英开拓未来领衔建筑,彰显尊贵绿地崴廉公寓:金桥40万平方米德国音乐艺术生活汇都国际:昆明都心,城市引擎财富之都风情之都梦幻之都文化之都商贸之都西部首座巨型商业之城颠峰商圈的原动力,缔造西部财富新领地新江湾城:绿色生态港国际智慧城新江湾城,一座承载上海新梦想的城区上海城投,全心以赴建设知识型,生态型花园城区风和日丽:入住准现楼,升值在望湾区大户,空中花园大格局下的西海岸市中心:市中心少数人的专属颠峰珍贵市中心的稀世名宅正中心城市颠峰领地颠峰勾勒稀世名宅繁华不落幕的居家风景地利皇者尽得先机稀世经典180席阳光国际公寓:阳光金桥来自纽约的生活蓝本钟宅湾:海峡西岸生态人居休闲商务区汇聚国际财富与人居梦想的绝版宝地二十一世纪是城市的世纪,二十一世纪也是海洋的世纪谁控制了海洋,谁就控制了一切站在蓝色海岸的前沿,开启一个新的地产时代东南门户海湾之心海峡西岸生态人居休闲商务区让所有财富的目光聚集钟宅湾,这里每一天都在创造历史上海A座(科维大厦):创富人生的黄金眼掘金上海!创富人生!远东大厦:花小公司的钱,做大公司的事未来城:无可挑战的优势无可限量的空间绿地集团:居住问题的答疑者,舒适生活的提案人茶马驿栈:精明置业时机享受附加值财富最大化雪山下的世外桃源茶马古道上千年清泉之乡金地格林春岸:城市精英的梦想家园繁华与宁静共存,阔绰身份不显自露建筑覆盖率仅20%,令视野更为广阔占据最佳景观位置,用高度提炼生活完美演绎自然精髓,谱写古城新篇章创新房型推陈出新,阔气空间彰显不凡365天的贴身护卫,阔度管理以您为尊金地格林小城:心没有界限,身没有界限春光永驻童话之城我的家,我的天下东渡国际:梦想建筑,建筑梦想齐鲁置业:传承经典,创新生活比天空更宽广的是人的思想创新远见生活嘉德中央公园:一群绝不妥协的居住理想家完成一座改变你对住宅想象的超越作品极至的资源整合丰富住家的生活内涵苛求的建造细节提升住家的生活品质地段优势,就是永恒价值优势设计优势,就是生活质量优势景观优势,就是生命健康优势管理优势,就是生活品味优势空中华尔兹:自然而来的气质,华尔兹的生活等级享受,没有不可逾越的极限所谓完美的习惯,是舒适空间的心情定格!临江花园:经典生活品质风景中的舞台美林别墅:源欧美经典纯自然空间住原味别墅赏园林艺术淡雅怡景温馨自然钱江时代:核心时代,核心生活核心位置创意空间优雅规划人文景观财富未来城市精神,自然风景,渗透私人空间泰达时尚广场:是球场更是剧场城市经济活力源时尚天津水舞中国未来都会休闲之居创意时尚天天嘉年华健康快乐新境界商旅新天地缔造好生意城市运营战略联盟,参与协作,多方共赢华龙碧水豪园:浪漫一次,相守一生东方莱茵:品鉴品位宜家宜人建筑一道贵族色彩品鉴一方美学空间品位一份怡然自得荡漾一股生命活力坐拥一处旺地静宅体会一种尊崇感受常青花园(新康苑):新康苑生活感受凌驾常规大非凡生活领域成功人士的生活礼遇拥有与自己身份地位相等的花园社区在属于自己的宴会餐厅里会宾邀朋只与自己品味爱好相同的成功人士为邻孩子的起步就与优越同步酒店式物管礼遇拥有[一屋两公园前后是氧吧]的美极环境水木清华:住在你心里福星惠誉(金色华府):金色华府,市府街才智名门——释放生命的金色魅力真正了解一个人,要看他的朋友,看他的对手。