超大规模集成电路设计导论:全定制设计方法

- 格式:ppt

- 大小:1.20 MB

- 文档页数:33

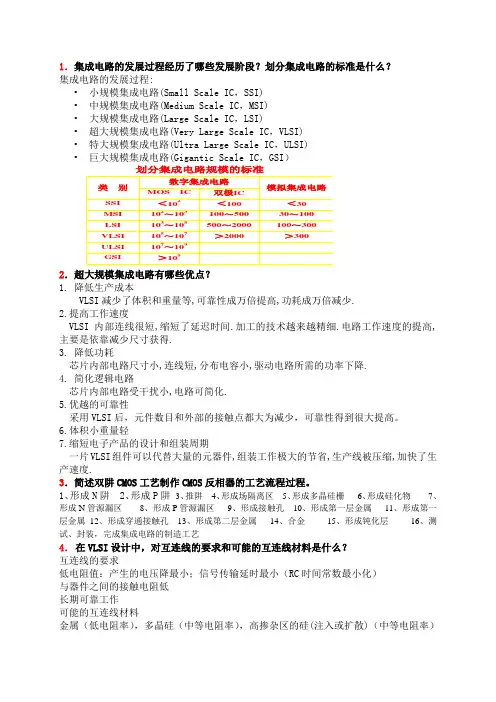

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

电子电路设计中的数字集成电路设计方法数字集成电路(Digital Integrated Circuit,简称DIC)设计方法在电子电路设计领域中扮演着至关重要的角色。

数字集成电路广泛应用于各种电子设备中,如计算机、通信设备、消费电子产品等。

本文将介绍几种常用的数字集成电路设计方法,并讨论其特点与应用。

一、全定制设计方法全定制设计方法是一种基于传统工艺的数字集成电路设计方法,它通过精确地定义电路的每个元件参数,将电路设计为完全定制化的形式。

在全定制设计方法中,设计师需要手动绘制电路原理图,并进行详细的手工布局和连线。

这种方法具有高度的灵活性和设计自由度,可以满足各种特定应用的需求。

然而,全定制设计方法需要投入大量人力与时间,成本较高,因此更适用于小批量、高性能的电路设计。

二、半定制设计方法半定制设计方法是介于全定制设计和可编程门阵列设计之间的一种设计方法。

在半定制设计方法中,设计师通过使用逻辑门库和标准元件库,将电路的逻辑功能和部分布局进行自定义,而其他部分则采用标准单元的形式。

这种方法兼具了全定制设计的灵活性和可编程门阵列设计的高效性,能够在满足设计需求的同时,有效地减少设计时间与成本。

半定制设计方法广泛应用于中小规模、低功耗的数字集成电路设计。

三、可编程门阵列(Programmable Gate Array,简称PGA)设计方法可编程门阵列设计方法是一种基于Field Programmable Gate Array (FPGA)的数字集成电路设计方法。

在可编程门阵列设计方法中,设计师通过在FPGA上进行逻辑配置,将电路设计实现为可编程的形式。

这种方法具有高度的灵活性和可重构性,能够适应快速变化的设计需求。

然而,相比于全定制设计和半定制设计方法,可编程门阵列设计方法在性能和功耗上存在一定的折中。

可编程门阵列设计方法主要应用于中小规模、低功耗的数字集成电路设计,以及快速原型验证与系统开发。

四、可重构计算机设计方法可重构计算机设计方法是一种基于可重构计算机架构的数字集成电路设计方法。

数字超大规模集成电路设计数字超大规模集成电路设计数字超大规模集成电路(VLSI)是一种特殊类型的集成电路,由数百万个晶体管构成,可用于各种应用,例如计算机处理器、数字信号处理器、存储器和网络芯片。

设计数字超大规模集成电路需要专业的知识和技术,严格的设计过程和流程可以确保电路的性能和可靠性达到最佳水平。

数字超大规模集成电路设计的主要步骤包括电路规划、逻辑设计、物理设计和验证等四个阶段。

下面将对这四个过程分别详细介绍。

1. 电路规划电路规划是设计数字超大规模集成电路的第一步,它需要确定电路的总体结构和功能。

在这个阶段,设计师需要与客户或团队成员讨论需求和预期的目标,以确定应满足的功能和性能要求。

电路规划需要在不同的层次上考虑电路的结构,例如芯片层、宏单元层、模块层和单元层,以确保整个电路都经过了全面的思考和验证。

2. 逻辑设计在电路规划阶段完成后,设计师需要开始进行逻辑设计,这是将电路的功能和结构转化为数字逻辑块的过程。

设计师可以使用各种电子设计自动化(EDA)工具来实现逻辑设计,通常使用硬件描述语言(HDL)来表示电路的行为和结构。

逻辑设计包括几个不同的步骤,例如:逻辑合成:将高层次的行为描述转化为门级或寄存器传输级别的等效电路。

时序分析:确保电路满足时序约束和时钟周期。

优化布局和布线:通过逻辑综合和布局布线工具优化电路,以实现更好的性能和功耗。

3. 物理设计物理设计阶段是将逻辑电路实现为实际电路的过程,包括立即设计、布局规划、布线、物理验证等。

立即设计:确定电路各个模块的精确位置,以及电路的层次和结构。

布局规划:根据立即设计结果生成电路的初始布局方案,包括放置模块、布线规划以及时钟树设计等。

布线:将布局好的模块进行线路连接,生成物理电路,并进行布线优化、电容和电感提取,确定线路的延迟等等。

物理验证:设计师对所生成的物理电路进行验证,包括逻辑验证、时序验证、数据库校验等,以确保电路的功能与预期相符,而且其性能达到标准。

目录摘要 (1)关键词 (1)Abstract (1)Key words (1)1 引言 (1)2 超大规模集成电路的设计要求 (1)3 超大规模集成电路的设计策略 (2)3.1层次性 (2)3.2模块化 (2)3.3规则化 (2)3.4局部化 (2)4 超大规模集成电路的设计方法 (3)4.1 全定制设计方法 (3)4.2 半定制设计方法 (4)4.3 不同设计方法的比较 (5)5 超大规模集成电路的设计步骤 (6)5.1 系统设计 (7)5.2 功能设计 (7)5.3 逻辑设计 (7)5.4 电路设计 (7)5.5 版图设计 (7)5.6 设计验证 (8)5.7 制造 (8)5.8 封装和测试 (8)6 超大规模集成电路的设计流程 (8)6.1 总体的设计流程 (8)6.1.1高层次综合 (8)6.1.2逻辑综合 (8)6.1.3 物理综合 (9)6.2 详细的设计流程 (9)7 超大规模集成电路的验证方法 (9)7.1 动态验证 (9)7.2 静态验证 (9)7.3 物理验证 (9)8 总结 (9)致谢 (10)参考文献 (10)超大规模集成电路网络工程专业学生孙守勇指导教师吴俊华摘要:随着集成电路的高速发展,集成电路的设计显得越来越重要,目前设计能力滞后于制造工艺已成为世界集成电路产业的发展现状之一。

为了明确超大规模集成电路设计的理想方法,首先对超大规模集成电路的设计要求进行了调查,然后对超大规模集成电路的设计策略进行了研究,探讨了超大规模集成电路的不同设计方法,并对不同的设计方法做出了比较,明确了超大规模集成电路的设计步骤及设计流程,最后探讨了超大规模集成电路的验证方法。

关键词:集成电路设计方法步骤Very Large Scale IntegrationStudent Majoring in Network Engineering Sun ShouyongTutor Wu JunhuaAbstract:With the high speed development of integrated circuit, the design of integrated circuit is becoming more and more important. At present, the design capacity behind manufacture technology has become one of the world's integrated circuit industry development current situation. In order to specify the ideal method of VLSI design, first of all, the requirements of VLSI was investigated, then, the design strategy of VLSI is studied. Discuss different methods of VLSI, and made a comparison of different methods. Clear and definite the design steps of very large scale integrated circuit and the design process, finally, discuss the validation method of very large scale integrated circuit.Key words:integrated circuit; design; method; step1引言自从1959年集成电路诞生以来,经历了小规模(SSI)、中规模(MSI)、大规模(LSI)的发展历程,目前已进入超大个规模(VLSI)和甚大规模集成电路(ULSI)阶段,集成电路技术的发展已日臻完善,集成电路芯片的应用也渗透到国民经济的各个部门和科学技术的各个领域之中,对当代经济发展和科技进步起到了不可估计的推动作用。

超大规模集成电路课程论文题目:超大规模集成电路的设计方法院系:xxxxxxxxx专业:xxxxxxxxxxxx年级:xxxxxxxxx学号:xxxxxxxxxxx姓名:xxxxxx指导老师:xxxxxxxxxx完成时间:xxxxxxxxxxx超大规模集成电路的设计方法作者:xxxx指导老师:xxxxxxxxxxxxxxxxx摘要:本文在概述超大规模集成电路设计步骤上,详细的论述了各种设计集成电路的方法,讨论了全定制法、标准单元设计方法、积木块设计方法、门阵列设计方法以及可编程逻辑器件设计方法的特点和适用范围。

关键词:集成电路;全制定法;标准单元设计法Abstracts:On the basis of VLSI design method, this thesis detailed expounds the methods of design of integrated circuits, discusses the custom law, full customization method, standard unit design method ,building block design ,gate array method and design method of programmable logic devices 's characteristics and applicability.Keywords: integrate circuit;full customization method;standard unit design method1 引言所谓集成电路就是将晶体管、电阻、电容、等各种电子元器件以相互联系的状态集成到半导体材料(主要是硅)或者绝缘体材料薄层片子上,再用一个管壳将其封装起来,构成一个完整的、具有一定功能的电路或系统。

自1959年以来,集成电路技术发生了惊人的变化。

超大规模集成电路设计方法学导论第二版课程设计项目背景随着半导体工艺和设计技术的不断进步,超大规模集成电路(Very Large Scale Integration,VLSI)已成为电子工业的主流技术之一。

在VLSI设计中,设计方法学起到至关重要的作用,可以提高设计效率、降低设计成本、提高设计质量和可重用性。

本课程旨在介绍VLSI设计方法学的基本原理和实践方法,为学生提供一种深入了解VLSI设计的能力和技能。

课程目标本课程旨在:•介绍VLSI设计的基本原理和实践方法;•培养学生的VLSI设计能力和技能;•提供学生参与VLSI设计项目的实践机会,了解VLSI产品开发和制造的全过程。

课程内容本课程包括以下主题:1.VLSI设计流程介绍VLSI设计的基本流程,包括开发需求、架构设计、逻辑设计、物理设计、验证和测试等环节。

2.VLSI设计工具介绍常用的VLSI设计工具,如EDA工具、仿真工具、物理设计工具等,并说明它们的使用方法和特点。

3.VLSI设计技术与方法介绍VLSI设计中的关键技术和方法,如低功耗设计、时序约束、功耗分析等,并通过实例分析加深理解。

4.VLSI设计案例分析选取一些典型的VLSI设计案例,介绍其设计原理和实现技术,并引导学生进行分析和讨论。

课程设计课程设计要求学生选择一个VLSI设计项目进行研究和实践,包括以下环节:1.项目选择学生从给定的VLSI设计项目中选择一个项目,并列出项目的开发需求、设计目标和约束条件。

2.架构设计学生进行项目的架构设计,确定项目的功能模块和接口,并绘制设计图。

3.逻辑设计学生进行项目的逻辑设计,编写硬件描述语言(HDL)代码,并进行仿真和验证。

4.物理设计学生进行项目的物理设计,包括布局设计和布线设计,并进行功耗和时序分析。

5.验证和测试学生进行项目的验证和测试,包括模拟验证、板级测试和芯片级测试等环节。

总结本课程通过理论学习和实践项目相结合的方式,培养学生的VLSI设计能力和技能,提高学生的综合素质和创新能力。

超大规模集成电路设计导论课程设计介绍超大规模集成电路(Very Large-Scale Integration,简称VLSI)是指将许多电子器件、电子元件和电路系统高度集成在一起,形成一个功能强大的芯片。

VLSI 技术是电子信息科学与技术的重要分支之一,应用范围广泛,从计算机芯片到计算机网络、通信系统、控制系统等领域都有广泛的应用。

本文将介绍超大规模集成电路设计导论课程设计的相关内容。

课程设计任务超大规模集成电路设计导论课程设计的任务是设计一个最小的超大规模集成电路芯片,实现指定的功能。

学生需完成以下任务:1.设计一个基于MOSFET电路的逻辑电路。

学生需要掌握MOS场效应管的基本工作原理,了解CMOS电路的基本操作和管路的结构。

2.进行电路级仿真。

学生需要使用常用的电路设计软件进行电路仿真,如HSpice、Cadence等。

3.进行物理级设计。

学生需要熟悉并掌握芯片物理设计的相关知识,包括版图设计、布线、电源分配等。

4.进行芯片测试。

学生需要设计并实现相应的测试电路,并进行芯片测试,以验证芯片的正确性和稳定性。

设计流程超大规模集成电路设计导论课程设计的设计流程可以分为以下几个步骤:步骤一:确定电路功能在超大规模集成电路设计导论课程设计中,首先需要确定电路的功能。

学生需要根据课程要求,确定芯片的功能模块,例如逻辑门、存储器等。

步骤二:电路设计在确定电路功能之后,学生需要进行电路设计。

主要的工作包括选择电路拓扑结构,确定器件大小和参数等。

步骤三:电路仿真完成电路设计后,学生需要进行电路仿真。

通过仿真可以预测电路的性能和工作过程,根据仿真结果进行电路调整和参数优化。

步骤四:物理级设计完成电路仿真之后,需要进行物理级设计。

主要的工作包括版图设计、布线和电源分配等。

学生需要熟练运用芯片设计软件,如Cadence等。

步骤五:芯片制造完成物理级设计后,学生需要将设计好的芯片提交到芯片制造厂家进行生产加工。

学生需要了解芯片制造的相关知识和技术,如光刻工艺、腐蚀工艺等。

IC设计流程之实现篇——全定制设计要谈IC设计的流程,⾸先得搞清楚IC和IC设计的分类。

集成电路芯⽚从⽤途上可以分为两⼤类:通⽤IC(如CPU、DRAM/SRAM、接⼝芯⽚等)和专⽤IC(ASIC)(Application Specific Integrated Circuit),ASIC是特定⽤途的IC。

从结构上可以分为数字IC、模拟IC和数模混合IC三种,⽽SOC(System On Chip,从属于数模混合IC)则会成为IC设计的主流。

从实现⽅法上IC设计⼜可以分为三种,全定制(full custom)、半定制(Semi-custom)和基于可编程器件的IC设计。

全定制设计⽅法是指基于晶体管级,所有器件和互连版图都⽤⼿⼯⽣成的设计⽅法,这种⽅法⽐较适合⼤批量⽣产、要求集成度⾼、速度快、⾯积⼩、功耗低的通⽤IC或ASIC。

基于门阵列(gate-array)和标准单元(standard-cell)的半定制设计由于其成本低、周期短、芯⽚利⽤率低⽽适合于⼩批量、速度快的芯⽚。

最后⼀种IC 设计⽅向,则是基于PLD或FPGA器件的IC设计模式,是⼀种“快速原型设计”,因其易⽤性和可编程性受到对IC制造⼯艺不甚熟悉的系统集成⽤户的欢迎,最⼤的特点就是只需懂得硬件描述语⾔就可以使⽤EDA⼯具写⼊芯⽚功能。

从采⽤的⼯艺可以分成双极型(bipolar),MOS和其他的特殊⼯艺。

硅(Si)基半导体⼯艺中的双极型器件由于功耗⼤、集成度相对低,在近年随亚微⽶深亚微⽶⼯艺的的迅速发展,在速度上对MOS管已不具优势,因⽽很快被集成度⾼,功耗低、抗⼲扰能⼒强的MOS管所替代。

MOSFET⼯艺⼜可分为NMOS、PMOS和CMOS三种;其中CMOS⼯艺发展已经⼗分成熟,占据IC市场的绝⼤部分份额。

GaAs器件因为其在⾼频领域(可以在0.35um下很轻松作到10GHz)如微波IC中的⼴泛应⽤,其特殊的⼯艺也得到了深⼊研究。

⽽应⽤于视频采集领域的CCD传感器虽然也使⽤IC⼀样的平⾯⼯艺,但其实现和标准半导体⼯艺有很⼤不同。

EDA重点(填空题、解答题、论述题、程序题)以下内容完全根据老师给的重点总结得到,如有不周,敬请谅解第一章VLSI概述1、微电子专业词汇IC(Integrated Circuit): 集成电路VLSI (Very Large Scale Integration):超大规模集成电路VDSM(Very Deep Sub-Micron): 超深亚微米(<=0.25um)ASIC(Application Specific Integrated Circuit): 专用集成电路ASSP(Application Specific Standard Products): 专用标准产品EDA(Electronic Design Automation):电子设计自化ESDA(Electronic System Design Automation): 电子系统设计自动化技术IP(Intellectual Property):指知识产权、著作权SOC(System on a chip): 片上系统(基于IP的半定制设计方法)PGA(Pin Grid Array) :阵栅(网格)阵列BGA(Ball Grid Array): 球栅(网格)阵列EDIF(Electronic Design Interchange Format):电子设计网表格式NRE(Non-Recurring Engineering):非重复性工程成本或一次性工程成本GA(Gate Array): 门阵列P&R(Place and Route): 布局布线LVDS(Low power differential signaling):低电压差分信号ESD(Electro-Static discharge):静电释放EMI(Electro-magnetic Interference) :电磁干扰Foundry:工艺生产线RTL(register Transfer lever):寄存器传输级ISP (In-System Programmability ):在系统可编程SOPC(System on programmable chip): 可编程片上系统2、封装的主要类型:从扦孔形(THP)向表面按装形式(SMP)发展,到现在的MCM(Multi-Chip Module)多芯片组件封装。

集成电路设计中的全定制电路设计全定制电路设计是集成电路设计的一个重要分支,它与传统的标准细胞库设计方法相比,具有更大的灵活性和更高的性能。

本文将详细介绍全定制电路设计的基本概念、设计流程、优势以及应用。

1. 全定制电路设计的基本概念全定制电路设计,顾名思义,就是根据特定的应用需求,为特定的功能设计电路。

与标准细胞库设计方法不同,全定制电路设计不依赖于预先定义的单元库,而是完全根据设计的实际需求来定制电路。

这种设计方法可以在保证性能的同时,最大限度地减少电路的面积和功耗。

2. 全定制电路设计的设计流程全定制电路设计通常包括以下几个基本步骤:2.1 需求分析在需求分析阶段,设计师需要充分理解电路的功能需求,包括输入输出信号、工作频率、功耗等关键参数。

这一步是整个设计过程的基础,直接关系到后续电路设计的成败。

2.2 逻辑设计在逻辑设计阶段,设计师需要根据需求分析的结果,设计出满足功能要求的逻辑电路。

这一步通常使用硬件描述语言(HDL)进行描述,如Verilog或VHDL。

2.3 电路合成在电路合成阶段,需要将逻辑设计阶段得到的描述转化为具体的电路结构。

这一步涉及到电路的优化和布局,目的是为了在满足性能要求的同时,尽可能减少电路的面积和功耗。

2.4 仿真验证在仿真验证阶段,需要使用专门的仿真工具对设计好的电路进行功能和性能的验证。

这一步是非常重要的,因为它可以帮助设计师及时发现并修复设计中的错误。

2.5 物理设计在物理设计阶段,需要将电路合成阶段得到的结构映射到具体的集成电路工艺上,进行版图绘制和后端处理。

这一步需要考虑到电路的布局、布线、功耗分布等因素,以保证电路在实际制造过程中的性能和可靠性。

3. 全定制电路设计的优势全定制电路设计具有以下几个显著的优势:3.1 性能优化由于全定制电路设计是完全根据实际需求来定制电路,因此可以在保证功能的同时,实现最优的性能。

这与标准细胞库设计方法相比,可以显著提高电路的运行速度和效率。

集成电路的几种设计方法有哪些

集成电路的几种设计方法主要有以下几种:

1. 全定制设计:完全根据特定要求和设计目标进行设计,可以实现高度的定制化,但设计周期长,成本高。

2. 半定制设计:通过在设计阶段选择合适的标准库和模块来设计电路,可以实现部分定制化,设计周期相对较短,成本也相对较低。

3. 可编程门阵列(FPGA)设计:使用可编程逻辑门阵列来实现电路设计,可以通过配置逻辑门的连接关系来实现不同的功能,具有灵活性和可重配置性。

4. 系统级设计(ESL):在高级抽象层次上进行设计,利用高级编程语言和工具来描述和实现电路功能,可以提高设计效率和可靠性。

5. 模拟集成电路设计:主要用于处理模拟信号的电路设计,常用的方法包括电路仿真、参数优化等。

6. 数字集成电路设计:主要用于处理数字信号的电路设计,常用的方法包括逻辑门设计、时序设计等。

7. 射频集成电路设计:主要用于射频信号的电路设计,常用的方法包括匹配网

络设计、滤波器设计等。

以上是常见的集成电路设计方法,不同的方法在不同的应用场景下有各自的优劣势。

超大规模集成电路设计方法学导论第二版课程设计1. 课程介绍超大规模集成电路设计方法学导论第二版是电子信息工程专业本科生必修课程,旨在培养学生掌握超大规模集成电路设计方法学的基本理论、方法和技术,以及能够利用现代电子设计自动化工具进行VLSI系统(数字、模拟、混合)的建模和设计的实践能力。

本次课程设计旨在通过实际操作,巩固和加深学生对于超大规模集成电路设计的理解,并培养学生独立解决工程问题的能力。

2. 实验内容本次课程设计实验内容包括:1.RTL级Verilog HDL电路设计:根据要求实现电路功能模块的RTL级Verilog HDL描述;2.仿真验证:利用Verilog仿真工具验证模块功能的正确性;3.门级综合:将RTL级Verilog HDL描述的电路模块综合成门级网表,并分析电路的逻辑开销和时序性能;4.物理布局与布线:根据门级网表进行物理布局与布线;5.电路后仿真:根据布局与布线结果利用仿真工具进行电路后仿真。

3. 实验设计3.1 实验环境本次课程设计中,需要使用的软硬件环境如下:1.计算机一台:CPU至少为i5,内存至少为8G;2.Verilog仿真工具:ModelSim;3.门级综合工具:Design Compiler;4.物理布局与布线工具:ICC;5.储存介质:U盘或移动硬盘。

3.2 实验步骤1.阅读并理解课程设计要求;2.根据要求,设计电路功能模块的RTL级Verilog HDL描述;3.利用Verilog仿真工具进行功能验证;4.利用Design Compiler完成门级综合,并分析电路的逻辑开销和时序性能;5.根据门级网表进行物理布局与布线;6.利用仿真工具进行电路后仿真;7.完成实验报告及实验过程记录。

3.3 实验要求1.完成电路功能模块的RTL级Verilog HDL描述,代码格式规范,注释清晰;2.完成Verilog仿真验证,仿真时需要指定仿真程序、仿真数据,并正确验证电路功能的正确性和性能;3.完成门级综合和物理布局与布线,分析电路逻辑开销和时序性能;4.完成电路后仿真,验证电路最终设计的正确性和性能;5.完成实验报告,并对实验过程进行记录。