全定制集成电路设计流程

- 格式:ppt

- 大小:449.50 KB

- 文档页数:25

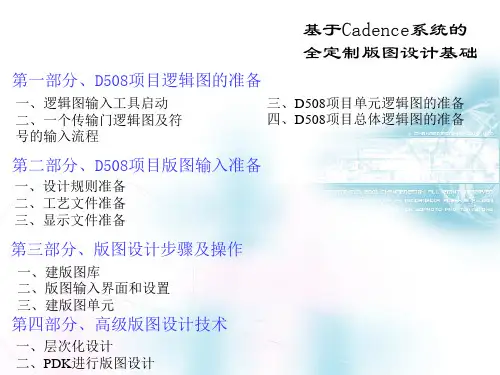

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

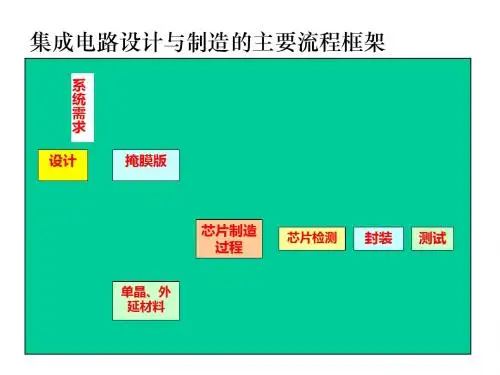

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

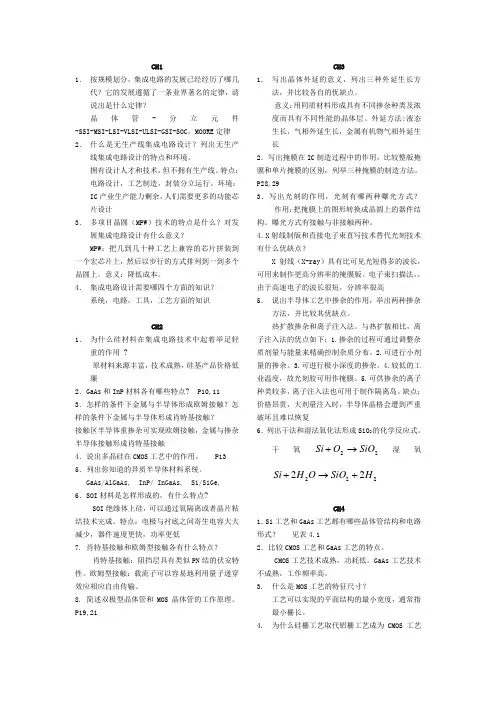

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

asic 芯片ASIC芯片(Application-Specific Integrated Circuit)是一类专用集成电路芯片,也称为定制芯片。

相比于通用集成电路(如处理器、存储器等),ASIC芯片是根据特定的应用需求而设计的,因此能够提供更高的性能和更低的功耗。

ASIC芯片在各个领域都得到广泛应用,包括通信、计算机、工业控制、汽车、医疗等。

下面将从设计流程、应用案例和未来发展趋势三个方面来介绍ASIC芯片。

首先是ASIC芯片的设计流程。

ASIC芯片的设计是一个复杂的过程,通常分为前端设计和后端设计两个阶段。

前端设计主要包括功能设计、电路设计和逻辑验证。

功能设计是根据需求规格书确定芯片的功能模块和接口,并进行功能分析;电路设计则是根据功能要求,设计电路的结构和参数,如时钟、存储器、逻辑门等;逻辑验证是通过仿真和验证工具对设计进行全面测试,以确保功能的正确性。

后端设计主要包括物理设计、布局设计和版图设计。

物理设计是将逻辑电路映射到实际的物理器件,进行数电转换、时序优化等操作;布局设计则是确定各个电路模块的位置和相互连接方式;版图设计则是将布局设计结果转化为最终的芯片版图。

完成设计后,还需要进行流片和封装测试。

流片是指将版图发送给芯片制造企业,进行样片生产;封装测试则是将芯片封装为最终的芯片模块,并经过各种测试和验收,确保芯片的可靠性和稳定性。

其次是ASIC芯片的应用案例。

ASIC芯片广泛应用于各个领域,以下以通信和计算机领域为例介绍两个典型的应用案例。

在通信领域,ASIC芯片被广泛用于移动通信设备中,如手机、路由器和基站等。

它们能够提供高效的信号处理、数据传输和接口控制功能,满足不同通信标准和需求。

例如,LTE芯片可以实现高速无线数据传输,提供更快的网络连接速度;而基站芯片能够实现大规模的无线通信覆盖,提供更好的通信服务质量。

在计算机领域,ASIC芯片被广泛用于数据中心和云计算设备中。

它们能够提供高性能的计算、存储和网络功能,满足大规模数据处理和分析的需求。

–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色–集成电路设计流程与EDA软件•半定制设计流程•全定制设计流程–选择EDA设计工具的原则–主要的EDA Vendor工具特色迭代性2与3可互换LVS/DRC1. 设计输入硬件描述语言设计输入,任何文本编辑工具–如:Ultraedit (IDM Computer Solutions 公司); vi (Linux 文本编辑工具)–仿真器自带编辑器…计规范检查:LEDA (Synopsys )-增强了设计人员检查HDL 代码的能力,包括可综合性,可仿真性、可测试性和可重用性Logic Design Flow2、逻辑综合–Synopsys:Design Compiler;380到500个综合库198890 %ASIC设计师选用1年的license 83万RMBLogic Design Flowdesign entryPhysical Design FlowDesign & timing SetupFloor Planning布图规划:包括裸片大小的规划、I/O规划、电源规划、大量硬核或模块(hard core、block)的规划等,是对芯片内部结构的完整规划和设计。

布图规划的合理与否直接关系到芯片的时序收敛、布线通畅。

CTSCTS步骤中,需要对设计的时钟分布有大体的了解,buffer tree的级数,时钟的skew等分为全局布线(global routing )、详细布线(detailrouting )和布线修正(search and repair )。

RoutingDesign For Manufacturability(DFM)保证芯片能被foundry正确制造:1.天线效应修补:如果某一层的一个信号线过长,在制造过程中可能会吸收大量的电荷,从而造成栅氧化层击穿。

一般工具软件会使信号跳层或者插入反偏二极管来消除;2.单孔变多孔:布线完成后不同层的金属在连接处都只用了单一孔来进行连接,这样接触电阻大,而且如果制造出问题时容易断路。

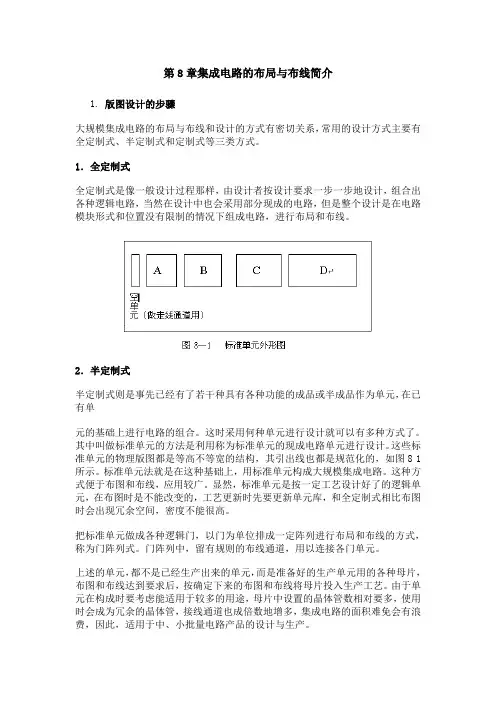

第8章集成电路的布局与布线简介1.版图设计的步骤大规模集成电路的布局与布线和设计的方式有密切关系,常用的设计方式主要有全定制式、半定制式和定制式等三类方式。

1.全定制式全定制式是像一般设计过程那样,由设计者按设计要求一步一步地设计,组合出各种逻辑电路,当然在设计中也会采用部分现成的电路,但是整个设计是在电路模块形式和位置没有限制的情况下组成电路,进行布局和布线。

2.半定制式半定制式则是事先已经有了若干种具有各种功能的成品或半成品作为单元,在已有单元的基础上进行电路的组合。

这时采用何种单元进行设计就可以有多种方式了。

其中叫做标准单元的方法是利用称为标准单元的现成电路单元进行设计。

这些标准单元的物理版图都是等高不等宽的结构,其引出线也都是规范化的,如图8 1所示。

标准单元法就是在这种基础上,用标准单元构成大规模集成电路。

这种方式便于布图和布线,应用较广。

显然,标准单元是按一定工艺设计好了的逻辑单元,在布图时是不能改变的,工艺更新时先要更新单元库,和全定制式相比布图时会出现冗余空间,密度不能很高。

把标准单元做成各种逻辑门,以门为单位排成一定阵列进行布局和布线的方式,称为门阵列式。

门阵列中,留有规则的布线通道,用以连接各门单元。

上述的单元,都不是已经生产出来的单元,而是准备好的生产单元用的各种母片,布图和布线达到要求后,按确定下来的布图和布线将母片投入生产工艺。

由于单元在构成时要考虑能适用于较多的用途,母片中设置的晶体管数相对要多,使用时会成为冗余的晶体管,接线通道也成倍数地增多,集成电路的面积难免会有浪费,因此,适用于中、小批量电路产品的设计与生产。

3.定制方式定制方式的设计是把各种基本逻辑单元事先设计完好,形成独立的功能单元,放在库中存储,设计时调出功能单元组合成各种电路。

这些功能单元也可以是寄存器、算数逻辑单元、存储器等,对形状也没有统一的要求。

这种设计法也叫通用单元法或积木块法。

不同的设计方法有不同的布局与布线要求,相应地,在利用计算机自动设计时需要采取不同的计算方法和程序。

全定制电路设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!全定制电路设计流程详解在电子工程领域,全定制电路设计是一种常见的方法,尤其适用于高性能、低功耗和特殊应用的集成电路设计。

集成电路设计中的全定制电路设计全定制电路设计是集成电路设计的一个重要分支,它与传统的标准细胞库设计方法相比,具有更大的灵活性和更高的性能。

本文将详细介绍全定制电路设计的基本概念、设计流程、优势以及应用。

1. 全定制电路设计的基本概念全定制电路设计,顾名思义,就是根据特定的应用需求,为特定的功能设计电路。

与标准细胞库设计方法不同,全定制电路设计不依赖于预先定义的单元库,而是完全根据设计的实际需求来定制电路。

这种设计方法可以在保证性能的同时,最大限度地减少电路的面积和功耗。

2. 全定制电路设计的设计流程全定制电路设计通常包括以下几个基本步骤:2.1 需求分析在需求分析阶段,设计师需要充分理解电路的功能需求,包括输入输出信号、工作频率、功耗等关键参数。

这一步是整个设计过程的基础,直接关系到后续电路设计的成败。

2.2 逻辑设计在逻辑设计阶段,设计师需要根据需求分析的结果,设计出满足功能要求的逻辑电路。

这一步通常使用硬件描述语言(HDL)进行描述,如Verilog或VHDL。

2.3 电路合成在电路合成阶段,需要将逻辑设计阶段得到的描述转化为具体的电路结构。

这一步涉及到电路的优化和布局,目的是为了在满足性能要求的同时,尽可能减少电路的面积和功耗。

2.4 仿真验证在仿真验证阶段,需要使用专门的仿真工具对设计好的电路进行功能和性能的验证。

这一步是非常重要的,因为它可以帮助设计师及时发现并修复设计中的错误。

2.5 物理设计在物理设计阶段,需要将电路合成阶段得到的结构映射到具体的集成电路工艺上,进行版图绘制和后端处理。

这一步需要考虑到电路的布局、布线、功耗分布等因素,以保证电路在实际制造过程中的性能和可靠性。

3. 全定制电路设计的优势全定制电路设计具有以下几个显著的优势:3.1 性能优化由于全定制电路设计是完全根据实际需求来定制电路,因此可以在保证功能的同时,实现最优的性能。

这与标准细胞库设计方法相比,可以显著提高电路的运行速度和效率。

I C设计流程之实现篇——全定制设计要谈IC设计的流程,首先得搞清楚IC和IC设计的分类。

集成电路芯片从用途上可以分为两大类:通用IC(如CPU、DRAM/SRAM、接口芯片等)和专用IC(ASIC)(Application Specific Integrated Circuit),ASIC是特定用途的IC。

从结构上可以分为数字IC、模拟IC和数模混合IC三种,而SOC (System On Chip,从属于数模混合IC)则会成为IC设计的主流。

从实现方法上IC设计又可以分为三种,全定制(full custom)、半定制(Semi-custom)和基于可编程器件的IC设计。

全定制设计方法是指基于晶体管级,所有器件和互连版图都用手工生成的设计方法,这种方法比较适合大批量生产、要求集成度高、速度快、面积小、功耗低的通用IC或ASIC。

基于门阵列(gate-array)和标准单元(standard-cell)的半定制设计由于其成本低、周期短、芯片利用率低而适合于小批量、速度快的芯片。

最后一种IC设计方向,则是基于PLD或FPGA器件的IC设计模式,是一种“快速原型设计”,因其易用性和可编程性受到对IC制造工艺不甚熟悉的系统集成用户的欢迎,最大的特点就是只需懂得硬件描述语言就可以使用EDA工具写入芯片功能。

从采用的工艺可以分成双极型(bipolar),MOS和其他的特殊工艺。

硅(Si)基半导体工艺中的双极型器件由于功耗大、集成度相对低,在近年随亚微米深亚微米工艺的的迅速发展,在速度上对MOS管已不具优势,因而很快被集成度高,功耗低、抗干扰能力强的MOS管所替代。

MOSFET工艺又可分为NMOS、PMOS和CMOS三种;其中CMOS工艺发展已经十分成熟,占据IC市场的绝大部分份额。

GaAs器件因为其在高频领域(可以在0.35um 下很轻松作到10GHz)如微波IC中的广泛应用,其特殊的工艺也得到了深入研究。