SilvacoTCAD器件仿真01

- 格式:ppt

- 大小:2.81 MB

- 文档页数:84

9SilvacoTCAD器件仿真模块及器件仿真流程Silvaco TCAD是一种广泛使用的集成电路(IC)设计和仿真工具,用于开发和研究半导体器件。

它提供了一套完整的器件仿真模块,可以帮助工程师设计、优化和验证各种半导体器件的性能。

本文将介绍几个常用的Silvaco TCAD器件仿真模块,并提供一个简要的器件仿真流程。

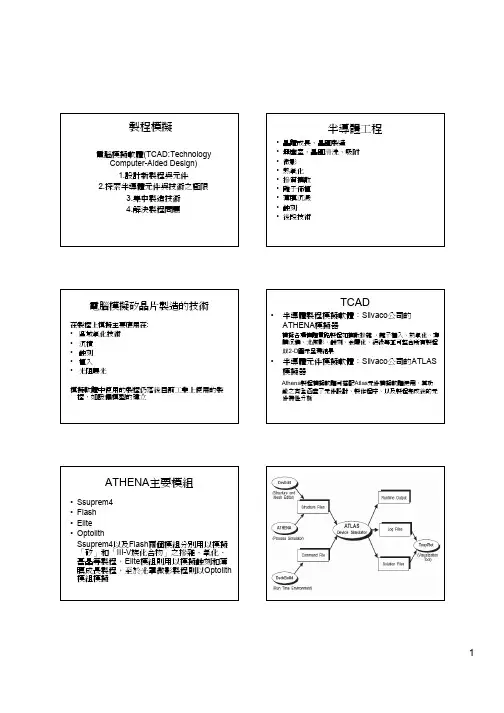

1. ATHENA模块:ATHENA是Silvaco TCAD的物理模型模拟引擎,用于模拟器件的结构和物理特性。

它可以通过解决泊松方程、电流连续性方程和能带方程等来计算电子和空穴的分布、电场和电势等物理量。

ATHENA支持多种材料模型和边界条件,可以准确地模拟各种器件结构。

2. ATLAS模块:ATLAS是Silvaco TCAD的设备模拟引擎,用于模拟半导体器件的电学和光学特性。

它可以模拟器件的电流-电压特性、载流子分布、能量带结构和光电特性等。

ATLAS支持各种器件类型,如二极管、MOSFET、BJT和太阳能电池等。

3. UTILITY模块:UTILITY是Silvaco TCAD的实用工具模块,用于处理和分析仿真结果。

它提供了各种数据可视化、数据处理和数据导出功能,帮助工程师分析和优化器件性能。

UTILITY还可以用于参数提取和模型校准,以改进模拟的准确性。

接下来是一个简要的Silvaco TCAD器件仿真流程:2. 设置模拟参数:在进行仿真之前,需要设置模拟所需的参数,如材料参数、边界条件、物理模型和仿真选项等。

可以使用Silvaco TCAD的参数设置工具来设置这些参数。

3. 运行ATHENA模拟:使用ATHENA模块进行结构模拟,通过求解泊松方程和连续性方程,计算出电子和空穴的分布、电场和电势等物理量。

可以使用Silvaco TCAD的命令行界面或图形用户界面来运行ATHENA模拟。

4. 运行ATLAS模拟:使用ATLAS模块进行设备模拟,模拟器件的电学和光学特性。

ATLAS模块可以计算器件的电流-电压特性、载流子分布、能量带结构和光电特性等。

ATHENA模擬LOCOS隔離結構初使結構是先沉積二氧化矽在沉積氮化矽,接著蝕刻左邊露出矽.矽被蝕刻以形成嵌壁式氧化層,此結構進行90分鐘,1000℃的水蒸氣氧化.在這個結構中也顯示了鳥嘴的形狀隨時間演變的情形等向性蝕刻因各方向蝕刻速率相當而有明顯的底切(undercut)現象,隨著蝕刻時間的加長其蝕刻結果(左圖)非等向性蝕刻具非等向性的蝕刻製程稱之為Ion Milling,在較長時間的蝕刻後會有輕微的底切出現(右圖)啟動Deckbuild改變工作目錄至自己電腦的資料夾command:line•定義格子Grid形成網格Mesh•Grid的多寡與模擬精確及模擬時間有關command:initialize•parametersone.d、two.d、auto指定模擬計算過程的維度•語法init two.d呼叫視覺化軟體Tonyplot假設欲以60keV硼植入,且已知植入peak約•Mesh:triangular mesh•Edges:sides of trianglesTonyplot:plot menuCommand:Deposit •Material材料參數:SILICON,OXIDE, OXYNITRIDE,NITRIDE,POLYSILICON, ALUMINUM,BARRIER,TUNGSTEN, TITANIUM,PLATINUM,WSIX,TISIX, PTSIX,PHOTORESIST,ALGAAS, INGAAS,SIGE,INP•User defined:MATERIAL=<c>•Thickness(μm):指定沉積層的厚度Thickness=<n>•EXAMPLESDEPOSIT OXIDE THICK=0.1DIVISIONS=4deposits a conformal layer of silicon dioxide,1000Angstroms thick, on the surface of the simulation structure.It will contain4vertical grid points.DEPOSIT MATERIAL=BPSG THICKNESS=0.1DIV=6C.BORON=1e20C.PHOS=1e20deposits a layer of a user defined material BPSG doped with boron and phosphorusDEPOSIT NITRIDE THICK=0.3DY=0.1YDY=0.3DIVIS=10•LEFT,RIGHT,ABOVE,and BELOW:配合參數P1.X,P1.Y,P2.X,and P2.Y所指定之區域進行蝕刻•P1.X,P1.Y,P2.X,and P2.Y:P1參數為平行或垂直線配合上下左右參數使用,P2參數為指定蝕刻角度etch poly right p1.x=0.3•Thickness:蝕刻厚度Exercise•將上圖SiO2的尾巴去除•先以Tonyplot→Tools→Probe訂出座標•以Etch指令進行蝕刻command:structure struct mirror leftcommand:stretch•針對上例Fig.2-22閘極長度為0.6微米,stretch指令提供增長閘極長度的功能•parameters •Stretch length(μm):設定伸展長度length=<n>STRETCH LENGTH=1.8Grid Divisions、Grid spacing:設定伸展區域的格子層數及間隔division=<n>spacing=<n>•也可經由STRETCH.VAL,X.VAL,Y.VAL達到所要的伸展長度STRETCH OXIDE X.VAL=2.3\Tonyplot→Display→製作連續播放Exercise。

§4 工艺及器件仿真工具SILVACO-TCAD本章将向读者介绍如何使用SILVACO公司的TCAD工具ATHENA来进行工艺仿真以及ATLAS来进行器件仿真。

假定读者已经熟悉了硅器件及电路的制造工艺以及MOSFET和BJT 的基本概念。

4.1 使用ATHENA的NMOS工艺仿真4.1.1 概述本节介绍用ATHENA创建一个典型的MOSFET输入文件所需的基本操作。

包括:a. 创建一个好的仿真网格b. 演示淀积操作c. 演示几何刻蚀操作d. 氧化、扩散、退火以及离子注入e. 结构操作f. 保存和加载结构信息4.1.2 创建一个初始结构1 定义初始直角网格a. 输入UNIX命令:deckbuild-an&,以便在deckbuild交互模式下调用ATHENA。

在短暂的延迟后,deckbuild主窗口将会出现。

如图4.1所示,点击File目录下的Empty Document,清空DECKBUILD文本窗口;图4.1 清空文本窗口b. 在如图4.2所示的文本窗口中键入语句go Athena ;图4.2 以“go athena”开始接下来要明确网格。

网格中的结点数对仿真的精确度和所需时间有着直接的影响。

仿真结构中存在离子注入或者形成PN结的区域应该划分更加细致的网格。

c. 为了定义网格,选择Mesh Define菜单项,如图4.3所示。

下面将以在0.6μm×0.8μm 的方形区域内创建非均匀网格为例介绍网格定义的方法。

图4.3 调用ATHENA网格定义菜单2 在0.6μm×0.8μm的方形区域内创建非均匀网格a. 在网格定义菜单中,Direction(方向)栏缺省为X;点击Location(位置)栏并输入值0;点击Spacing(间隔)栏并输入值0.1;b. 在Comment(注释)栏,键入“Non-Uniform Grid(0.6um x 0.8um)”,如图4.4所示;c. 点击insert键,参数将会出现在滚动条菜单中;图4.4 定义网格参数图 4.5 点击Insert键后d. 继续插入X方向的网格线,将第二和第三条X方向的网格线分别设为0.2和0.6,间距均为0.01。

[SILVACOATLAS]a-IGZO薄膜晶体管⼆维器件仿真(01)最近因为肺炎的缘故,宅在家⾥不能出门,就翻了下⼀些资料,刚好研究⽅向是这个,就简单研究了下。

参考资料主要如下:1.《半导体⼯艺和器件仿真软件Silvaco TCAD实⽤教程》唐龙⾕ 20142.《长安⼤学半导体⼯艺与器件仿真指导书》张林 2015引⽤本科时社团⼀姐的⼀句话:学习PS的精髓在于毁图。

个⼈浅见,学习仿真的话还是要根据实例拆解分析⽐较快。

重复,我是新⼿,只是个⼈浅见。

# (c) Silvaco Inc., 2019# This example demonstrates simulation of amorphous IGZO (indium galium# zinc oxide) TFT. Here we reproduce the results from:## Fung, T., Chuang, C., Chen, C., Katsumi, A., Cottle, R., Townsend, M.,# Kumomi, H., and Kanicki, J., "Two-dimensional numerical simulation of# radio frequency sputter amorphous In-Ga-Zn-O thin-film transistors",# J. Appl. Phys., V. 106, pp. 084511-1 through 084511-10.## Comparisons with experiment are included.## This first part of the input deck simulates Id-Vg.#go atlasmesh width=180 outf=tftex10_1.str master.outx.m l=0 s=0.25x.m l=40 s=0.25y.m l=0 s=0.0005y.m l=0.02 s=0.0005y.m l=0.12 s=0.005#(划分⽹格)# The device is composed of a 20 nm layer of IGZO deposited# 100 nm oxide on a n++ substrate that acts as the gate.#region num=1 material=igzo y.min=0 y.max=0.02region num=2 material=sio2 y.min=0.02 y.max=0.12#(定义材料)elec num=1 name=gate bottomelec num=2 name=source y.max=0.0 x.min=0.0 x.max=5.0elec num=3 name=drain y.max=0.0 x.min=35.0 x.max=40.0#(定义电极)# We define the gate as N.POLY. This pins the gate workfunction# to the conduction band edge of silicon.#contact num=1 n.poly## We also define a workfunction for the source and drain that# is very close to the conduction edge. In the reference the# authors observed that without a workfunction the results for# ohmic boundaries were not significantly different than the# Schottky model.#contact num=2 workf=4.33contact num=3 workf=4.33#(定义接触条件)models fermi## Key to the characterization of amorphous materials is the# definition of the states within the band gap.#defects nta=1.55e20 ntd=1.55e20 wta=0.013 wtd=0.12 \nga=0.0 ngd=6.5e16 egd=2.9 wgd=0.1 \sigtae=1e-15 sigtah=1e-15 sigtde=1e-15 sigtdh=1e-15 \siggae=1e-15 siggah=1e-15 siggde=1e-15 siggdh=1e-15 \dfile=tftex10_don.dat afile=tftex10_acc.dat numa=128 numd=64#(定义缺陷分布)# From here we simply extract the Id-Vg characteristic#solve initsolve prev#solve vdrain=0.1save outf=tftex10_0.strlog outf=tftex10_1a.logsolve vgate=0 vstep=-0.1 vfinal=-5 name=gatelog off#load inf=tftex10_0.str mastersolve prevlog outf=tftex10_1b.logsolve vstep=0.2 vfinal=20.0 name=gate## And we compare the simulation with experimental data reported in# the reference.#tonyplot -overlay tftex10_1a.log tftex10_1b.log tftex10_1.dat -set tftex10_1.set#tonyplot 的 overlay与set命令tonyplot -overlay tftex10_don.dat -set tftex10_don.set#绘制施主态密度分布曲线tonyplot -overlay tftex10_acc.dat -set tftex10_acc.set#绘制受主态密度分布曲线go atlas## In the next part of the input deck we extract the Id-Vd family of# curves. The structure definition is exactly the same.#mesh width=180x.m l=0 s=0.25x.m l=40 s=0.25y.m l=0 s=0.0005y.m l=0.02 s=0.0005y.m l=0.12 s=0.005region num=1 material=igzo y.min=0 y.max=0.02region num=2 material=sio2 y.min=0.02 y.max=0.12elec num=1 name=gate bottomelec num=2 name=source y.max=0.0 x.min=0.0 x.max=5.0elec num=3 name=drain y.max=0.0 x.min=35.0 x.max=40.0contact num=1 n.polycontact num=2 workf=4.33contact num=3 workf=4.33models fermidefects nta=1.55e20 ntd=1.55e20 wta=0.013 wtd=0.12 \nga=0.0 ngd=6.5e16 egd=2.9 wgd=0.1 \sigtae=1e-15 sigtah=1e-15 sigtde=1e-15 sigtdh=1e-15 \siggae=1e-15 siggah=1e-15 siggde=1e-15 siggdh=1e-15 \dfile=don afile=acc numa=128 numd=64## Here we calculate the start structures for each of the IdVd# family by performing an initial gate ramp.##(下⾯就有点懵了...)solve solve vstep=0.2 vfinal=4.0 name=gate save outf=tftex10_2.strsolve vstep=0.2 vfinal=8.0 name=gate save outf=tftex10_3.strsolve vstep=0.2 vfinal=12.0 name=gate save outf=tftex10_4.strsolve vstep=0.2 vfinal=16.0 name=gate save outf=tftex10_5.strsolve vstep=0.2 vfinal=20.0 name=gate save outf=tftex10_6.strload inf=tftex10_2.str master log outf=tftex10_2.logsolve vdrain=0.0 vstep=0.5 vfinal=20.0 name=drainload inf=tftex10_3.str master log outf=tftex10_3.logsolve vdrain=0.0 vstep=0.5 vfinal=20.0 name=drainload inf=tftex10_4.str master log outf=tftex10_4.logsolve vdrain=0.0 vstep=0.5 vfinal=20.0 name=drainload inf=tftex10_5.str master log outf=tftex10_5.logsolve vdrain=0.0 vstep=0.5 vfinal=20.0 name=drainload inf=tftex10_6.str master log outf=tftex10_6.logsolve vdrain=0.0 vstep=0.5 vfinal=20.0 name=draintonyplot -overlay tftex10_2.log tftex10_2.dat tftex10_3.log tftex10_3.dat tftex10_4.log tftex10_4.dat tftex10_5.log tftex10_5.dat tftex10_6.log tftex10_6.dat -set tftex10_2.set quit官⽹给出的四张输出图像如下:⾃⼰装的ATLAS还有点问题,这⼏天先折腾下在跑跑看。

高频npn双极型晶体管Silvaco TCAD仿真一、npn晶体管器件物理1.npn晶体管的基本结构和制造工艺(1)npn晶体管的基本结构双极型晶体管由两个“背靠背”的pn结组成,一种基本结构如图1所示,晶体管中两种载流子都参与导电。

双极型晶体管按照导电类型和极性可划分为npn 晶体管和pnp晶体管,按照制作工艺可划分为合金管、平面管和台面管。

图 1 双极型晶体管基本结构(2)npn晶体管的制造工艺1948年,美国贝尔实验室的肖克莱、巴丁和布拉顿利用合金烧结法制作了第一个锗基双极型晶体管分立器件,奠基了现代电子技术的基础[1]。

npn晶体管制造的平面外延工艺在上世纪70年代一度成为主流,随着各种先进工艺和材料的引进,npn晶体管普遍使用多晶硅发射极的结构以提升注入效率,通过异质外延、离子注入、极紫外光刻等技术,npn晶体管尺寸更小、掺杂浓度更高更精确,性能也更出色。

2.npn晶体管的输出特性和击穿特性(1)npn晶体管的电流放大功能当处于放大工作状态时,npn晶体管的电流输运分为以下三个步骤:发射区发射载流子→基区输运载流子→集电区收集载流子,由于两种载流子都参与晶体管的电流输运,故得名“双极型晶体管”,三个过程定量描述载流子输运的系数分别是注入效率、基区输运系数和集电区雪崩倍增因子。

当npn型双极型晶体管发射结正偏、集电结反偏时,晶体管的基极电流将与集电极电流呈现近似比例关系,即I C=βI B(β>>1),呈现出“电流放大”的功能,其中β称为npn晶体管的电流放大系数。

npn晶体管的输出特性曲线如图2所示,图中虚线代表V BC=0,即V CE=V BE 的情形,是放大区和饱和区的分界线。

(2)npn晶体管的击穿特性当双极型晶体管一个电极开路,在另外两个电极外加反向偏压时,npn晶体管将发生雪崩倍增效应,产生类似于pn结的击穿现象,基极开路时,使I CEO→∞的V CE称为BV CEO,npn晶体管的BV CEO曲线表示如图3所示。