实验六 半导体器件仿真实

- 格式:docx

- 大小:1.11 MB

- 文档页数:17

半导体功率器件与智能功率IC实验学生姓名:田瑞学号:201422030143指导教师:乔明一、实验室名称:211楼803 工作站二、实验项目名称:半导体功率器件与智能功率IC实验——VDMOS器件仿真设计实验三、实验原理:对于阈值电压的调节,可以改变氧化层厚度,氧化层厚度越大,栅对沟道的控制能力越弱,阈值电压越大。

也可以增大沟道区掺杂浓度,浓度越大,沟道区越难反型,阈值电压越大。

MEDICI的使用流程:四、实验目的:通过实验,了解VDMOS器件的结构,掌握VDMOS器件的设计方法,熟悉MEDICI 软件的使用。

五、实验内容:完成一种600V VDMOS器件完整的设计仿真工作,其指标达到预定要求。

其中,主要针对器件耐压、阈值电压、跨导、开态特性进行仿真优化,确定栅氧厚度、沟道浓度、栅长、漂移区掺杂、漂移区厚度等重要的浓度和结构参数。

衬底n+换成p+,再仿真器件的转移特性和击穿特性,比较与VDMOS区别,并分析原因。

VDMOS指标要求:BV > 600VV T 2~3V器件结构构造网格构造器件求解输出MEDICI 输入文件Device Structure SpecificationSolution SpecificationInput/Output预先确定器件结构V20V maxG六、实验器材(设备、元器件):MEDICI软件七、实验步骤:title VDMOSassign name=nd n.val=1e14assign name=pwell n.val=2e18assign name=dpwell n.val=1.2assign name=tepi n.val=35assign name=ld n.val=6mesh smooth=1x.mesh width=@ld h1=0.10y.mesh n=1 L=-0.1y.mesh n=3 L=-0.017y.mesh n=4 L=0y.mesh depth=@dpwell h1=0.05y.mesh depth=@tepi-@dpwell h1=0.05 h2=0.05 h3=1y.mesh depth=0.5 h1=0.05y.mesh depth=0.1 h1=0.05region name=si siliconregion name=sio y.max=0 oxideelectrod name=gate x.min=1 x.max=@ld-1electrod name=source x.max=0.6 y.max=0electrod name=source x.min=@ld-0.6 y.max=0electrod name=drain y.min=@tepi+0.5$$$$$ n drift $$$$$$$profile region=si n-type n.peak=@nd uniform$$$$$ p-well $$$$profile region=si p-type n.peak=@pwell+@nd xy.ratio=0.4 x.min=0 x.max=1.5 y.junction=@dpwellprofile region=si p-type n.peak=@pwell+@nd xy.ratio=0.4 x.min=@ld-1.5 x.max=@ld y.junction=@dpwell$$$$ n+/p+ source $$$$profile region=si p-type n.peak=1e20 xy.ratio=0.4 x.min=0 x.max=0.4y.junction=0.4profile region=si n-type n.peak=1e20 xy.ratio=0.4 x.min=0.5 x.max=1y.junction=0.2profile region=si p-type n.peak=1e20 xy.ratio=0.4 x.min=@ld-0.4 x.max=@ldy.junction=0.4profile region=si n-type n.peak=1e20 xy.ratio=0.4 x.min=@ld-1 x.max=@ld-0.5 y.junction=0.2$$$ drain $$$profile region=si n-type n.peak=1e20 uniform x.min=0 y.min=@tepi y.max=@tepi+0.5regrid ignore=sio doping logarith ratio=1 smooth=1 cos.angle=0.8$$$$ gate material $$$$$contact name=gate n.polysisave out.f=vdmos.mesh$$$$ plot $$$$plot.2d grid fill scale title=" the orignal gird"plot.2d boundary scale junction fill title="the junction profiles"plot.1d doping y.start=0.01 y.end=0.01 title="surface doping log" y.logplot.1d doping y.start=0.01 y.end=0.01 title="surface doping"plot.1d doping y.start=3 y.end=3 title="y=3 doping log" y.logplot.1d doping y.start=3 y.end=3 title="y=3 doping"plot.1d doping x.start=3 x.end=3 title="x=3 doping log" y.logplot.1d doping x.start=3 x.end=3 title="x=3 doping"八、实验数据及结果分析:器件模型:VDMOS的BV特性曲线:更改参数后BV为642V阈值电压曲线:更改参数后阈值电压为2V衬底n+换成p+时:BV为620V 阈值电压为2.45V九、实验结论:1、由BV特性曲线的比较可知,增大击穿电压BV可以采用的方法有增大漂移区浓度与厚度。

实验六半导体器件仿真实验姓名:林少明专业:微电子学学号11342047【实验目的】1、理解半导体器件仿真的原理,掌握Silvaco TCAD 工具器件结构描述流程及特性仿真流程;2、理解器件结构参数和工艺参数变化对主要电学特性的影响。

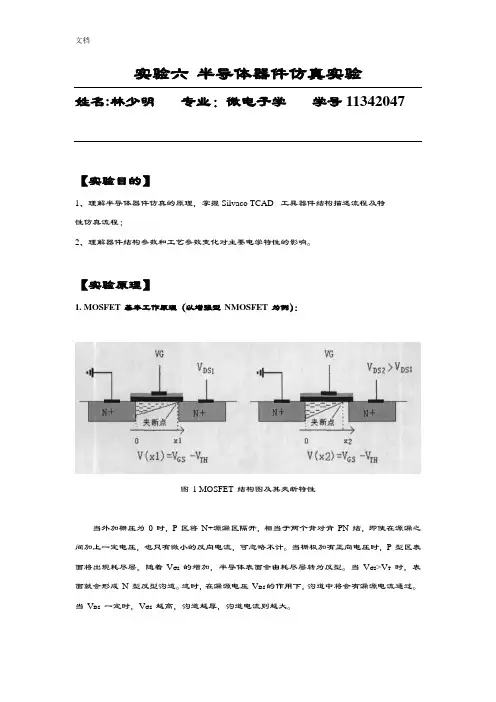

【实验原理】1. MOSFET 基本工作原理(以增强型NMOSFET 为例):图1 MOSFET 结构图及其夹断特性当外加栅压为0 时,P 区将N+源漏区隔开,相当于两个背对背PN 结,即使在源漏之间加上一定电压,也只有微小的反向电流,可忽略不计。

当栅极加有正向电压时,P 型区表面将出现耗尽层,随着V GS的增加,半导体表面会由耗尽层转为反型。

当V GS>V T时,表面就会形成N 型反型沟道。

这时,在漏源电压V DS的作用下,沟道中将会有漏源电流通过。

当V DS一定时,V GS越高,沟道越厚,沟道电流则越大。

2. MOSFET 转移特性V DS 恒定时,栅源电压 V GS 和漏源电流 I DS 的关系曲线即是 MOSFET 的转移特性。

对于增强型 NMOSFET ,在一定的 V DS 下, V GS =0 时, I DS =0;只有 V GS >V T 时,才有 I DS >0。

图 2 为增强型 NMOSFET 的转移特性曲线。

图 2 增强型 NMOSFET 的转移特性曲线图中转折点位置处的 V GS (th ) 值为阈值电压。

3. MOSFET 的输出特性对于 NMOS 器件,可以证明漏源电流:令n =oxWC Lμβ,称β为增益因子。

(1)()DS GS T V V V <<-由于 V DS 很小,忽略2DS V 项,可得:I DS 随 V DS 而线性增加,故称为线性区。

(2)()DS GS T V V V <-DS V 增大,但仍小于()GS T V V -,2DS V 项不能忽略。

故:在一定栅源电压下,V DS 越大,沟道越窄,则沟道电阻越大,曲线斜率变小。

器件仿真实验报告电力电子仿真仿真实验报告目录实验一:常用电力电子器件特性测试................................................................................... 3 (一)实验目的:................................................................................................ .. (3)掌握几种常用电力电子器件(SCR、GTO、MOSFET、IGBT)的工作特性; (3)掌握各器件的参数设置方法,以及对触发信号的要求。

(3)(二)实验原理.................................................................................................... (3)(三)实验内容.................................................................................................... (3)(四)实验过程与结果分析 (3)1.仿真系统.................................................................................................... (3)2.仿真参数.................................................................................................... .. (4)3.仿真波形与分析.................................................................................................... .. (4)4.结论.................................................................................................... .. (10)实验二:可控整流电路.................................................................................................... .. (11)(一)实验目的.................................................................................................... . (11)(二)实验原理.................................................................................................... . (11)(三)实验内容.................................................................................................... . (11)(四)实验过程与结果分析 (12)1.单相桥式全控整流电路仿真系统,下面先以触发角为0度,负载为纯电阻负载为例.................................................................................................... .. (12)2.仿真参数.................................................................................................... (12)3.仿真波形与分析.................................................................................................... (14)实验三:交流-交流变换电路................................................................................................19(一)实验目的.................................................................................................... . (19)(三)实验过程与结果分析 (19)1)晶闸管单相交流调压电路 (19)实验四:逆变电路.................................................................................................... . (26)(一)实验目的.................................................................................................... . (26)(二)实验内容.................................................................................................... . (26)实验五:单相有源功率校正电路 (38)(一)实验目的.................................................................................................... . (38)(二)实验内容.................................................................................................... . (38)个性化作业:................................................................................................ . (40)(一)实验目的:................................................................................................ . (40)(二)实验原理:................................................................................................ . (40)(三)实验内容.................................................................................................... . (40)(四)结果分析:................................................................................................ . (44)(五)实验总结:................................................................................................ . (45)实验一:常用电力电子器件特性测试(一)实验目的:掌握几种常用电力电子器件(SCR、GTO、MOSFET、IGBT)的工作特性;掌握各器件的参数设置方法,以及对触发信号的要求。

实验报告实验名称半导体器件课程设计班级姓名:学号:实验日期:实验地点:一.P MOS的制造流程制作PMOS的主要流程为:衬底掺杂—〉栅氧化—〉离子注入—〉淀积多晶硅栅—〉多晶硅氧化—〉多晶掺杂—〉边墙氧化层淀积—〉边墙氧化层刻蚀形成氧化层—〉源漏注入—〉源漏退火—〉金属化—〉镜像生成PMOS结构。

二.实验程序和图形进入模拟软件后,输入数据和程序go athena# Non-Uniform Grid(0.6um x 0.8um)line x loc=0.00 spac=0.10line x loc=0.20 spac=0.01line x loc=0.60 spac=0.01#line y loc=0.00 spac=0.008line y loc=0.20 spac=0.01line y loc=0.50 spac=0.05line y loc=0.80 spac=0.15# Initial Silicon Structure with <100> Orientationinit silicon c.phosphor=1.0e14 orientation=100 two.d# Gate Oxidationdiffus time=11 temp=950 dryo2 press=1.00 hcl.pc=3#extract name="Gateoxide" thickness material="SiO~2"mat.occno=1 x.val=0.3# Threshold Voltage Adjust implantimplant phosphor dose=9.5e10 energy=10 crysta l此图为离子注入后杂质浓度在画线处注入的磷的浓度相对于器件的深度的分布# Conformal Polysilicon Depositiondeposit polysilicon thick=0.20 divisions=10# Poly Definitionetch polysilicon left p1.x=0.35# Polysilicon Oxidationdiffus time=3 temp=900 weto2 press=1.00# Polysilicon Dopingimplant boron dose=3.0e13 energy=10 crystal# Spacer Oxide Depositiondeposit oxide thick=0.12 divisions=10# Spacer Oxide Etchetch oxide dry thick=0.12# Soucer/Drain Implantimplant bf2 dose=5.0e15 energy=24 tilt=0 rotation=0 crystal # Source/Drain Annealingmethod fermidiffus time=1 temp=900 nitro press=1.00下图为源漏退火前后两图相叠加、对比的图形。

半导体器件模拟设计研究随着科技的不断发展,各种电子设备在我们的生活中越来越普遍。

而在这些设备中,半导体器件扮演着至关重要的角色。

半导体器件模拟设计研究是半导体技术研发的重要一环,对于提升半导体器件的性能和稳定性具有重要作用。

一、半导体器件的基本原理半导体器件是利用半导体材料(如硅、锗等)的特殊性质,运用电子学和半导体物理学原理制成的电子元器件。

半导体器件的基本原理是利用P型材料和N型材料在界面处形成的PN结,在不同的电场作用下,控制电子和空穴的运动,实现电信号的转移和控制。

不同类型的半导体器件有不同的原理和工作方式,如二极管、三极管、场效应管等。

二、半导体器件模拟设计的意义半导体器件的性能和稳定性是制约其应用的关键因素。

在设计半导体器件时,需要根据其使用场景和需要的性能,选择合适的材料和设计方案,并进行模拟和优化。

半导体器件模拟设计研究的意义在于通过计算机模拟和仿真分析,预测和优化器件的性能,提高设计效率和成功率。

三、半导体器件模拟设计的过程半导体器件模拟设计的过程主要分为以下几个步骤:1.选取合适的EDA工具EDA(Electronic Design Automation)工具是进行半导体器件模拟和设计的关键软件。

常用的EDA工具有SPICE、ADS、HSPICE等,需要根据不同的需求和场合,选择合适的工具。

2.建立器件模型根据设计方案,需要建立相应的器件模型。

模型的建立需要考虑材料特性、结构参数等因素,以确保模拟结果的准确性和可靠性。

3.设计和布局电路在建立模型后,需要设计和布局电路,确定各个元器件之间的连接方式和工作模式。

设计过程中需要考虑材料特性、电路参数、工艺限制等因素。

4.进行仿真分析在电路设计和布局后,需要进行仿真分析,检查和评估器件性能和运行情况。

可以通过SPICE仿真、HSPICE仿真等方式进行分析。

5.优化和改进设计在仿真分析结果的基础上,需要对设计进行优化和改进。

可以考虑改变器件材料、结构参数、电路参数等方案,找到最优方案,提高器件性能和稳定性。

新型半导体材料与器件仿真实验项目课程介绍与课件电子科学与技术专业及微电子科学与工程专业的教学内容中,涉及到半导体纳米材料与器件。

纳米材料与器件的宏观物理特性是由材料的微观电子结构所决定的。

但是,材料的微观电子结构无法直接观察和测量,对学生理解和掌握所学知识带来了一定的难度;其次,制备纳米材料时需要考虑很多因素,如起始反应物的选择、反应物用量和配比,反应条件的设计。

为了获得性能好的产品,往往需要进行大量重复性的实验,对每一次实验结果进行分析检测,再改进方案重新实验。

即不断反复试验、不断摸索、不断修改,一直到获得最佳的结果为止。

如果需要摸索的条件多,实验研究的过程相应会增长,不利于提高研究效率。

通过虚拟仿真实验,以图形化、视频化的方式,栩栩如生的向学生展示了纳米材料的微观电子结构与宏观光学特性之间的关系;降低了实验成本。

加深了学生对学科基础理论知识的理解,使学生掌握本专业领域常用的设计与仿真软件工具,增强学生分析问题、解决问题的能力,进而达到较佳的教学效果。

在教学中,以启发式教学为主的教学方法。

采用录像、视频的形式,演示课程中所涉及的文物保护纳米涂层的作用,演示纳米材料的吸收光谱随纳米线尺寸的变化。

这部分穿插在多媒体课件中实施,解决传统课程黑板讲述不直观的问题。

激发学生的学习兴趣。

每次实验前,将学生分成若干个小组,通过小组讨论,进行合作学习,培养学生的思维表达能力,让学生多多参与,亲自动手、亲自操作、激发学习兴趣、促进学生主动学习。

小组讨论后,指导教师先进行一个基本的实验流程操作,对一些关键或容易出错之处进行强调,使学生首先有一个感性的认识。

每次实验都编排有依实验过程的相关问题的实验报告,学生一边实验操作一边思考,达到对理论或难点知识的深刻理解。

为了给学生提供一个良好的实验条件, 在课后学生可以在校园网内任何网络端口可全天候上机实践,并与指导老师进行交互。

若有任何问题,学生可以在网络平台给教师留言,进行意见反馈。

实验报告专业:______姓名:______学号:______日期:______桌号:________________课程名称:模拟电子技术基础实验指导老师:成绩:________________ 实验名称:半导体器件特性仿真一、实验目的1. 掌握PSpice软件的使用。

2. 学习半导体器件特性的仿真分析方法。

二、实验内容1. 仿真分析二极管的伏安特性。

2. 仿真分析二极管的温度特性。

3. 仿真分析二极管两端的输出波形。

4. 分析仿真分析三极管的输出特性。

三、实验电路和实验结果1. 仿真分析二极管的伏安特性。

仿真电路:仿真结果:二极管的伏安特性图:50mA0A-50mA-100mA-120V-100V-80V-60V-40V-20V-0V20V I(D)V(D:1)二极管正向导通的伏安特性图:40mA30mA20mA10mA0A0V0.1V0.2V0.3V0.4V0.5V0.6V0.7V0.8V0.9V 1.0V I(D)V(D:1)仿真结果分析:图一中:二极管加有反向电压,当电压值较小时,电流极小。

当反向电压超过某个值时,电流开始急剧增大,称为反向击穿,此电压为二极管的反向击穿电压。

图二中,开启电压约为0.5V,0V-0.5V称为死区,0.5V之后二极管正向导通。

此二极管应该为硅二极管。

2. 仿真分析二极管的温度特性。

仿真电路:仿真结果:二极管的温度特性图:V(D:1)0V 0.1V0.2V0.3V0.4V0.5V0.6V0.7V0.8V0.9V1.0VI(D)0A 20mA40mA50mA仿真结果分析:温度的敏感器件,温度的变化对其伏安特性的影响主要表现为:随着温度的升高,其正向特性曲线左移,即正向压降减小。

3. 仿真分析二极管两端的输出波形。

仿真电路:仿真结果:Time0s0.2ms0.4ms0.6ms0.8ms1.0ms1.2ms1.4ms1.6ms1.8ms2.0msV(out)-10V-5V0V5V仿真结果分析:由图可知:二极管导通后,其上压降基本接近其开启电压,所以利用二极管单向导电性,可以把方向交替变化的交流电变换成单一方向的脉冲直流电。

实验六NPN器件TCAD模拟实验一、实验调查掌握NPN器件的特性,转移特性曲线,IV特性曲线,放大倍数等二、实验目的1. 熟悉Silvaco TCAD的仿真模拟环境;2、掌握NPN器件设计流程2.掌握器件特性的仿真流程3.掌握使用Tonyplot观察仿真仿真结果三、实验要求1、实验前必须仔细调查实验调查的内容2、根据程序完成NPN器件的设计仿真四、实验指导器件结构设计步骤:1、创建一个初始网格结构2、初始化硅衬底3、进行Boron离子注入4、进行Boron扩散5、淀积多晶硅栅6、进行Polysilicon掺杂7、刻蚀多晶硅8、多晶硅氧化9、退火10、进行二次Boron离子注入11、形成侧氧12、进行三次Boron离子注入与退火13、镜像得到完整NPN结构14、形成发射级和基极接触15、定义电极16、保存ATHENA结构文件图一NPN三极管器件仿真步骤:1、结构说明2、材料模型说明3、数学计算方法的说明4、解析条件说明5、结果分析图二NPN三极管转移特性图三NPN三极管IV特性五、实验仿真程序结构仿真程序:go athena# Polysilicon Emitter Bipolar (NPN)line x loc=0.00 spac=0.03line x loc=0.2 spac=0.02line x loc=0.24 spac=0.015line x loc=0.3 spac=0.015line x loc=0.8 spac=0.15#line y loc=0.00 spac=0.01line y loc=0.12 spac=0.01line y loc=0.3 spac=0.02line y loc=0.5 spac=0.06line y loc=1 spac=0.35# Initial Silicon Structureinit silicon c.arsenic=2e16 orientation=100#struct outfile=init_bjt.str# Implant Boronimplant boron dose=2.5e13 energy=18 crystal # Diffuse Borondiffus time=60 temp=920 nitro#struct outfile=implant1_bjt.str# Deposit Polysilicondeposit polysilicon thick=0.3 divisions=6#struct outfile=poly_bjt.str# Implant to Dope Polysiliconimplant arsenic dose=7.5e15 energy=50 crystal #struct outfile=dopepoly_bjt.str# Pattern Polysiliconetch polysilicon right p1.x=0.2#struct outfile=etchpoly_bjt.str# Polysilicon Oxidationmethod fermi compressdiffus time=25 temp=920 dryo2 press=1.00#struct outfile=polyox_bjt.str# Annealing Processdiffus time=50 temp=900 nitro press=1.00#struct outfile=anneal_bjt.str# Second Boron Implantationimplant boron dose=2.5e13 energy=18 crystal#struct outfile=implant2_bjt.str# Deposit Spacerdeposit oxide thick=0.4 divisions=10#struct outfile=depositspacer_bjt.str# etch the Spacer Backetch oxide dry thick=0.50#struct outfile=etchspacer_bjt.str# Forming P+ Base Regionimplant boron dose=1e15 energy=30 crystal#struct outfile=implant3_bjt.str# Second Annealing Processdiffus time=60 temp=900 nitro press=1.00#struct outfile=anneal2_bjt.str#struct mirror left#struct outfile=full_bjt.str# Put down Aluminum and Etch to form the Emitter/Base Contacts deposit aluminum thick=0.05 divisions=2#struct outfile=deposit_Al_bjt.str# etch the Left Hand Side Shaded Regionetch aluminum start x=-0.16 y=-0.35etch cont x=-0.16 y=0.1etch cont x=-0.6 y=0.1etch done x=-0.6 y=-0.35#struct outfile=etchleft_bjt.str# etch the Right Hand Side Shaded Regionetch aluminum right p1.x=0.15#struct outfile=etchfight_bjt.str#electrode name=emitter x=0.00#electrode name=base x=-0.65#electrode name=collector backside#struct outfile=bjt.str性能仿真程序:go atlas#mesh infile=bjt.str#material number=2 taun0=5e-06 taup0=5e-06#models auger consrh conmob fldmob b.electrons=2 b.holes=1 evsatmod=0 \ hvsatmod=0 boltzman bgn print temperature=300#contact name=emitter n.poly surf.rec#method newton itlimit=25 trap atrap=0.5 maxtrap=4 autonr nrcriterion=0.1 \ tol.time=0.005 dt.min=1e-25solve initsolve vcollector=0.025solve vcollector=0.1solve name=collector vcollector=0.25 vfinal=2 vstep=0.25solve vbase=0.025solve vbase=0.1solve vbase=0.2log outf=bjt_0.logsolve name=base vbase=0.3 vfinal=1 vstep=0.05tonyplot bjt_0.loglog offsolve init# Ramping base voltagesolve vbase=0.025solve vbase=0.05solve vbase=0.1 vstep=0.1 vfinal=0.7 name=base# Switch to Current Boundary Conditionscontact name=base current# ramp base current and save the solutionssolve ibase=1.e-6save outf=bjt_1.str mastersolve ibase=2.e-6save outf=bjt_2.str mastersolve ibase=3.e-6save outf=bjt_3.str mastersolve ibase=4.e-6save outf=bjt_4.str mastersolve ibase=5.e-6save outf=bjt_5.str master# Load in each initial guess file and ramp Vceload inf=bjt_1.str masterlog outf=bjt_1.logsolve vcollector=0.0 vstep=0.1 vfinal=5.0 name=collector load inf=bjt_2.str masterlog outf=bjt_2.logsolve vcollector=0.0 vstep=0.1 vfinal=5.0 name=collector load inf=bjt_3.str masterlog outf=bjt_3.logsolve vcollector=0.0 vstep=0.1 vfinal=5.0 name=collector load inf=bjt_4.str masterlog outf=bjt_4.logsolve vcollector=0.0 vstep=0.1 vfinal=5.0 name=collector load inf=bjt_5.str masterlog outf=bjt_5.logsolve vcollector=0.0 vstep=0.1 vfinal=5.0 name=collector # Plot Family of Ic/Vce curvetonyplot -overlay bjt_1.log bjt_2.log bjt_3.log bjt_4.log \ bjt_5.log -set bjt_1.setquit六、实验任务1、完成实验指导4和仿真程序5的内容;七、实验结果分析与体会附录:NPN三极管器件仿真操作启动Deckbuild,同时调用ATHENA工具包,在终端输入命令deckbuild –an&实验三:用ATHENA创建一个多晶硅发射级NPN三极管1、创建一个初始网格结构目的,创建一个0.8um*1.0um模拟区域及一个非均匀网格在工具栏右键点击Commands→选Mesh Define...输入坐标及间距go athena# Polysilicon Emitter Bipolar(NPN)line x loc=0.00 spac=0.03line x loc=0.2 spac=0.02line x loc=0.24 spac=0.015line x loc=0.3 spac=0.015line x loc=0.8 spac=0.15#line y loc=0.00 spac=0.01line y loc=0.12 spac=0.01line y loc=0.3 spac=0.02line y loc=0.5 spac=0.06line y loc=1.0 spac=0.352、初始化硅衬底(如图一)目的,得到均匀掺杂砷浓度为2×1016atom/cm3、(100)方向的硅衬底打开ATHENA Mesh Initialize菜单:右键点击Commands→ Mesh Initialize。

电子科技大学成都学院实验报告册课程名称:器件仿真实验姓名:王灿学号:1140720524院系:微电子专业:电子科学与技术教师:袁艺丹2013 年12 月25 日实验一:MEDICI的使用方法一、实验目的:了解器件仿真软件学习使用medici二、实验原理和内容:使用medici建立一个PN结三、实验步骤:1.打开medici,输入用户名和密码2.新建文件夹3.新建文件4.编写器件结构文件并查看器件结构图像5.编写文件并查看一维杂质分布6.编写文件并查看杂质的二维分布图像7.求解并查看漏极电压和漏极电流的关系8.编写文件查看电势分布和电流分布9.求解并查看漏极电流的瞬态曲线四、实验数据和结果:TITLE Avant! MEDICI Example 1 - 1.5 Micron N-Channel MOSFET COMMENT Specify a rectangular meshMESH SMOOTH=1X.MESH WIDTH=3.0 H1=0.125Y.MESH N=1 L=0Y.MESH N=30 L=2.0COMMENT Specify oxide and silicon regionsREGION SILICONCOMMENT Electrode definitionELECTR NAME=anode X.MIN=0.625 X.MAX=2.375 TOPELECTR NAME=cathode BOTTOMCOMMENT Specify impurity profiles and fixed chargePROFILE P-TYPE N.PEAK=2E16 Y.CHAR=.25PROFILE N-TYPE N.PEAK=2E20 Y.JUNC=.34 X.MIN=2.5 WIDTH=.5 + XY.RAT=.75PLOT.2D GRID TITLE="Example 1 - Initial Grid" FILL SCALE COMMENT Regrid on dopingREGRID DOPING LOG IGNORE=OXIDE RATIO=2 SMOOTH=1PLOT.2D GRID TITLE="Example 1 - Doping Regrid" FILL SCALE COMMENT Specify contact parametersCONTACT NAME=Gate N.POLYCOMMENT Specify physical models to useMODELS CONMOB FLDMOB SRFMOB2COMMENT Symbolic factorization, solve, regrid on potentialSYMB CARRIERS=0METHOD ICCG DAMPEDSOLVEREGRID POTEN IGNORE=OXIDE RATIO=.2 MAX=1 SMOOTH=1 PLOT.2D GRID TITLE="Example 1 - Potential Regrid" FILL SCALE五、实验总结:学习了仿真软件的使用,通过这个简单的pn结实验熟练的达到学习该软件的目的,编写合适的程序仿真出pn结的图形,了解一些简单的工艺步骤,为以后做实验打下了坚实的基础,对于更加复杂的实验更能熟悉。

半导体器件基础实验1.实验目的通过利用EDA工具对肖特基二极管进行模拟仿真,并通过利用控制变量法,通过对影响PN结特性的一些因素的调节,观察其对PN结特性的影响。

2.实验概述1、改变掺杂浓度对肖特基二极管 I-V 曲线的影响2、改变金属功函数对肖特基二极管 I—V 曲线的影响3、改变温度对肖特基二极管 I—V 曲线的影响4、改变N区分布函数对肖特基二极管 I—V 曲线的影响3.实验内容1.N 区浓度对 IV 曲线及结构的影响6e186e10N型轻掺杂浓度为6e10#(c) Silvaco Inc。

, 2013go atlasmesh space.mult=1。

0#绘制x向网格x.meshloc=0。

00 spac=0.5x。

meshloc=3.00 spac=0.2x.meshloc=5.00 spac=0.25x.meshloc=7.00 spac=0.25x.meshloc=9。

00 spac=0。

2x.meshloc=12.00 spac=0.5#绘制y向网格y.meshloc=0.00 spac=0.1y.meshloc=1。

00 spac=0.1y.meshloc=2。

00 spac=0.2y。

meshloc=5.00 spac=0.4# 用硅半导体作衬底region num=1 silicon#定义电极electr name=anode x.min=5 length=2 electr name=cathode bot#...。

N—epi doping N型掺杂doping n。

typeconc=6e10 uniform#。

.。

Guardring doping P型掺杂doping p。

typeconc=1e19 x。

min=0 x。

max=3 junc=1 rat=0.6 gaussdoping p.typeconc=1e19 x.min=9 x。

max=12 junc=1 rat=0。

实验2 PN结二极管特性仿真1实验内容(1)PN结穿通二极管正向I-V特性、反向击穿特性、反向恢复特性等仿真。

(2)结构和参数:PN结穿通二极管的结构如图1所示,两端高掺杂,n-为耐压层,低掺杂,具体参数:器件宽度4叩,器件长度20卩m耐压层厚度16卩m p+区厚度2(im, n+区厚度2叩。

掺杂浓度:p+区浓度为1xi019cm-3, n+区浓度为1xi019cm-3,耐压层参考浓度为5X1015 cm-3。

图1普通耐压层功率二极管结构2、实验要求(1)掌握器件工艺仿真和电气性能仿真程序的设计(2)掌握普通耐压层击穿电压与耐压层厚度、浓度的关系。

3、实验过程#启动Athenago athe na#器件结构网格划分;line x loc=0.0 spac= 0.4line x loc=4.0 spac= 0.4line y loc=0.0 spac=0.5line y loc=2.0 spac=0.1line y loc=10 spac=0.5line y loc=18 spac=0.1line y loc=20 spac=0.5#初始化Si衬底;init silicon c.phos=5e15 orientation=100 two.d#沉积铝;deposit alum thick=1.1 div=10#电极设置electrode n ame=a node x=1electrode n ame=cathode backside#输出结构图structure outf=cb0.strton yplot cb0.str#启动Atlasgo atlas#结构描述doping p.type conc=1e20 x.min=0.0 x.max=4.0 y.min=0 y.max=2.0 uniformdoping n.type conc=1e20 x.min=0.0 x.max=4.0 y.min=18 y.max=20.0 uniform#选择模型和参数models cvt srh printmethod carriers=2impact selb#选择求解数值方法method n ewt on#求解solve in itlog outf=cb02.logsolve vano de=0.03solve vano de=0.1 vstep=0.1 vfin al=5 n ame=a node#画出IV特性曲线tonyplot cb02.log#退出quit图2为普通耐压层功率二极管的仿真结构。

实验六半导体器件仿真实验姓名:林少明专业:微电子学学号11342047【实验目的】1、理解半导体器件仿真的原理,掌握Silvaco TCAD 工具器件结构描述流程及特性仿真流程;2、理解器件结构参数和工艺参数变化对主要电学特性的影响。

【实验原理】1. MOSFET 基本工作原理(以增强型NMOSFET 为例):图 1 MOSFET 结构图及其夹断特性当外加栅压为0 时,P 区将N+源漏区隔开,相当于两个背对背PN 结,即使在源漏之间加上一定电压,也只有微小的反向电流,可忽略不计。

当栅极加有正向电压时,P 型区表面将出现耗尽层,随着V GS的增加,半导体表面会由耗尽层转为反型。

当V GS>V T时,表面就会形成N 型反型沟道。

这时,在漏源电压V DS的作用下,沟道中将会有漏源电流通过。

当V DS一定时,V GS越高,沟道越厚,沟道电流则越大。

2. MOSFET 转移特性V DS 恒定时,栅源电压 V GS 和漏源电流 I DS 的关系曲线即是 MOSFET 的转移特性。

对于增强型 NMOSFET ,在一定的 V DS 下, V GS =0 时, I DS =0;只有 V GS >V T 时,才有 I DS >0。

图 2 为增强型 NMOSFET 的转移特性曲线。

图 2 增强型 NMOSFET 的转移特性曲线图中转折点位置处的 V GS (th ) 值为阈值电压。

3. MOSFET 的输出特性对于 NMOS 器件,可以证明漏源电流:令n =oxWC Lμβ,称β为增益因子。

(1)()DS GS T V V V <<-由于 V DS 很小,忽略2DS V 项,可得:I DS 随 V DS 而线性增加,故称为线性区。

(2)()DS GS T V V V <-DS V 增大,但仍小于()GS T V V -,2DS V 项不能忽略。

故:在一定栅源电压下,V DS 越大,沟道越窄,则沟道电阻越大,曲线斜率变小。

根据③式知,I DS -V DS 关系曲线为通过原点的抛物线。

当 V DS =(V GS -V T )时,I DS -V DS 关系曲线斜率为 0,表明此时沟道电阻很大。

在该区,沟道电阻逐渐变大,称为可变电阻区,或非饱和区。

(3)()DS GS T V V V ≥-将()DS GS T V V V =-代入①式,得到此时,漏电流 I DS 与漏源电压 V DS 无关,即达到饱和,I DSat 则称为饱和漏电流。

根据上述分析,可分析 MOSFET 的输出特性曲线:图 3 增强型 NMOSFET 输出特性4. 影响阈值电压的因素:可以证明,对于 NMOSFET 的阈值电压 V T 表达式为:其中, Cox 为栅电容,Fp ϕ为费米势,ms φ为接触电势差, Qox 为氧化层电荷密度。

由公式⑤可知,影响阈值电压的主要由栅电容 Cox 、衬底杂质浓度、氧化层电荷密度 Qox 等因素决定。

由0sox oxC t εε=可知,氧化层厚度 tox 越薄,则 Cox 越大,使阈值电压 V T 降低。

费米势:lnAFp iN kT q n ϕ=,当 P 区掺杂浓度 N A 变大,则费米势增大,阈值电压 V T 增大 。

氧化层电荷密度 Qox 增大,则 V T 减小。

5. 影响 MOSFET 输出特性的因素由①式可知,影响输出曲线的因素为增益因子β和阈值电压 V T 。

已知n oxW C Lμβ=,因此,当沟道长度 L 增大时,β减小。

由原理 4 知,影响 V T 的主要因素有栅电容 Cox 、衬底杂质浓度、氧化层电荷密度 Qox 等因素。

【实验仪器】计算机,Silvaco TCAD 软件【实验内容】1.采用ALTAS 器件仿真工具对NMOS 器件电学特性仿真 (1)I-V 输出特性曲线a、Vds=0.1V时,Id-Vgs曲线。

b、Vgs分别为3.3V、4.4V和5.5V时,Id-Vgs曲线。

(2)器件参数提取,如阈值电压、Beta和Theta等。

2.改变器件结构参数和工艺参数,分析其对NMOS器件主要电学特性的影响。

(1)栅氧厚度tox(2)沟道长度L(3)衬底杂志浓度【实验数据记录及分析】1.采用ALTAS器件仿真工具对NMOS器件电学特性仿真在Silvaco 中建立的指定参数器件模型结构如图示:图4指定参数MOSFET 结构模型中,氧化层厚度tox 为0.1 μm,沟道长度L 为 1 μm,p型衬底浓度10^17cm-3,n阱掺杂浓度为10^19cm-3。

选用载流子统计模型(fermidirac)对器件进行模拟,固定漏源电压为0.1V。

所得的转移特性曲线如图所示:图5 转移特性曲线图当 V GS分别为 3.3、4.4、5.5V 时,模拟出器件的输出曲线如图示:图6 器件输出特性曲线由下至上的曲线分别代表V GS为3.3、4.4、5.5V 的情况。

由该模拟结果可得,在V GS>V T 的情况下,随着V GS的增大,饱和漏源电流I DSat增大,与式④所分析的结果相符合。

观察曲线可知,当V DS较小时,曲线近似呈线性,随着V DS增大,曲线趋于平缓,与实验原理分析结果相符。

提取器件参数,从运行窗口中可以看到阀值电压,Beta 和Theta 等,如下:图7 提取参数代码段1提取结果总结如下: 阀值电压:vt=3.41966 V Beta :beta=4.24194e-005 A/V2 Theta :theta=0.0644978 1/V2.改变器件结构参数和工艺参数,分析其对NMOS 器件主要电学特性的影响。

(1)改变栅氧厚度tox 的值,分析其对NMOS 器件电学特性的影响。

①将氧化层厚度tox 从0.1μm 改为0.05μm ,分别就器件结构及器件参数、转移特性曲线、输出特性曲线三个方面进行分析和比较。

器件结构及器件参数比较(1)tox=0.1 μm(2)t ox =0.05 μm图8器件结构及器件参数图对比观察器件结构图和器件参数值可知,栅极和沟道之间的氧化层变薄,而且阈值电压变小了,Beta 值变大了,Theta 值变小了。

转移特性曲线改变比较图9 器件转移特性曲线对比观察图9曲线,可知改变氧化层厚度为0.05 μm 后,V T = V ,比氧化层厚度为0.1 μm 时的V T =3.41699 V 要小,说明氧化层变薄后,阈值电压降低。

由公式⑤以及公式0sox oxC t εε=,分析可知,当氧化层厚度t ox 的值越小时,即氧化层厚度越薄,栅极电容C ox 的值越大,使阈值电压的降低。

可知仿真结果和理论分析相符合。

输出特性曲线比较(V gs 分别为3.3v ,4.4v ,5.5v )图10器件输出特性曲线对比观察图10曲线,可知改变氧化层厚度为0.05 μm 后,在通入同等栅极电压的情况下,氧化层厚度变薄,饱和漏源电流变得比原器件大。

由公式0sox oxC t εε=,n oxW C Lμβ=分析可知,氧化层厚度变薄,C ox 和β的值同时增大。

由此可知,仿真结果和理论分析相符合。

②将氧化层厚度tox 从0.1μm 改为0.2μm ,分别就器件结构及器件参数、转移特性曲线、输出特性曲线三个方面进行分析和比较。

为进一步验证①中的结论,下面将列出厚度为0.2μm 时,器件结构及器件参数、转移特性曲线、输出特性曲线三个方面的仿真情况,不对结果再作详细分析。

器件结构及器件参数比较(1)t ox =0.1 μm(2)t ox =0.2 μm图11器件结构及器件参数图对比转移特性曲线改变比较图12 器件转移特性曲线对比输出特性曲线比较(V gs分别为3.3v,4.4v,5.5v)图13器件输出特性曲线对比分别观察图11,、图12、图13可知,当氧化层厚度增大时,阈值电压增大,饱和漏源电流变得比原器件小,即β值减少。

可知当氧化层厚度增大时,仿真结果和理论分析也一致。

(2)改变沟道长度L的值,分析其对NMOS器件电学特性的影响。

将沟道长度度tox从1μm改为0.6μm,分别就器件结构及器件参数、转移特性曲线、输出特性曲线三个方面进行分析和比较。

器件结构及器件参数比较(1)L=1μm(2)L=0.6 μm图14器件结构及器件参数图对比观察图14,可知当沟道长度减小到0.6μm 后,阈值电压减少到3.32242V ,但变化幅度非常小,另外,β值减小,θ值增大。

转移特性曲线改变比较图15 器件转移特性曲线对比改变沟道长度为0.6μm 后,阈值电压V T =3.32242V ,与沟道长度为1μm vt=3.41699 V 近似相等,说明沟道长度和阈值电压无明显相关性。

结合实验理论分析,在理想状态下,由公式可知,阈值电压与沟道长度没有明显的相关性,仿真结果和理论分析结果相符合。

输出特性曲线比较(V gs 分别为3.3v ,4.4v ,5.5v )图16器件输出特性曲线对比由图可知,沟道长度变短之后,在通入相同栅压的情况下,饱和漏源电流比改变之前要大。

结合实验原理分析,n oxW C Lμβ=,当沟道长度变小时,β值增大,饱和漏源电流增大。

可知仿真结果和理论分析结果相符合。

(3)改变衬底掺杂浓度的值,分析其对NMOS 器件电学特性的影响。

将衬底掺杂浓度从1017cm -1改为1015 cm -1,分别就器件结构及器件参数、转移特性曲线、输出特性曲线三个方面进行分析和比较。

器件结构及器件参数比较(1)N A =1017cm -1(2)N A = 1015 cm -1图17器件结构及器件参数图对比观察图17可知,衬底浓度减小时,阈值电压减小了,β值增大,theta 值减小了。

转移特性曲线改变比较图18 器件转移特性曲线对比改变衬底掺杂浓度为1015cm-1时,阈值电压减小为vt=1.25669 V,比掺杂浓度为1017cm-1时小由公式分析可知,当掺杂浓度减小时,费米电势增大,则阈值电压减小。

所以仿真结果和理论分析结果相符合。

输出特性曲线比较(V gs分别为3.3v,4.4v,5.5v)图19器件输出特性曲线对比观察图19可知,衬底浓度变小后,通入相同的栅极电压下,饱和漏源电流比改变前小。

由半导体物理知识可知,衬底掺杂浓度减小会增大载流子迁移率,根据公式n oxuW C Lμβ=,β值增大,饱和源漏电流增大,所以,可知仿真结果和理论分析结果相符合。

【实验总结】一、通过本次实验,熟悉了利用silvaco 软件进行NMOS 器件结构描述流程和电学特性仿真的流程,通过修改参数进行仿真实验,对于器件参数对器件电流特性的影响有了更加深入的了解。

二、通过改变实验参数,可总结出:1. 随着栅压的提高,横流区的漏极电流也相应提高;2. 恒流区的漏极电流也是随着漏极电压增大而略有增大,不是理想横流特性;3. 随着栅极与沟道间氧化层厚度的变小,栅极对于漏极电流的调控能力增强;4.当栅压过大时,会出现氧化层击穿,会导致漏极电流反而减小;5.由于氧化层太薄,导致漏电流更大了,所以器件开关比变小;6.随着沟道长度的增加,漏极电流会有所下降,但是恒流特性会有所提高;。