TAP状态机

- 格式:doc

- 大小:42.00 KB

- 文档页数:7

JTAG电路的工作原理JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它提供了一种简单、高效的方法来访问和控制电路中的内部信号和逻辑。

本文将详细介绍JTAG电路的工作原理。

JTAG电路由两部份组成:测试访问端(TAP)和测试访问控制器(TAC)。

TAP是位于被测试电路和测试设备之间的接口,用于传输数据和控制信号。

TAC 是测试设备中的逻辑电路,用于控制TAP并处理测试数据。

JTAG电路的工作原理如下:1. TAP控制状态机(TAP Controller State Machine):TAP控制状态机是TAC 中的一种有限状态机,用于控制TAP的操作。

它包含四个状态:Test-Logic-Reset (TLR)、Run-Test/Idle(RTI)、Select-DR-Scan(SDR)和 Select-IR-Scan (SIR)。

在不同的状态下,TAP控制状态机会执行不同的操作。

2. 信号传输:JTAG电路通过四条信号线进行数据和控制信号的传输。

这四条信号线分别是:TCK(Test Clock)、TMS(Test Mode Select)、TDI(Test Data Input)和 TDO(Test Data Output)。

- TCK:测试时钟信号,用于同步数据传输和状态转换。

- TMS:测试模式选择信号,用于控制TAP状态机的状态转换。

- TDI:测试数据输入信号,用于向被测试电路传输测试数据。

- TDO:测试数据输出信号,用于从被测试电路读取测试结果。

3. TAP状态转换:TAP控制状态机通过TMS信号控制状态的转换。

根据TMS 信号的不同序列,TAP状态机可以从一个状态转换到另一个状态。

例如,从TLR 状态转换到RTI状态,或者从RTI状态转换到SDR状态。

4. 测试数据传输:在SDR状态下,可以通过TCK、TDI和TDO信号进行测试数据的传输。

Gowin FPGA产品JTAG配置手册TN653-1.07, 2019-11-18版权所有© 2019广东高云半导体科技股份有限公司未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

目录目录 (i)图目录 (iii)表目录 (iv)1 关于本手册 (1)1.1 手册内容 (1)1.2 适用产品 (1)1.3 相关文档 (1)1.4 术语、缩略语 (2)1.5 技术支持与反馈 (2)2 配置和烧录(Configuration&Programming) (3)2.1 JTAG配置模式 (3)2.2 配置流程 (5)2.2.1 JTAG引脚定义 (5)2.2.2 TAP状态机 (5)2.2.3 TAP复位 (5)2.2.4 指令寄存器和数据寄存器 (6)2.2.5 读取ID CODE实例 (7)2.2.6 配置SRAM流程 (9)2.2.7 读取SRAM的流程 (12)2.2.8 擦除内部Flash (14)2.2.9 编程内部Flash流程 (18)2.2.10 读取内部Flash流程 (22)2.2.11 背景烧录(Background Programming) (25)2.2.12 编程外部Flash (27)2.2.13 读取Status Register 0x41 (31)2.2.14 读取User Code 0x13 (32)2.2.15 重加载0x3C (32)2.2.16 擦除SRAM 0x15 (32)3 例程文件 (33)图目录图2-1 JTAG配置模式连接示意图 (4)图2-2 TAP状态机 (5)图2-3指令寄存器访问时序 (6)图2-4数据寄存器访问时序 (6)图2-5读取ID Code状态机流程图 (8)图2-6读取ID Code指令-0x11访问时序 (8)图2-7读取ID Code数据寄存器访问时序 (8)图2-8配置SRAM流程 (10)图2-9 Tansfer Configuration Data过程示意 (11)图2-10读取SRAM的流程 (13)图2-11擦除GW1N-2(B)/4(B)/6/9,GW1NZ-1内部Flash擦除流程 (15)图2-12擦除GW1N-1(S)内部Flash流程 (17)图2-13编程内部Flash流程图 (19)图2-14 X-page编程流程图 (21)图2-15 Y-page编程流程图 (22)图2-16读取内部Flash流程图 (23)图2-17读取一个Y-page的过程 (24)图2-18 GW1N-4 Background Programming 流程图 (25)图2-19 Transfer JTAG Instrction Sample & Extest 流程图 (26)图2-20 JTAG接口编程外部Flash连接示意图 (27)图2-21采用config-mode[2:0]=011模式编程SPI Flash流程示意图 (28)图2-22 GW2A系列JTAG模拟SPI发送0x06指令时序图 (28)图2-23 GW1N系列JTAG模拟SPI发送0x06指令时序图 (29)图2-24采用Boundary Scan模式编程SPI Flash流程示意图 (30)表目录表目录表1-1术语、缩略语 (2)表2-1 JTAG配置模式管脚定义 (3)表2-2 Gowin FPGA IDCODE (7)表2-3发送指令过程中TDI和TMS的值变化 (7)表2-4器件SRAM地址数量和地址长度 (12)表2-5 JTAG的TCK频率要求 (14)表2-6 Readback-pattern / Autoboot-pattern (18)表2-7管脚状态 (29)表2-8 Status Register含义 (31)1关于本手册 1.1手册内容1关于本手册1.1手册内容本手册主要介绍Gowin FPGA产品的JTAG配置及烧录相关信息,包含JTAG配置模式、配置流程及相关例程文件。

JTAG电路的工作原理JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它是一种通用的、硬件辅助的测试方法,可以用于验证芯片的功能和性能,以及进行故障诊断和调试。

JTAG电路的工作原理是基于一种被称为“Boundary Scan”的技术。

Boundary Scan是一种在芯片的边界上添加了一系列的测试逻辑和控制逻辑的方法。

这些逻辑电路通过JTAG接口与外部测试设备连接,可以对芯片内部的信号和电路进行测试和控制。

JTAG电路由四个主要组件组成:Test Access Port (TAP)、Instruction Register (IR)、Data Register (DR)和Boundary Scan Register (BSR)。

首先,TAP是JTAG电路的核心组件,它负责与外部测试设备进行通信。

TAP 包括两个状态机:Test-Logic-Reset (TLR)状态机和Run-Test/Idle (RTI)状态机。

TLR 状态机用于初始化和复位电路,而RTI状态机用于执行测试和调试操作。

其次,IR是一个用于存储指令的寄存器。

通过JTAG接口,外部测试设备可以向IR中加载不同的指令,用于控制芯片的测试和调试操作。

常见的指令包括读取和写入数据、设置和清除寄存器等。

然后,DR是一个用于存储数据的寄存器。

通过JTAG接口,外部测试设备可以向DR中加载测试数据,或者从DR中读取测试结果。

这样可以实现对芯片内部信号和电路的测试和调试。

最后,BSR是一组用于测试芯片边界上的信号和电路的寄存器。

它包含了一系列的扫描链,每一个扫描链都与芯片边界上的一个信号或者电路相连。

通过JTAG 接口,外部测试设备可以对BSR中的扫描链进行操作,以实现对芯片边界上信号和电路的测试和调试。

JTAG电路的工作流程如下:1. 初始化和复位:外部测试设备通过TAP的TLR状态机将芯片初始化和复位,确保芯片处于可测试状态。

构建系统级JTAG链调试电路第一部分:JTAG技术介绍JTAG技术俗称边界扫描技术,是近代发展起来的高级测试技术。

JTAG主要有以下几个方面应用:1) .互连测试。

判断互连线路是否存在开路、短路或固定逻辑故障。

2) .可编程器件的程序加载。

如FLASH CPLD FPGA等器件的加载。

3) .可编程器件的在线调试。

如FPGA DSP等器件在线debug。

4) .电路采样。

器件正常工作时,对管脚状态进行采样观察。

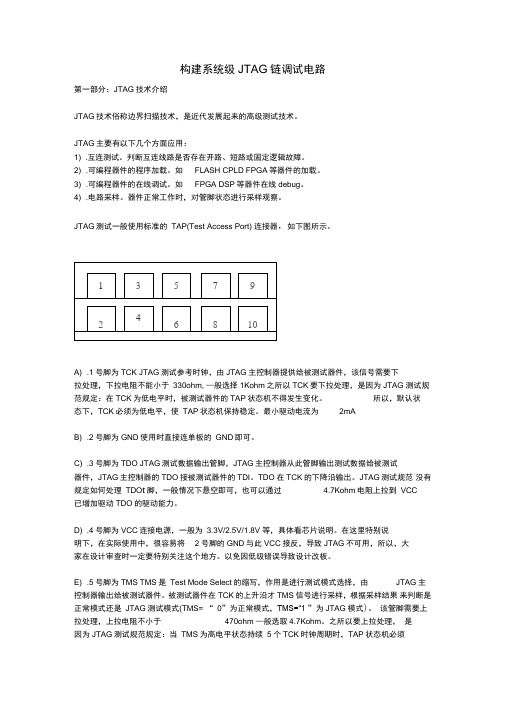

JTAG测试一般使用标准的TAP(Test Access Port) 连接器,如下图所示。

A) .1号脚为TCK JTAG测试参考时钟,由JTAG主控制器提供给被测试器件,该信号需要下拉处理,下拉电阻不能小于330ohm, —般选择1Kohm之所以TCK要下拉处理,是因为JTAG 测试规范规定:在TCK为低电平时,被测试器件的TAP状态机不得发生变化。

所以,默认状态下,TCK必须为低电平,使TAP状态机保持稳定。

最小驱动电流为2mAB) .2号脚为GND使用时直接连单板的GND即可。

C) .3号脚为TDO JTAG测试数据输出管脚,JTAG主控制器从此管脚输出测试数据给被测试器件,JTAG主控制器的TDO接被测试器件的TDI。

TDO在TCK的下降沿输出。

JTAG测试规范没有规定如何处理TDO t脚,一般情况下悬空即可,也可以通过 4.7Kohm电阻上拉到VCC已增加驱动TDO的驱动能力。

D) .4号脚为VCC连接电源,一般为3.3V/2.5V/1.8V 等,具体看芯片说明。

在这里特别说明下,在实际使用中,很容易将2号脚的GND与此VCC接反,导致JTAG不可用,所以,大家在设计审查时一定要特别关注这个地方。

以免因低级错误导致设计改板。

E) .5号脚为TMS TMS是Test Mode Select的缩写,作用是进行测试模式选择,由JTAG主控制器输出给被测试器件。

被测试器件在TCK的上升沿才TMS信号进行采样,根据采样结果来判断是正常模式还是JTAG测试模式(TMS= “ 0”为正常模式,TMS=“1 ”为JTAG模式)。

JTAG简介JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

现在,JTAG接口还常用于实现ISP(In-System P rogrammable�在线编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对PSD芯片内部的所有部件进行编程具有JTAG口的芯片都有如下JTAG引脚定义:TCK——测试时钟输入;TDI——测试数据输入,数据通过TDI输入JTAG口;TDO——测试数据输出,数据通过TDO从JTAG口输出;TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST——测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

JTAG内部有一个状态机,称为TAP控制器。

TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。

图1为TAP控制器的状态机框图。

2 JTAG芯片的边界扫描寄存器JTAG标准定义了一个串行的移位寄存器。

寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。

交流JTAG跟我学JTAG协议破解——第一弹初识

JTAGTAP状态机

摘要:JTAG协议是一种用来连接单片机及多媒体芯片的标准接口,

它是芯片的一个特殊接口,可以实现对芯片的编程、调试,以及JTAG状

态机的结构,为JTAG的正确使用提供了理论依据,使得我们能够更好地

理解JTAG协议,正确应用它。

本文介绍JTAG接口及JTAGTAP状态机的运

行机制,有助于进一步了解JTAG协议并掌握它的破解技术。

关键词:JTAG协议;TAP状态机;运行机制

1. introduction

JTAG(Joint Test Action Group)是一种专业性的接口标准,它使得

系统设计人员能够编写系统测试代码,并将系统芯片插入测试设备,运行

测试程序和捕获数据。

随着芯片的微缩,调试和设计芯片的需求越来越多,JTAG协议提供了一种很好的方式来处理这些问题。

2.JTAG接口

JTAG接口通常由4个部分组成,分别是TDI(Test Data In),

TDO(Test Data Out),TCK(Test Clock)和TMS(Test Mode Select)。

TDI

和TDO通过这个接口传输测试数据;TCK是控制时钟信号,设备使用它来

确定传输的位比特流;而TMS是控制模式选择,它用来控制设备的模式,

比如测试模式、调试模式等。

JTAGTAP状态机是JTAG设备的核心部分,它的目的是监控所有以TMS

为基础的信号状态,并根据信号的变化将设备移动到正确的状态。

超大规模集成电路设计272 8.4.2 边界扫描电路结构边界扫描电路包括测试访问端口TAP(Test Access Port)、TAP控制器(TAP Controller)、指令及数据寄存器(Instruction and Data Register)、边界扫描单元(BSC)。

其结构如图8.12所示。

图8.12 边界扫描电路结构边界扫描逻辑是通过测试存取口(TAP)存取的,它由IEEE标准规定的四个必需引脚和一个可选引脚组成。

四个必需引脚包括:测试状态选择(TMS),测试时钟(TCK),测试数据输入(TDI)和测试数据输出(TDO)。

部分器件提供TRST用于复位JTAG数据和指令寄存器。

TCK 为低时测试逻辑中的存储单元保持不变,在TCK的上升沿采样TMS和TDI,在TCK的下降沿后TDO变化。

只有在扫描时(Shift-DR or shift-IR)TDO输出才有效。

8.4.3 TAP控制器及指令集TAP控制器由一个包含16个状态的有限状态机构成,它控制了指令和数据寄存器的操作。

TCK为其时钟,TMS用于决定状态机的跳转。

TAP控制器在芯片上电时复位,也可通过TRST端口施加复位脉冲,或使TMS保持高电平至少5个TCK Cycle的方法复位。

TAP控制器的Test-Logic-Reset状态抑制测试逻辑,并使器件处于正常工作模式。

由状态转换图可看出,无论TAP控制器现处于何种状态,都可以通过将TMS保持高电平至少5个TCK Cycle的方法使其返回Test-Logic-Reset状态。

Run-Test/Idle主要用于执行BIST 操作。

其他的TAP控制器状态转换可简化为三个基本操作:Capture、Shift、Update。

当TAP处于Capture状态时,数据或指令在TCK上跳沿并行地装载入数据或指令寄存器的移位单元。

在Shift状态,移位单元中的数据或指令由TDO端口串行移位输出,同时通过TDI端口移入新的数据,此过程一直持续到所有的新数据或指令位全部载入为止。

JTAG技术俗称边界扫描技术,是近代发展起来的高级测试技术。

随着电子技术的高速发展,电路已经进入超大规模时代,芯片的封装技术也日新月异,从最初的DIP到QFP,已经当今的BGA,电路的物理可测试性正在逐渐消失。

为了寻找更先进的测试技术,1985年,IBM、AT&T、Texas Instruments、Philips、Siemens、Alcatel、Ericsson等几家公司联合成立了JETAG(Joint European Test Action Group欧洲联合测试行动小组),并提出边界扫描技术。

通过存在于器件输入输出管脚与内核电路之间的BSC(Boundary Scan Cell)对器件及其外围电路进行测试。

1986年,一些欧洲之外的其他公司加入该组织,JETAG组织的成员已不仅仅局限在欧洲,所以该组织名称由JETAG更改为JTAG。

1990年,IEEE(Institute of Electrical and Electronics Engineers,美国电气和电子工程师协会)正式承认JTAG标准,命名为IEEE1149.1-1990。

JTAG主要有以下几个方面应用:1).互连测试。

判断互连线路是否存在开路、短路或固定逻辑故障。

2).可编程器件的程序加载。

如FLASH、CPLD、FPGA等器件的加载。

3).电路采样。

器件正常工作时,对管脚状态进行采样观察。

JTAG测试一般使用标准的TAP(Test Access Port)连接器,如下图所示。

A).1号脚为TCK。

JTAG测试参考时钟,由JTAG主控制器提供给被测试器件,该信号需要下拉处理,下拉电阻不能小于330ohm,一般选择1Kohm。

之所以TCK 要下拉处理,是因为JTAG测试规范规定:在TCK为低电平时,被测试器件的TAP 状态机不得发生变化。

所以,默认状态下,TCK必须为低电平,使TAP状态机保持稳定。

最小驱动电流为2mA。

A、基本的状态机知识B、基本的C语言能力,包括位操作、常用宏定义、数组、指针等常见内容C、会使用一种单片机D、熟悉SPI协议的物理原理E、对JTAG的好奇和兴趣[ 序言]JTAG协议是目前应用最广泛的下载和仿真协议,对协议的最初缔造者来说,这也许有点无心插柳柳成荫的感觉——最初的JTAG协议只是用来辅助专门的硬件质检部门对印刷电路进行检测的。

这些老账现不再提了我们现在看到的各种JTAG下载和仿真协议都是各生产厂商在原有JTAG协议的思想上进行扩充的,并不具有通用性,甚至连最基本的电路检测部分功能也被加以改造——比如,一个JTAG指令可能在大部分的版本中是4位长度的,而对于AVR32来说,一个JTAG指令却是5位。

总之,现在大行其道的JTAG协议,不变的部分就只有其核心TAP状态机了。

ARM有ARM的JTAG,AVR有AVR的JTAG,51有51的JTA G……在这样一个缺乏统一标准的“街头”JTAG时代,如果你想学好JTAG下载仿真协议的破解,就必须从TAP状态机开始。

[原理解析]在你被复杂的时序图弄得眼花缭乱之前,你应该首先记住以下的断言:A、JTAG协议的本质与SPI协议并没有什么不同,它等于一个复杂的S S状态机+变长的MOSI和MISO数据移位操作。

不过所谓的变长,都是事先约定好的。

B、JTAG协议是一个同步通讯协议,它是全双工的。

它的通讯原则是“以物易物”——即你如果想得到某些东西,你必须先给与相同长度的内容;你如果只是想发送一些数据,也会自动获取相同长度的内容,至于交换的内容是否有意义,这是另外一回事了。

C、JTAG协议无论多么复杂,实际上只有4根线起作用(有时候还有两根鸡肋的nSRST和TRST),他们分别是TMS、TCK、TDI和TDO,他们分别对应SPI协议里面的SS、S CK、MOSI和MISO。

在本质上,他们并没有什么不同。

即便是ARM的JTAG那么多的引脚,实际上起作用JT AG的也就这4根线而已。

D、JTAG的数据操作都是基于移位寄存器的。

E、如果JTAG协议在某个下载仿真协议中只是用来发送控制信息和少量的数据,而大量的数据传输是通过额外的其它引脚进行的,即便这个协议被称为JTAG仿真其本质也早已超过JTAG了,严格来说,不应该称之为JTAG。

因为JTAG协议中就只有4根线(有时候也算上n SRST和TRST)而已。

典型的如NEXUS协议。

说了这么多,我们终于可以开始正式的讲解了。

一、从SPI到JTAG如果熟悉SPI,你会发现SPI是如此的简单、和谐——一根用于二进制位同步的时钟线SCK,一根用于主机发送到从机的数据线MOSI(Master Out Slave In),一根用于从机发送到主机的数据线MISO(MasterIn Slave Out),外加一根用于复位SPI从机控制器以达到通讯同步的控制信号SS(不妨理解为SlaveSynchronization)。

如果乐意,你很容易就通过消减MOSI和MISO的方法获得精简的单向通讯。

前面我们提到,JTAG的数据操作都是基于移位寄存器的,这一点和SPI是相同的。

JTAG协议的核心在于能够有效地传输指令和数据,并且传输指令和数据的过程是能够明确的加以区别对待而不会造成歧义的。

如何实现这一功能呢?JTAG协议只是将原本用来复位从机的SS信号扩展为一个状态机。

而该状态机每一个状态都有两个状态触发——在TCK(也就是SCK)的上升沿,TMS(也就是SS)的电平决定了跳转的分支。

下图就是一个典型的TAP状态机,值得庆幸的是,该状态机所有JTAG 协议中都会遵守的部分。

如果这是你第一次研究TAP状态机,首先你不必去追究TAP究竟是哪些英文单词的缩写,因为Test AccessPort已经是过去很久的事情了,现在的JTAG状态机虽然功能没变,但早就从事其它“高科技”行业了。

第二眼看着附图,你会发现,其实整个状态机不过分为三个部分:信道选择部分、数据信道和指令信道。

所谓的信道选择,就是图中最顶上由四个状态组成的矩形,分别对应着四个状态:1、JTAG TAP状态机复位状态顾名思义,就是进入该状态,将导致整个硬件TAP 控制器复位,所有的寄存器都将被初始化。

在TCK的上升沿,TMS为低电平时,进入下一个状态;否则保持不变。

2、JTAG TAP的Run-Test/Idle状态其实就是“开工”和“休息”的选择分支点。

在TCK 的上升沿,TMS的高电平将导致状态切换,进入数据信道的通讯状态;否则保持不变。

3、JTAG TAP的Select-DR Scan状态Select DR Scan翻译成中文就是“选择数据移位寄存器进行移位操作”,简单说来,就是当我们在该状态下,TCK的上升沿读取到了TMS的低电平将直接进入数据信道的操作子状态机;在TCK的上升沿读取到了TMS的高电平,将切换到指令信道的通讯状态。

4、JTAG TAP的Select-IR Scan状态Select-IR Scan翻译成中文就是“选择指令寄存器进行移位操作”,简单来说,就是当我们在该状态下,TCK的上升沿读取到了TMS的低电平将直接进入指令信道的操作状态机;在TCK的上升沿读取到了TMS的高电平,将重新回到JTAG的复位状态。

数据信道和指令信道对应着两个子状态机,从本质上数据和指令并没有任何不同,只是习惯上,指令的长度固定为4个二进制位(AVR32的JTAG是5个),而数据则随着不同的指令选择了不同长度的指令寄存器,这个就需要具体查阅相关的协议说明了,比如JTA G IDCODE的长度固定为32位,而AVR32的复位指令却有5位(很多情况下别指望是8的倍数)。

根据阅读前面“选择部分4个状态机”的经验,大家应该对照着图片自己尝试去理解剩下的两个信道。

下面,我只就常见的几个状态进行解释(以数据信道为例,指令信道可以参考其内容)。

1、Capture DR状态前文说过,JTAG协议是基于移位寄存器的,其通讯具有“以物易物”的特性,在我们进入真正的数据传输之前,需要告知JTAG“准备通讯了哦?你有没有东西要给我哈?”,于是Capture DR就是一个给JTAG机会将需要传达给我们的数据放入指定的移位寄存器中的状态。

2、Shift DR状态这个状态就是通过TDI和TDO进行数据传输的状态。

需要说明的是,即便进入了该状态,TMS上的电平在TCK的上升沿也是会被读取的,从图中看到,一旦在TMS上读取到高电平,系统就会跳出Shift DR状态如果此时数据没有传输完成,造成的后果是不确定的。

请大家注意,我所说的是不确定,而不是“很严重”:同样是因为移位寄存的传输特性,有时候并不要求一定要将所有的数据都完整的进行传输,比如在AVR32中,针对SAB的数据操作,往往只需要进行最关键的部分,详细地内容可以参照相关的数据手册;但有的时候,数据的不完整传输则会导致很严重的后果,这取决于具体的JTAG通讯协议。

所以,为了保险起见,一旦进入Shift DR状态,在发送最后一个数据之前,请保持TMS为低电平,当要发送最后一个数据时,应该将TMS设置为高电平,这样,当TCK跳变为上升沿时,系统既完成了最后一个数据的传输,也成功的退出了Shift DR状态。

3、Exit1 DR状态该状态提供了我们一个在刚才输入的数据生效前,重新修改的机会。

一般情况下,我们直接保持TMS的高电平,并在TCK的上升沿驱动TAP状态机,直接进入Upd ate-DR状态。

4、Update-DR状态顾名思义,就是使我们输入的数据生效——一般JTAG 内部的动作就是触发一个锁存信号,将移位寄存器中的内容并行的读取到对应的寄存器中。

Update-DR有两个出口,一个是,TMS的低电平对应Run-test/Idle,还有一个是TMS的高电平对应的Select-DR Scan。

这两个操作看似区别不大,但是意义非凡。

前者往往会导致JTAG内部产生额外的时序(比如发生一个信号,表示完成了一个特定的周期操作,在AVR的JTAG下载中有此实例);后者则表示完成了一次数据操作,将进行下一个数据的操作,但是这些操作属于同一个操作周期。

当然有些情况下,这两种方法是没有区别的。

关于理论部分的讲解,到此为止,留下一个小小的思考,当T AP状态机处于一个未知的状态时,如何才能通过一个统一的操作使其回到Run-Test/Idel状态呢?给一个小小的提示,针对TAP状态机的TMS信号,给定固定的电平,在有限的TCK上升沿中,完成状态机的复位。

那么这个有限的范围最少是多少个时钟周期?这个固定的电平究竟是高还是低呢?[实际应用]下面的代码是我应用在Snail mkII DEMO中用来操作TAP状态机的实际代码,它根据用户输入的TAP控制流,产生TAP控制时序,比如我们需要从Run-Test/Idle状态进入Shift-IR状态,根据TAP状态图,我们很容易得出需要产生的TMS信号依次为1(进入Select DR Scan)1(进入Select IR Scan)0(进入Capture IR)0(进入Shift-IRScan),一共四个二进制位,根据从LSB到MSB依次发送的顺序,需要传送给函数的值就是0x03,长度为4。

需要注意的是,进入Shift-IR状态以后,有可能要设置此时的需要TMS保持的电平状态,因此,实际传送的0x03其内容应该是1 1 0 0 0,最后一个0表示完成前面4个TMS时序的输入以后,TMS 保持低电平。

最后一个0不计入长度。

/************************************************************ 函数说明:JTAG TAP 状态机控制函数** 输入:控制序列,序列长度** 输出:无** 调用函数:无** -------------------------------------------------------- ** 使用说明** 1、TMS在TCK上升边沿输出状态控制量。

** 2、连续5个TCK周期在TMS上输出高电平将进入Test- ** Logic-Reset模式。

** 3、使用该函数时,请将状态机跳转以后TMS需要保** 持的电平也作为一个有效输入加入到序列的末尾** 但描述序列长度的数值不需要相应的增加。

************************************************************/void JTAG_TAP_Control(UINT8 chCTRStream,UINT8 chLength){UINT8 n = 0;//状态机控制序列for (n = 0;n < chLength;n++){CLR_TCKif (chCTRStream & BIT(n)){SET_TMS}else{CLR_TMS}JTAG_CLOCK_DELAYSET_TCK/* 延时部分*/JTAG_CLOCK_DELAY}//保持电平if (chCTRStream & BIT(chLength)){SET_TMS}else{CLR_TMS}}为了方便使用,我们可以将一些常用的TAP操作用宏进行封装,从而获得较高的代码可读性:# define JTAG_TAP_TEST_LOGIC_RESET JTAG_ TAP_Control(0x1F,6);# define JTAG_TAP_SHIFT_IRJTAG_TAP_Control(0x03,4);。