状态机学习文档

- 格式:doc

- 大小:170.00 KB

- 文档页数:5

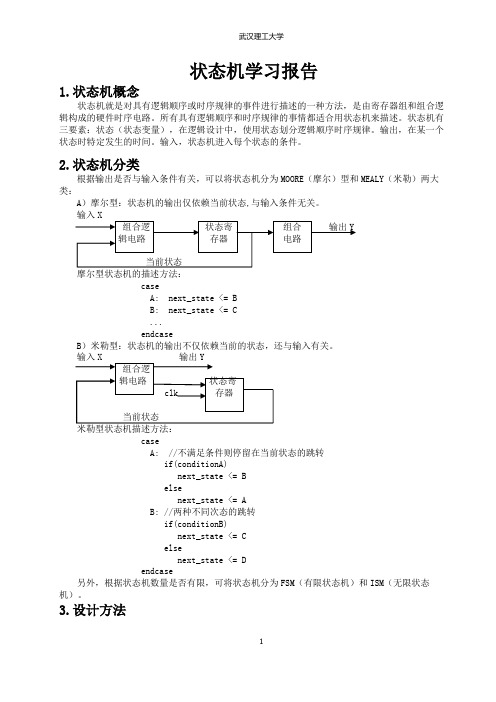

状态机学习报告1.状态机概念状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法,是由寄存器组和组合逻辑构成的硬件时序电路。

所有具有逻辑顺序和时序规律的事情都适合用状态机来描述。

状态机有三要素:状态(状态变量),在逻辑设计中,使用状态划分逻辑顺序时序规律。

输出,在某一个状态时特定发生的时间。

输入,状态机进入每个状态的条件。

2.状态机分类根据输出是否与输入条件有关,可以将状态机分为MOORE(摩尔)型和MEALY(米勒)两大类:A)摩尔型:状态机的输出仅依赖当前状态,与输入条件无关。

摩尔型状态机的描述方法:caseA: next_state <= BB: next_state <= C...endcaseB)米勒型:状态机的输出不仅依赖当前的状态,还与输入有关。

caseA: //不满足条件则停留在当前状态的跳转if(conditionA)next_state <= Belsenext_state <= AB: //两种不同次态的跳转if(conditionB)next_state <= Celsenext_state <= Dendcase另外,根据状态机数量是否有限,可将状态机分为FSM(有限状态机)和ISM(无限状态机)。

3.设计方法状态机的描述方式有:状态转移图、状态转移列表和HDL语言描述。

状态转移图经常在设计规划阶段定义逻辑功能时使用,也可以在分析已有源代码中的状态机时使用,这种图形化的描述方式有助于理解设计意图。

状态转移列表是用列表的方式描述状态机,是数字逻辑电路常用的设计方法之一,经常被用于状态化简,对于可编程逻辑设计而言,由于可用逻辑资源比较丰富,而且状态编码要考虑设计的稳定性、安全性等因素,所以并不经常使用状态转移列表优化状态。

使用HDL语言描述状态机应具有一定的灵活性,通过使用一些规范的描述方法,可以使HDL语言描述状态机更安全、更稳定、更高效、更易于维护。

Verilog] 同步状态机的实现状态机一般包括组合逻辑和寄存器逻辑两部分。

组合电路用于状态译码和产生输出信号,寄存器用于存储状态。

状态机的下一个状态及输出不仅与输入信号有关,还与寄存器当前状态有关。

根据输出信号产生方法的不同,状态机可分为米里(Mealy)型和摩尔(Moore)型。

前者的输出是当前状态和输入信号的函数,后者的输出仅是当前状态的函数。

在硬件设计时,根据需要决定采用哪种状态机。

状态编码状态编码又称状态分配。

通常有多种编码方法,编码方案选择得当,设计的电路可以简单;反之,电路会占用过多的逻辑或速度降低。

设计时,须综合考虑电路复杂度和电路性能这两个因素。

下面主要介绍二进制编码、格雷编码和独热码。

二进制编码和格雷码都是压缩状态编码。

二进制编码的优点是使用的状态向量最少,但从一个状态转换到相邻状态时,可能有多个比特位发生变化,瞬变次数多,易产生毛刺。

格雷编码在相邻状态的转换中,每次只有1个比特位发生变化,虽减少了产生毛刺和一些暂态的可能,但不适用于有很多状态跳转的情况。

独热码是指对任意给定的状态,状态向量中只有1位为1,其余位都为0。

n状态的状态机需要n个触发器。

这种状态机的速度与状态的数量无关,仅取决于到某特定状态的转移数量,速度很快。

当状态机的状态增加时,如果使用二进制编码,那么状态机速度会明显下降。

而采用独热码,虽然多用了触发器,但由于状态译码简单,节省和简化了组合逻辑电路。

独热编码还具有设计简单、修改灵活、易于综合和调试等优点。

对于寄存器数量多、而门逻辑相对缺乏的FPGA 器件,采用独热编码可以有效提高电路的速度和可靠性,也有利于提高器件资源的利用率。

独热编码有很多无效状态,应该确保状态机一旦进入无效状态时,可以立即跳转到确定的已知状态。

有限状态机的Verilog实现用Verilog 语言描述有限状态机可使用多种风格,不同的风格会极大地影响电路性能。

通常有3种描述方式:单always块、双always 块和三always块。

第九章状态机状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法方法。

状态机的三个基本要素状态机的三个基本要素::状态状态::也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

比如:设计伪随机码发生器时,可以用移位寄存器序列作为状态;在设计电机控制电路时,可以以电机的不同转速作为状态;在设计通信系统时,可以用信令的状态作为状态变量等。

输出输出::输出指在某一个状态时特定发生的事件。

如设计电机控制电路中,如果电机转速过高,则输出为转速过高报警,也可以伴随减速指令或降温措施等。

输入输入::指状态机中进入每个状态的条件。

有的状态机没有输入条件,其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态一、状态机状态机分为::状态机分为有限状态机((Finite State Machine,FSM)√ 有限状态机无限状态机((Infinite State Machine,ISM) 无限状态机易维护。

FSM设计要清晰易懂设计要清晰易懂、、易维护有限状态机的设计什么是有限状态机((FSM ) 什么是有限状态机FSM的种类和不同点设计举例什么是有限状态机?什么是有限状态机?-有限状态机是由寄存器组和组合逻辑构成的硬件时序电路;-其状态其状态((即由寄存器组的1和0的组合状态所构成的有限个状态有限个状态))只能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态;-究竟转向哪一状态不但取决于各个输入值究竟转向哪一状态不但取决于各个输入值,,还取决于当前状态于当前状态。

-状态状态机可用于产生在时钟跳变沿时刻开关的复杂的机可用于产生在时钟跳变沿时刻开关的复杂的控制逻辑控制逻辑,,是数字逻辑的控制核心是数字逻辑的控制核心。

Moore 状态机下一个状态= F(当前状态当前状态,,输入信号)输出信号= G(当前状态);下一状态的逻辑输出逻辑G状态寄存器输入输出当前状态激励信号时钟同步的状态机结构(Moore 状态机)F时钟信号clk clk输入Moore型状态机Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);下一状态输出逻辑输入时钟同步的状态机结构(Mealy 状态机)的逻辑FG状态寄存器时钟信号clkclk 输入输出当前状态激励信号Mealy型状态机带流水线输出的Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);输出输出输输出流带流水线输出的Mealy 状态机下一状态的逻辑F逻辑G 状态寄存器时钟信号clkclk 输入入当前状态激励信号水线寄存器clk 输入有限状态机的Verilog 描述定义模块名和输入输出端口定义模块名和输入输出端口;;定义输入定义输入、、输出变量或寄存器输出变量或寄存器;;定义时钟和复位信号定义时钟和复位信号;;定义状态变量和状态寄存器;定义状态变量和状态寄存器;用时钟沿触发的always 块表示状态转移过程块表示状态转移过程;;在复位信号有效时给状态寄存器赋初始值在复位信号有效时给状态寄存器赋初始值;;描述状态的转换过程描述状态的转换过程::符合条件符合条件,,从一个状态到另外一个状态一个状态,,否则留在原状态否则留在原状态;;验证状态转移的正确性验证状态转移的正确性,,必须完整和全面必须完整和全面。

第五讲状态机设计及其指导原则1/ 38第五讲状态机设计及其指导原则1/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则1 状态机是一种设计思想方法2状态机结构3状态机设计的其他技巧4状态机设计步骤第五讲状态机设计及其指导原则2/ 38第五讲状态机设计及其指导原则2/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学z 状态机是一种设计思想方法第五讲状态机设计及其指导原则3/ 38第五讲状态机设计及其指导原则3/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学原语描述module noconditional (clk,nrst,state,event);input clk,nrst input state;output event;reg event;reg [2:0] CS; //CurrentState reg[2:0] NS; //NextStateparameter [2:0] //one hot with zero idleidle = 3’b000,dorm = 3'b001,diningroom = 3'b010,classroom = 3'b100;第五讲状态机设计及其指导原则4/ 38第五讲状态机设计及其指导原则4/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学//sequential state transitionalways @ (posedge clk or negedge nrst)if (!nrst) CS <= idle; else CS <= NS; //combinational condition judgment always @ (nrst or CS)begincase (CS)idle:idle_task;NS = dorm;dorm:dorm_task;NS = diningroom;diningroom:diningroom_task;NS = classroom;classroom:classroom_task;NS = dorm;default:idle_task;NS = dorm;endcase end endmodule第五讲状态机设计及其指导原则5/ 38第五讲状态机设计及其指导原则5/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则6/ 38第五讲状态机设计及其指导原则6/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学 状态机的本质--对具有逻辑顺序或时序规律事件的一种描述方法 状态机的两个应用思路:-从状态变量入手-明确电路的输出的关系第五讲状态机设计及其指导原则7/ 38第五讲状态机设计及其指导原则7/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学对于逻辑电路而言,小到一个简单的时序逻辑,大到复杂的微处理器,都适合用状态机方法进行描述。

主主主主主主

以下以主状态机在某个状态等待N 个clk 为例子说明主状态机和子状态机之间的配合

与交互。

假定主状态机等待N 个CLK 的状态为state_nw,之前的状态为state_nw-1,之后的状态为state_nw+1.

用于主状态机和子状态机之间交互的连线有2根。

分别是主状态机通知子状态机的START 信号,和子状态机通知主状态机的DONE 信号。

当主状态机需要等待N 个clk 的时候即进入state_nw 状态,主状态机输出译码得到DONE 信号为高点平。

并且只要主状态机维持在

state_nw 状态,DONE 就保持高电平。

子状态机默认是在IDLE 状态,即计数值始终为0。

IDLE 状态下,只要START 信号变高,则子状态机随即进入计数值为1的状态,计数值为1的状态下,只要START 信号为高,则进入计数值为2的状态,如果START 信号为低,则进入IDLE 状态。

例如计数器的模数为10,则当进入计数值为10的状态时,计数器子状态机DONE 信号从低变为高,下个状态即为IDLE 状态,IDLE 状态中,DONE

信号为低,所以主状态机在等待10个clk 时收到来自子状态机的宽度为1个clk 的DONE 信号。

主状态机在state_nw 状态下,一直判断来自子状态机的DONE 信号,只要DONE 信号为高随即进入state_nw+1状态,并且STATE 信号译码为低。

对于子状态机来说,只要START 信号为低,随即进入IDLE 状态。

计数值始终为0,并且DONE 信号输出为低。