基于FPGA的SOPC实践教程

- 格式:ppt

- 大小:188.50 KB

- 文档页数:9

基于FPGA的数字时钟设计摘要:EDA技术在电子系统设计领域越来越普及,本设计主要利用VHDL和C 语言在FPGA实验板上设计一个电子数字钟,它的计时周期为24小时,显示满刻度为23时59分59秒、。

总的程序由几个各具不同功能的单元模块程序拼接而成,其中包括分频程序模块、时分秒计数模块、处理器及外设模块,并且使用QuartusII运用VHDL语言对分频和计数两个模块进行硬件电路设计和电路波形仿真,运用sopc技术嵌入内核并创建了系统所需的外部设备FLASH和SRAM 软件通过使用NiosII运用C语言进行编程然后下载到硬件电路中,并在FPGA实验板上进行调试和验证。

该设计采用自顶向下、混合输入方式(原理图输入—顶层文件连接和VHDL语言输入—各模块程序设计)实现数字钟的设计、下载和调试。

关键词:数字钟;FPGA;VHDL语言;C语言;SOPC技术;1、选题背景和研究内容近年来,随着数字集成电路技术的发展,用以前传统的方法进行芯片或系统设计已不能满足要求, 迫切需要提高设计效率。

能大大降低设计难度的VHDL设计方法正在被越来越广泛的采用。

VHDL 即超高速集成电路硬件描述语言,诞生于1982 年。

1987年底, VHDL被IEEE和美国国防部确认为标准硬件描述语言。

此后VHDL 在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。

1993年IEEE对VHDL 进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL 的内容,公布了新版本的VHDL,即IEEE标准的1076--1993 版本。

现在, VHDL作为IEEE的工业标准硬件描述语言,已成为通用硬件描述语言。

现在电子钟产品可谓百家争鸣,市场上到处可见一些功能齐全的设备,可能基于单片机的比较多,用FPGA设计电子钟可能比较少。

因为两个都可以实现同样的功能,而FPGA芯片的价格远比单片机高。

出于利润,当然会选择开发成本少的产品。

3.2 构建比较复杂的Nios II系统实验实验目的:1. 强化使用IP核构建系统的设计思想,学习使用SDRAM 等IP软核的方法;2. 学习使用MegaWizard Plug-In Manager添加PLL IP软核进行时钟倍频的方法。

实验内容:在前面实验的基础上添加SDRAM及用于倍频的锁相环,构建比较复杂的Nios II系统。

实验原理:FPGA片内嵌入式锁相环PLL可以与一输入的时钟信号同步,并以其作为参考信号实现锁相,从而输出一至多个同步倍频或分频的片内时钟,以供逻辑系统应用。

与直接来自外部的时钟相比,这种片内时钟可以减少时钟延时和时钟变形,减少片外干扰;还可以改善时钟的建立时间和保持时间。

实验设备:SOPC核心板、USB-Blaster下载线、电源。

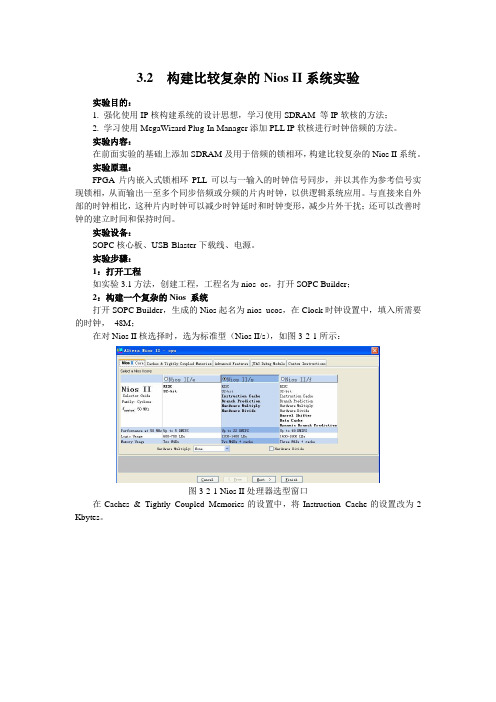

实验步骤:1:打开工程如实验3.1方法,创建工程,工程名为nios_os,打开SOPC Builder;2:构建一个复杂的Nios 系统打开SOPC Builder,生成的Nios起名为nios_ucos,在Clock时钟设置中,填入所需要的时钟,48M;在对Nios II核选择时,选为标准型(Nios II/s),如图3-2-1所示:图3-2-1 Nios II处理器选型窗口在Caches & Tightly Coupled Memories的设置中,将Instruction Cache的设置改为2 Kbytes。

图3-2-2 指令缓存设置其它的按默认设置即可,更改cpu_0名称为cpu。

添加SDRAM控制器软核,双击Memory下的SDRAM Controller,数据位设置为16位,片选1位,4块banks,地址线12行,8列,其他参数设置及时序设置见图3-2-4:其中,Memory Profile的设置如图3-2-3所示:图3-2-3 SDRAM基本参数设置Timing的设置如图3-2-4所示:图3-2-4 SDRAM时序参数设置将sdram_0重命名为sdram,注意sdram的参数设置必须正确,否则将不能使用,时序参数的设置可以参考芯片的数据手册根据需要适当调整。

黑龙江科技大学SOPC设计基础实验报告学院:黑龙江科技大学学号: ********** 姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容1 添加SOPC硬核1,.创建一个工程,取名。

2.添加.bdf文件,取名和工程名同名。

3.在Tools菜单下打开SOPC Builder。

4.创建系统,取名NIOS2,选择使用Verilog语言。

5.设置系统主频和指定FPGA。

6.加入NIOS2 CPU模块,选择型号,并设置相关参数。

7.依次添加定时器、Butoon PIO、LCD控制器、外部RAM和Flash接口、外部RAM和Flash总线、JTAG UART接口,并将这些模块命名成自己熟悉的名字。

8.分配IP模块的地址和中断号9.配置NIOS2 系统10.生成NIOS2并加入到工程中2 创建PLL器件由于Sdram的时钟是由fpga提供的,所以要创建一个PLL器件来实现对时钟的控制,Quartus II提供了Megawizard Plug-In Manager工具对Plug-In器件以及IP Core进行创建和管理,在Megawizard Plug-In Manager中可以创建各种逻辑门电路以及存储器件。

选择Tools/Megawizard Plug-In Manager点击“Next”,进入Manager,选择“IO/ALTPLL”,选择输出文件类型为“VHDL”,选择输出文件的名字“mypll”点击“Next”,选择器件的速度为8,输出的频率为50MHz,其它设置不变。

点击“Next”,去掉复位、使能等选项点击“Next”,进入Clock c0的设定。

改变“Enter output clock frequency”为50MHz点击“Next”,进入Clock c1的设定,不作改变点击“Next”进入Clock e0的设定。

DSP Builder可以帮助用户完成基于FPGA的DSP系统设计,除了可以进行图形化的系统建模外,DSP Builder还可以自动完成大部分的设计过程和仿真,直至把设计文件下载到FPGA 芯片中。

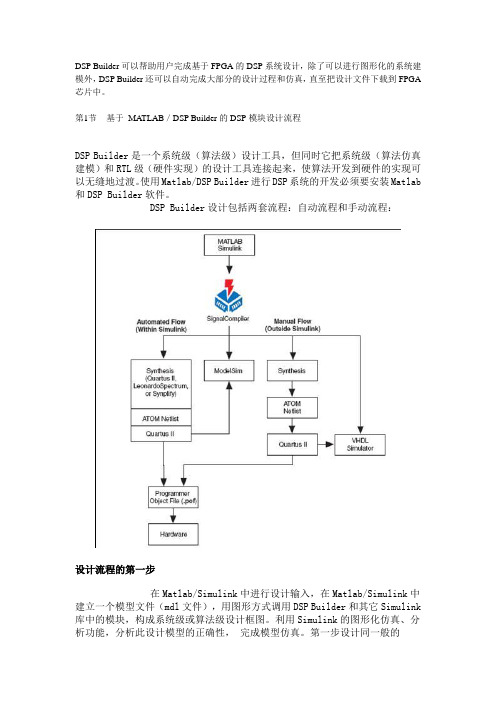

第1节基于MATLAB/DSP Builder的DSP模块设计流程DSP Builder是一个系统级(算法级)设计工具,但同时它把系统级(算法仿真建模)和RTL级(硬件实现)的设计工具连接起来,使算法开发到硬件的实现可以无缝地过渡。

使用Matlab/DSP Builder进行DSP系统的开发必须要安装Matlab 和DSP Builder软件。

DSP Builder设计包括两套流程:自动流程和手动流程:设计流程的第一步在Matlab/Simulink中进行设计输入,在Matlab/Simulink中建立一个模型文件(mdl文件),用图形方式调用DSP Builder和其它Simulink 库中的模块,构成系统级或算法级设计框图。

利用Simulink的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

第一步设计同一般的Matlab/Simulink建模过程几乎没什么区别,所不同的是,设计采用了DSP Builder库。

设计流程第二步通过SignalCompiler把Simulink的模型文件转化为硬件描述语言文件,以供其它的EDA(Quartus II、ModelSim 等)软件处理,这些软件不能直接处理Matlab/Simulink产生的模型文件,那么DSP Builder中的SignalCompiler模块用于完成模型文件到硬件描述语言文件的转换,转换之后的HDL文件是RTL级(寄存器传输级,即可综合的格式)。

设计流程的第三步执行RTL级的仿真,DSP Builder 支持自动流程的ModelSim仿真。

用户也可以利用第二步产生的VHDL文件使用其它的仿真工具软件手动地进行仿真。

设计流程的第四步使用第二步SignalCompiler产生的VHDL文件进行RTL级的综合,网表产生和适配等处理,DSP Builder支持自动流程和手动流程两种方式:自动流程中可以选择让DSP Builder自动调用Quartus II等EDA软件来完成相应的工作;手动模式允许用户选择相应的软件来完成相应的工作,手动模式需要更多的干预,同时提供了更大的灵活性,用户可以指定综合、适配等过程的条件。

SOPC实验指导书钮文良韩玺编著北京联合大学信息学院2007年12月6日目录第1章SOPC实验系统介绍 (3)1.1 系统硬件平台设计 (3)1.2 系统软件实验开发 (7)1.3 SOPC系统实验介绍 (8)第2章SOPC基本概念与基本原理 (10)2.1 SOPC技术 (10)2.2 基于FPGA嵌入IP软核的SOPC系统 (11)2.3 SOPC设计 (13)第3章SOPC设计开发案例 (14)3.1 Nios控制LED实验 (14)3.2 构建比较复杂的Nios II系统实验 .................................. 错误!未定义书签。

3.3 SOPC下μC/OS II操作系统移植实验............................ 错误!未定义书签。

3.4 Nios II控制下的UART串行接口通信实验 .................. 错误!未定义书签。

3.5 底板8×8点阵LED图形实验 ......................................... 错误!未定义书签。

3.6 VGA&SVGA接口显示器彩条信号发生器实验............ 错误!未定义书签。

3.7 按键控制数码管计数器实验 ........................................... 错误!未定义书签。

3.8 信号发生器设计实验 ....................................................... 错误!未定义书签。

3.9 底板键盘控制SOPC实验板数码管实验 ....................... 错误!未定义书签。

3.10 4位按键控制下的LED、数码管SOPC计数实验...... 错误!未定义书签。

3.11 基于SOPC的128*64 LCD显示实验 .......................... 错误!未定义书签。

Quartus ModelSim DSP HardCopy(1)在采用NIOS II处理器设计嵌入式系统时,一般遵循如下的流程:1.分析系统需求说明,包括功能需求和性能要求等;2. 建立Quartus II工程,建立顶层实体;3. 调用SOPC Builder生成一个用户定制的系统模块(包括NIOS II及标准外设模块);4. 将SOPC系统模块集成到硬件工程中,并添加一些模块,可以是Altera公司提供的LPM模块、第三方提供的或用户自己定制的模块;5. 在顶层实体中,将SOPC系统模块、Altera的LPM或用户自定义的模块连接起来;6. 分配引脚和编译工程,编译生成系统的硬件配置文件.sof和.pof文件;7. 下载工程,验证,将配置文件下载到开发板上进行验证;8. 软件开发,开发可以使用IDE开发环境,也可以使用SDK Shell;9. 编译软件工程,生成可执行文件.elf;10. 调试程序,将硬件配置文件下载到开发板,将可执行文件下载到RAM,直到软硬件协同工作。

在上面的过程中,用到的软件有Quartus II、Nios II SDK shell或Nios II IDE、ModelSim 等,如果进行DSP的开发,还会用到Matlab和DSPBuilder。

Quartus II用来建立硬件的系统,其中包括SOPC Builder工具,SOPC Builder用来建立SOPC系统模块,Quartus II支持多种设计方式,如原理图,硬件描述语言等,硬件描述语言的方式支持VHDL和Verilog。

软件开发使用Nios II SDK shell或Nios II IDE,IDE开发环境采用图形化的开发环境,使用方便直观。

而SDK shell采用命令窗口的方式进行程序的调试。

ModelSim是HDL编译仿真软件,用于对设计的硬件系统进行RTL级的仿真。

DSP Builder是Altera公司推出的数字信号处理开发软件,用来实现算法和硬件实现的无缝过渡,用户可以在Matlab的Simulink中完成算法模型的仿真、验证,然后通过SignalCompiler将模型文件转换成硬件描述语言的文件(2)支持Nios II的FPGACyclone和Cyclone II系列Stratix和Stratix II系列HardCopy器件HardCopy IIHardCopy StratixHardCopy APEX三代Cyclone和Cyclone II系列Cyclone 于2002年12月份推出。

2010年8月襄樊学院学报Aug., 2010 第31卷第8期Journal of Xiangfan University V ol.31 No8基于FPGA的SOPC设计王培元(襄樊学院物理与电子工程学院,湖北襄樊 441053)摘要:本SOPC系统在Altera 公司Cyclone 系列芯片EP1C6Q240中移植Nios II嵌入式处理器,作为核心控制电路;利用FPGA丰富的可编程逻辑资源和IP软核构成嵌入式处理器的接口模块,实现对SDRAM存储器、FLASH存储器、LCD液晶显示器、独立键盘、LED等硬件的控制;软件设计采用开源的uC/OS-II嵌入式实时操作系统,完成一个嵌入式系统硬件设计. 经调试运行,在该系统上成功进行了推箱子游戏,验证了基于FPGA硬件设计的可行性,实现嵌入式实时多任务软件的开发.关键字:FPGA;SOPC;Nios II;uC/OS-II中图分类号:TN47 文献标志码:A 文章编号:1009-2854(2010)08-0042-03SOPC(System-on-a-Programmable-Chip),全称是可编程片上系统. 首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能[1]. 随着FPGA芯片的发展,SOPC技术的得到了飞速发展,利用FPGA设计SOPC,为现在越来越复杂的产品所带来的竞争压力提供了高效的解决方案,在高速等高端产品中应用越来越广泛.SOPC设计是nios系统+硬实时部分+逻辑电路的一个组合体. 其中硬实时部分和逻辑电路在FPGA芯片内可以完美的得到实现. 本设计采用ALTERA公司的Nios II软核和FPGA芯片EP1C6Q240实现了一个SOPC的设计.1 系统总体设计本SOPC系统主要实现推箱子游戏,系统由一个32bit NiosII软核处理器、液晶显示器、SDRAM、FLASH、键盘等组成。