FPGA_CPLD设计开发流程快速入门指南 ALTERA篇QuartusII 史上最全

- 格式:pdf

- 大小:1.20 MB

- 文档页数:9

第3章Quartus II使用入门及FPGA设计流程Quartus II可编程逻辑开发软件是Altera公司为其FPGA/CPLD芯片设计推出的专用开发工具,是Altera公司最新一代功能更强的EDA开发软件,可完成从设计输入,综合适配,仿真到下载的整个设计过程。

Quartus II提供了一个完整的多平台开发环境,它包含FPGA和CPLD整个设计阶段的解决方案。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件设计、综合、布局和布线,验证和仿真。

Quartus II也可以直接调用Synplify Pro、ModelSim等第三方EDA 工具来完成设计任务的综合与仿真。

Quartus II与MATLAB和DSP Builder结合可以进行基于FPGA的DSP系统开发,方便快捷。

Quartus II还内嵌SOPC Builder,可实现SOPC系统的开发。

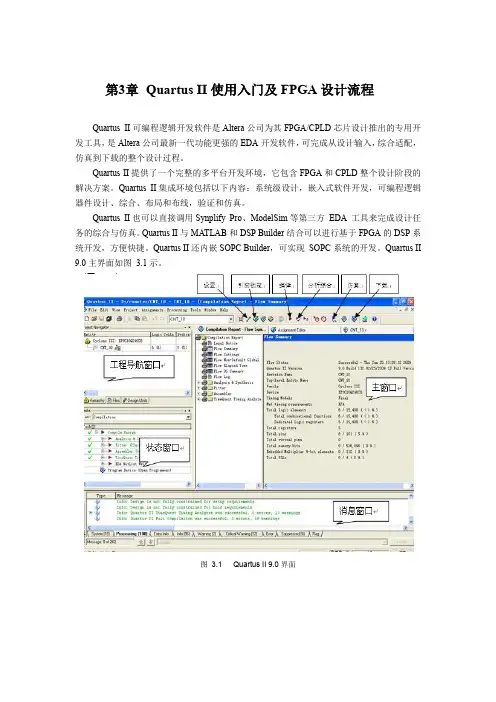

Quartus II 9.0主界面如图3.1示。

图 3.1 Quartus II 9.0界面3.1 Quartus II 基本设计流程Quartus II 设计的主要流程包括创建工程、设计输入、分析综合、编译、仿真验证、编程下载等,其一般流程如图 3.2所示。

下面以硬件描述语言输入法设计计数器为例,说明Quartus II 的设计流程。

3.1.1 创建工程使用Quartus II 设计电路被称作工程。

Quartus II 每次只进行一个工程,并将该工程的全部信息保存在同一个文件夹中。

开始一项新的电路设计,首先要创建一个文件夹,用以保存该工程的所有文件。

之后便可通过Quartus II 的文本编辑器编辑Verilog 源文件并存盘。

3.1.2 设计输入Quartus II 中包含原理图输入和硬件描述语言输入两种方法。

(1)原理图输入原理图输入的优点是,设计者不必具有诸如编译技术、硬件描述语言等新知识就能迅速入门,完成较大规模的电路系统的设计,且具有直观,易于理解的特点,适合于初学者使用。

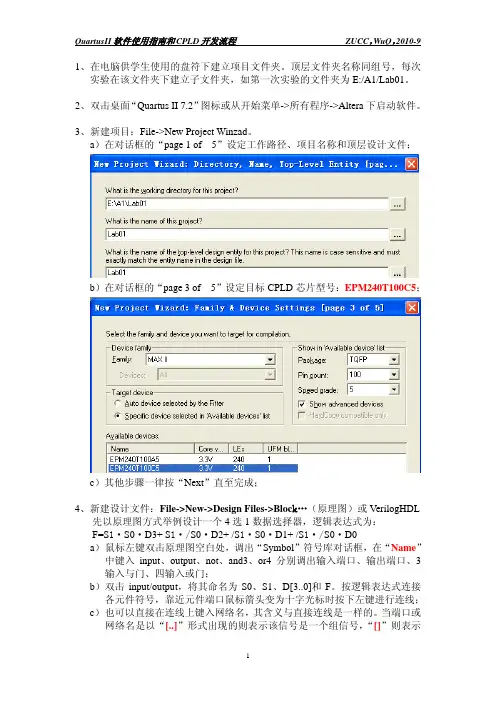

1、在电脑供学生使用的盘符下建立项目文件夹。

顶层文件夹名称同组号,每次实验在该文件夹下建立子文件夹,如第一次实验的文件夹为E:/A1/Lab01。

2、双击桌面“Quartus II 7.2”图标或从开始菜单->所有程序->Altera下启动软件。

3、新建项目:File->New Project Winzad。

a)在对话框的“page 1 of 5”设定工作路径、项目名称和顶层设计文件;b)在对话框的“page 3 of 5”设定目标CPLD芯片型号:EPM240T100C5;c)其他步骤一律按“Next”直至完成;4、新建设计文件:File->New->Design Files->Bloc k…(原理图)或VerilogHDL先以原理图方式举例设计一个4选1数据选择器,逻辑表达式为:F=S1·S0·D3+ S1·/S0·D2+ /S1·S0·D1+ /S1·/S0·D0 a)鼠标左键双击原理图空白处,调出“Symbol”符号库对话框,在“Name”中键入input、output、not、and3、or4分别调出输入端口、输出端口、3输入与门、四输入或门;b)双击input/output,将其命名为S0、S1、D[3..0]和F。

按逻辑表达式连接各元件符号,靠近元件端口鼠标箭头变为十字光标时按下左键进行连线;c)也可以直接在连线上键入网络名,其含义与直接连线是一样的。

当端口或网络名是以“[..]”形式出现的则表示该信号是一个组信号,“[]”则表示组信号中的单个成员,通常用于地址线、数据线或有一定变化规律的信号线。

下图展示了端口两种命名方式,信号线的两种连接方式;d)原理图绘制完成后,默认方式保存。

5、设计编译:Processing->Start Compilation或上方工具栏图标。

Altera FPGA开发说明(QuartusII 7.2 & ModelSim 6.5)By ccx于2010-11-22一、说明1、本例程中的代码是用Verilog编写的,但本文并不探讨Verilog本身。

推荐王金明的一本书作为入门书籍,既讲到了Verilog,也讲到了QuartusII 的使用,还探讨了Modelsim的使用(很难得地讲到了Test Bench的编写)。

2、QuartusII 7.2软件的文本编辑器不支持中文输入,Modelsim 6.5的编辑窗口也不尽如人意。

使用Notepad++(目前只支持Windows平台,方便易用)也可使用Gvim(陆博推荐,因为linux系统中也有对应的编辑工具)3、本例中的程序功能说明一个4位二进制计数器,显示到FPGA开发板(DE2-70)的4个LED上。

4、本例的验证平台为Altera公司的DE2-70开发板二、使用QuartusII 7.2和ModelSim 6.5进行Altera FPGA开发2.1、FPGA开发流程图2.2、建立QuartusII项目这里不讨论原理图输入法,也不讨论多个模块如何组织在1个顶层模块之下。

在建立项目之前,我已经编写好counter.v文件,并把它放在E:\counter目录下。

打开QuartusII软件,File→New Project Wizard…,可开始建立项目的流程。

2.2.1、向导介绍建立项目时要做的工作2.2.1、填写目录、项目名、top-level entity名注意:top-level entity需要正确填写,因为本例中只有一个模块counter,而且其为top-level entity,所以填写如下。

2.2.2、为项目添加文件2.2.3、选定器件Cyclone II系列,器件编号为EP2C70F896C6(可以网上搜索该器件号的意思)。

2.2.4、EDA工具设置默认即可,但可以留意Simulation一项,因为之后用ModelSim 6.5做时序仿真与它有关。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

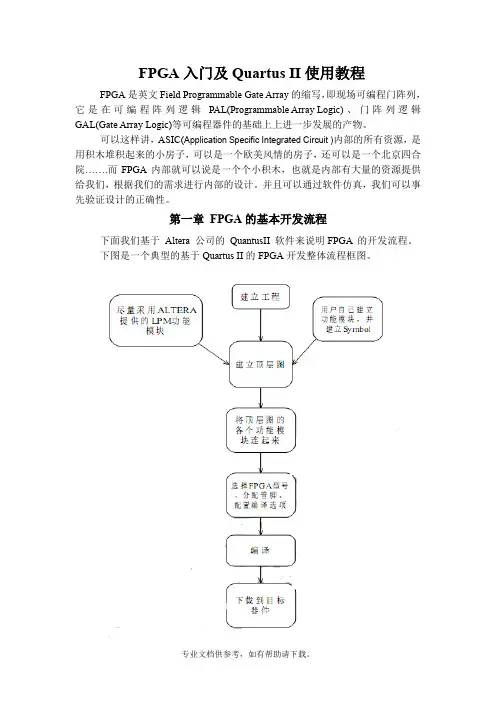

第一章FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(内部的所有资源,是Application Specific Integrated Circuit )用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

第一章 FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

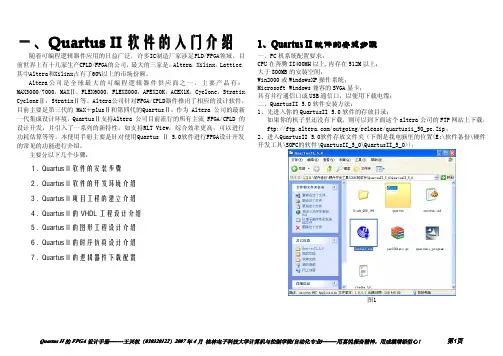

基于Quartus II 的CPLD开发实训手册(适用于电信系11级数电课程设计)编者:李楠2012-9Quartus II软件利用简介Quartus II是Altera公司提供的FPGA\CPLD开发集成环境,Altera是世界上最大可编程逻辑器件供给商之一。

Quartus II界面友好、利用便捷,被誉为业界最易用易学的EDA软件。

其主要功能为数字电子系统的设计输入、编辑、仿真、下载等。

该软件支持原理图输入设计和VHDL语言(和其它硬件描述语言)输入设计和原理图与HDL混合输入设计。

硬件描述语言(HDL-Hardware Description Language)是一种用于设计硬件电子系统的运算机语言,它用软件编程的方式来描述电子系统的逻辑功能、电路结构和连接形式,与传统的门级描述方式相较,它更适合大规模系统的设计。

VHDL(Very High Speed IC Hardware Description Language)以下将详细介绍原理图输入设计方式,但读者应该更多地关注设计流程,因为除最初的图形编辑输入外,其它处置流程都与文本(如VHDL文件)输入设计完全一致。

实验一原理图方式设计二进制全加器一、设计目的一、通过设计一个二进制全加器,掌握组合逻辑电路设计的方式。

二、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程和大体的设计方式、大体的仿真分析方式。

二、设计原理三、设计内容四、设计步骤1位全加器设计向导1 为本项设计成立文件夹任何一项设计都是一项工程(Project),都必需第一为此工程成立一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA软件默以为工作库(Work Library)。

一般不同的设计项目最好放在不同的文件夹中,注意,一个设计项目能够包括多个设计文件,如频率计。

打开Quartus Ⅱ,选菜单File→New,在弹出的New对话框当选择Device Design Files页的原理图文件编辑输入项Block Diagram/Schematic File,单击OK按钮后打开原理图编辑窗口如图所示。

明德扬点拨FPGA高手进阶第二章QuartusII技巧2.1FPGA开发流程第二章Quartus II技巧2.1 FPGA开发流程FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。

典型FPGA的开发流程一般如图4.1.1所示,包括功能定义/器件选型、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真以及芯片编程与调试等主要步骤。

1.功能定义/器件选型在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。

一般采用自顶向下的设计方法,把系统分成若干个基本模块,各模块功能相互独立并能协调工作。

好的系统结构,可以使系统高效稳定、减少资源、节省研发时间,是FPGA的最重要技巧。

但这要求设计师具有丰富的FPGA研发经验,能够从众多方案评估优劣,然后挑选适合的方案。

明德扬给出的FPGA学习步骤,先经过大量的基础案例训练,再逐步学习模块划分技术。

器件选型同样需要设计师具有丰富的FPGA研发经验,在项目启动时,就能够评估到整个项目所需要的资源、速度、功耗等。

但业界更通常的做法,先在开发板的基础上,完成所有功能的设计,得到该项目所需要的资源、速度、功耗等信息,从而再做器件造型,最后完成硬件的设计。

2.设计输入设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给EDA工具的过程。

常用的方法有硬件描述语言(HDL)和原理图输入方法等。

原理图输入方式是一种最直接的描述方式,在可编程芯片发展的早期应用比较广泛,它将所需的器件从元件库中调出来,画出原理图。

这种方法虽然直观并易于仿真,但效率很低,且不易维护,不利于模块构造和重用。

更主要的缺点是可移植性差,当芯片升级后,所有的原理图都需要作一定的改动。

明德扬不推荐这个方法,玩一玩可以,但做项目就太不方便了。