FPGA入门教程 ALTERA Quartus II 和 XILINX ISE CPLD入门教程 教案 VHDL Verilog 例程讲解

- 格式:ppt

- 大小:3.47 MB

- 文档页数:99

在自己做这个实验的时候,需要确认自己的开发软件是否已经安装好了,确认自己的下载器是否已经可以使用了。

如果还不熟悉的,可以看看下面两个文件QuartusII 9.0破解全过程.pdf下载器的安装.pdf实验要求:PC电脑一台,配置越高越好。

开发软件:QuartusII9.0SP2开发板型号:A-C8V4实验结果:学习Altera公司的FPGA开发软件QuartusII入门使用。

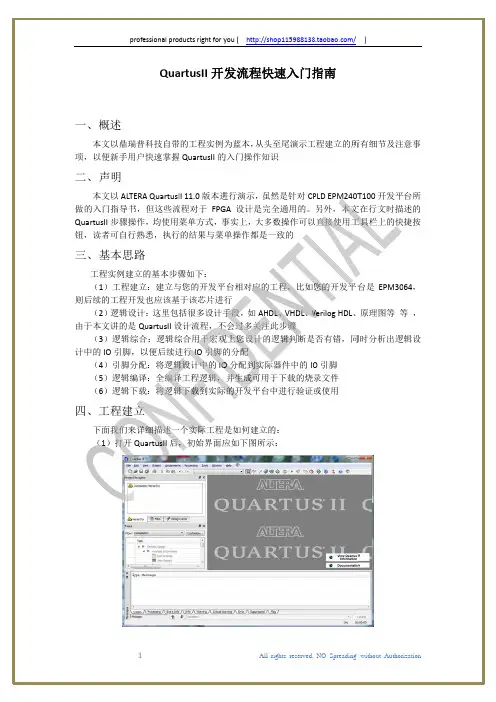

首先打开QuartusII9.0SP2的开发软件。

你有三种方法可以打开。

第一:如下图,桌面上有快捷图标。

双击就可以了。

第二:如下图,在开始菜单里面可以找到。

第三:如下图,在开始菜单里面也可以找到。

如下图:打开QII软件了如下图:我们可以把这个关闭了。

如下图:新建一个工程File->New Project Wizrd….如下图:点击Next如下图:这里我们要设置工程路径,工程名和顶层名。

点第一排三个点点那里如下图:我们把工程路径放在J盘下面FPGA_TEST文件夹;J:\FPGA_TEST设置好了,点击Next如下图:直接点击Next如下图:这里我们需要对CPU进行设置,也就是设置成和我们开发板对应的芯片。

Family 要选择Cyclone II如下图:如下图:选择芯片的封装,PQFP如下图:如下图:选择芯片的管教数目,我们这里是208个脚如下图:如下图:选择速度等级,我们这里选择8如下图:如下图:选择我们最后设置好的芯片。

然后点击Next如下图:然后点击Next如下图:然后点击Finish如下图:如下图:然后点击Next如下图:点击File->New 新建一个我们用来编写程序的窗口。

如下图:如果你使用Verilog语言,就选择Verilog HDL File 然后点击OK如下图:如果你使用VHDL语言,就选择VHDL File 然后点击OK 我们这里用VHDL作为演示如下图:会在右边出现程序编写的空白窗口。

如下图:假设我们已经编写了程序A-C8V4-开发板资料A\A-C8V4开发板资料\A-C8V4开发板-整理的VHDL程序\ 15实验十五:LED流水灯A (用这个里面的程序)如下图:我们的程序编写了,要保存File -> Save如下图:如下图:保存了之后,就要编译,如下图:我们编译的时候出错了。

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)Quartus Ⅱ8.1入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

快捷工具●快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

注意以下命名要一致。

第二步:新建工程(file>new Project Wizard)所建工程的1 工程名称:2第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b; assign out2=a | b; endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis ))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location 为您的输入输出配置引脚。

第七步:整体编译(工具栏的按钮(startComplilation))各个端口顶层某块的第八步:功能仿真(直接利用quratus 进行功能仿真)1 将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function )2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist )设置输入接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):观察波形,刚好符合我们的逻辑。

FPGA的基本工作原理Xilinx和Altera对比FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。

它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。

查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA 采用Flash或者熔丝与反熔丝工艺的查找表结构。

通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。

根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,最多只可能存在2n种结果。

所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。

FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。

查找表的原理与结构查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的的RAM。

当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

下面给出一个四输入与非门电路的例子来说明LUT实现逻辑功能的原理。

表给出一个使用LUT实现四输入与门电路的真值表。

从中可以看到,LUT具有和逻辑电路相同的功能。

实际上,LUT具有更快的执行速度和更大的规模。

3.1.2查找表结构的FPGA逻辑实现原理我们还是以这个电路的为例:A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连到到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样组合逻辑就实现了。

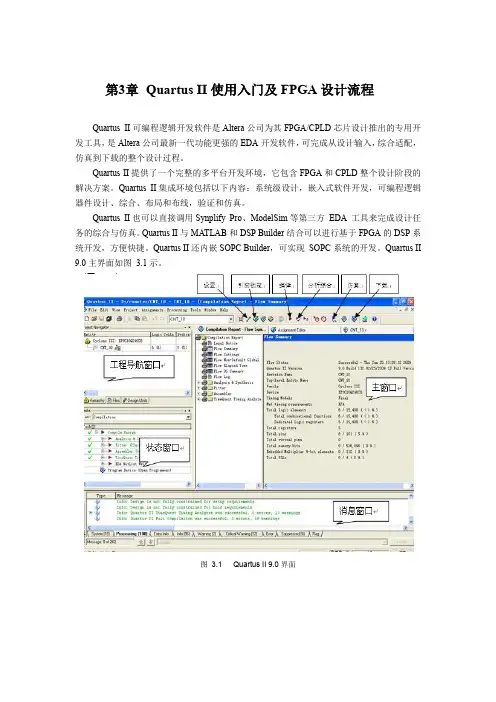

第3章Quartus II使用入门及FPGA设计流程Quartus II可编程逻辑开发软件是Altera公司为其FPGA/CPLD芯片设计推出的专用开发工具,是Altera公司最新一代功能更强的EDA开发软件,可完成从设计输入,综合适配,仿真到下载的整个设计过程。

Quartus II提供了一个完整的多平台开发环境,它包含FPGA和CPLD整个设计阶段的解决方案。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件设计、综合、布局和布线,验证和仿真。

Quartus II也可以直接调用Synplify Pro、ModelSim等第三方EDA 工具来完成设计任务的综合与仿真。

Quartus II与MATLAB和DSP Builder结合可以进行基于FPGA的DSP系统开发,方便快捷。

Quartus II还内嵌SOPC Builder,可实现SOPC系统的开发。

Quartus II 9.0主界面如图3.1示。

图 3.1 Quartus II 9.0界面3.1 Quartus II 基本设计流程Quartus II 设计的主要流程包括创建工程、设计输入、分析综合、编译、仿真验证、编程下载等,其一般流程如图 3.2所示。

下面以硬件描述语言输入法设计计数器为例,说明Quartus II 的设计流程。

3.1.1 创建工程使用Quartus II 设计电路被称作工程。

Quartus II 每次只进行一个工程,并将该工程的全部信息保存在同一个文件夹中。

开始一项新的电路设计,首先要创建一个文件夹,用以保存该工程的所有文件。

之后便可通过Quartus II 的文本编辑器编辑Verilog 源文件并存盘。

3.1.2 设计输入Quartus II 中包含原理图输入和硬件描述语言输入两种方法。

(1)原理图输入原理图输入的优点是,设计者不必具有诸如编译技术、硬件描述语言等新知识就能迅速入门,完成较大规模的电路系统的设计,且具有直观,易于理解的特点,适合于初学者使用。

【转】Xilinx和Altera的FPGA的对⽐Xilinx和Altera的FPGA的对⽐[原创⽂章,转载请注明出处tengjingshu]⽼板布置了⼀个任务:搞⼀个符合要求的DDS(直接数字频率合成),其中要求DDS存储波形的ROM地址要48位,天啊,这可是2的48次这么多个byte,FPGA有这么多空间吗?于是我就⽐较了⼀下Xilinx和Altera的FPGA逻辑资源。

(其实DDS中存储波形数据的ROM地址为没必要搞到48位,正弦波形间隔两位的数据差不了多少可以省了很多步长,加上其实只要存储1/4正弦波波形的数据既可,所以地址位可以减少到12位)。

要⽐较Xilinx和Altera的FPGA,就要清楚两个⼤⼚FPGA的结构,由于各⾃利益,两家的FPGA结构各不相同,参数也各不相同,但可以统⼀到LUT(Look-Up-Table)查找表上。

关于两家FPGA的结构,可以参考:1.2.我师姐⽤的是Altera的Cyclone II系列的EP2C35,我⽤的是Xilinx的Spartan-3E系列的XC3S500E。

可以参考Datasheet。

Cyclone IISpartan-3E其中Altera的LEs和Xilnx的CLB(Slice)【其中1 Slices="1" CLB】对应于LUT的结构。

Altera从LEs的结构可以知道 1 LEs = 1 LUTXilinx下图是1 Slice的结构,从Slice的结构可以看到1 Slice = 2 LUT =4 CLB从⽽可以知道Xilinx和Altera FPGA逻辑资源的对应关系:(为了统⼀度量衡(感觉像QSH⼀样),业界⼀般会归结到BLM(Basic Logic Module)1 BLM=1 LUT4(四输⼊查找表)+DFF(D触发器)1 BLM=0.5 Slice(Xilinx)=1 LE(Altera)=2.25 Tile(Actel)于是就可以知道Altera的Cyclone II系列的EP2C35有33216个LUT,我⽤的是Xilinx的Spartan-3E系列的XC3S500E有9312个LUTL 呜呜……加上EP2C35还有4个PLL,我的XC3S500E就跟⽐不上了参考资料:1. Altera Cyclone II系列⼿册 2. Xilinx Spartan-3E系列⼿册 3. 【器件求助】XILINX FPGA 和 ALTERA FPGA在逻辑单元是怎么算的? 4. PLD/FPGA 结构与原理初步5. xilinx和Altera的fpga對⽐?6. 做个⼩调查,Xilinx的Spartan-3和Altera的MAX II,哪个⽤的更多? 7. Altera/Xilinx FPGA逻辑门计算 8. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼀)9. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼆)。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

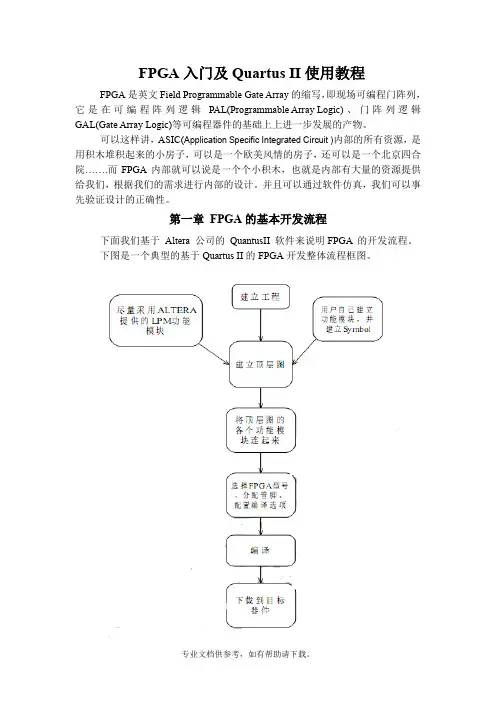

第一章FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(内部的所有资源,是Application Specific Integrated Circuit )用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

第一章 FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。

可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。

并且可以通过软件仿真,我们可以事先验证设计的正确性。

第一章FPGA的基本开发流程下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。

下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管理。

2、建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里边,编译的时候就将这些模块整合在一起。

也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。

3、采用ALTERA公司提供的LPM功能模块。

Quartus软件环境包含了大量的常用功能模块,比如计数器、累加器、比较器等等。

4、自己建立模块。

由于有些设计中现有的模块功能不能满足具体设计的要求,那就只能自己设计。

使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。

这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。

5、将顶层图的各个功能模块连线起来。

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE 被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。