ISA总线介绍

- 格式:doc

- 大小:673.50 KB

- 文档页数:8

PCI总线和ISA总线有什么区别?PCI,现在几乎看不到ISA了。

PCI总线是高速同步总线,具有32bit总线宽度,工作频率是33MHz,最大传输率为132Mbyte/s,远远大于ISA总线5Mbyte/s 的速率。

主板有两种扩展槽,黑色的为ISA,白色的短槽为PCI,PCI是现在比较先进的一种。

分别插入ISA卡和pci卡。

1、ISA总线ISA总线接口由于I/O速度较慢,随着上世纪90年代初PCI总线技术的出现,很快被淘汰了。

目前在市面上基本上看不到有ISA总线类型的网卡。

不过近期出现一种复古现象,就是在一些品牌的最新的i865系列芯片组主板中居然又提供了几条ISA插槽,真是令人费解!最普通的总线是ISA总线,即工业标准结构总线。

16位ISA总线频率为8MHz左右。

它的应用范围很广,几乎所有的主板都保留了ISA总线的扩展槽。

2、PCI总线PCI是Intel公司开发的一套局部总线系统,它支持32位或64位的总线宽度,频率通常是33MHz。

目前最快的PCI2.0总线速度是66MHz。

PCI总线允许十个接插件,同时它还支持即插即用。

是目前最主流的一种接口类型。

因为它的I/O速度远比ISA总线型的卡快(ISA最高仅为33MB/s,而目前的PCI 2.2标准32位的PCI接口数据传输速度最高可达133MB/s),所以在这种总线技术出现后很快就替代了原来老式的ISA总线。

PCI是Intel公司开发的一套局部总线系统,它支持32位或64位的总线宽度,频率通常是33MHz。

目前最快的PCI2.0总线速度是86MHz。

目前主流的PCI规范有PCI2.0、PCI2.1和PCI2.2三种,PC机上用的32位PCI网卡,三种接口规范的卡外观基本上差不多(主板上的PCI插槽也一样)。

服务器上用的64位PCI网卡外观就与32位的有较大差别,主要体现在金手指的长度较长。

ISA总线时序到本章为止,大家已经学会怎么读时序图。

ISA总线源于PC总线,其信号定义和8086CPU的信号十分接近。

我们着重分析ISA总线信号的一些特点。

ISA的16位数据传送是通过采样M16#或IO16#来确认的,在BCLK2的开始(上升沿),ISA总线控制器检测16位存储器传送信号M16#,如果该信号为0,意味着本次总线访问是16位存储器访问,将在3个BCLK之内完成。

如果M16#为1,表示本次总线访问是8位存储器访问,需要6个BCLK周期。

在16位ISA中,LA17~23是非锁存信号。

仅仅在第1个时钟周期有效,同样,要使扩展地址信号在整个ISA访问周期中保持,ISA扩展卡必须利用BALE信号锁存LA17~23上的地址。

注意,LA17~23上的地址信号有效时间是先于A0~15的。

LA17~23有效之后,与数据线分离的地址线A[15:0]上才发出地址信号,同时,数据线高位字节使能信号变为有效状态。

即SBHE#变成低电平,这样就可以通过SD8~15传送高8位数据,实现16位操作。

如果NOWS#为高,表示本周期仍为标准16位存储器访问周期,系统主板自动插入一个等待周期,即3个周期完成存储器访问。

如果采样到NOWS#为低,意味着所访问的存储器为高速存储器,主板可以撤除将要插入的等待周期,这样便形成了在2个总线时钟周期内完成的对存储器的快速访问。

ISA除了要在BCLK2的下降沿采样零等待周期信号以外,还将在BCLK3的上升沿(BCLK3的开始)采样I/O通道准备好信号IOCHRDY。

IOCHRDY信号是为慢速的存储器或I/O芯片准备的。

如果被访问的存储器不能在3个时钟周期内完成和主设备的数据交互,那么可以在扩展卡上设计产生请求插入等待周期的信号,即在总线采样IOCHRDY(BCLK3前沿)之前,令IOCHRDY为0,并根据需要插入等待周期的数目,决定IOCHRDY为低电平的持续时间。

需要注意的是,ISA总线规范规定,如产生NOWS#信号就不允许出现IOCHRDY 无效的情况,否则就会出现不可预知的情况。

AS-I总线教程1. 介绍1.1 现场总线系统概述在当今⼯业⾃动化中,⼀个复杂的系统包含⼤量的输⼊/输出信号,只通过⼀个中央控制器很难实现⾼要求的控制⽔平。

⼯业实践证明,将庞⼤的控制任务分割成多个⼩的,易于实现的⼦任务,即分布式控制,更加具有实际意义。

这就是需要通过总线系统将主控制器或PC 与各个⼦系统连接起来。

输⼊和输出设备也不可能再与PLC的中央信号模块直接连接。

他们通过⼀个I/O端⼦连接到相应地⼦系统中。

各⼦系统间同样通过总线互相联系,形成⼀个完整的控制系统。

这种解决⽅案具有下列特点:·信息(数据)通过总线传送·信息可以通过逻辑连接⽽传送到所有的⽹络设备中·将所有的传感器和执⾏器连接⾄主控制器中·各等级的控制器相互连接·对⽹络中各设备进⾏循环诊断⽹络的优点有:·灵活的系统结构,车间内可以很容易的在总线上增减设备·与传统接线相⽐,调试更加⽅便·数据集中处理·由于接线减少,故障率降低·故障处理更加优化,可靠性提⾼·维护成本低1.2 ⽹络等级为了更好的理解企业中的信号流,我们可以将⽹络分为⼏个等级。

信号不仅在每个层中传输,在各层之间也相互联系,也就是说,在横向和纵向两个⽅向上延伸。

每个等级的⽹络都与上下相邻的⽹络连接,可以判定相互间通讯的需求。

在最上层⽹络,存在众多复杂的计算机系统,能够不定期的对各种复杂数据进⾏响应,⼤量的通讯参与者和响应者在⽹络中相互协调。

在最底层,依然有很⼤的信息吞吐量,只是数据相对要少于上层结构。

在⾃动化系统⽹络中可以分为以下5层结构:·计划编制层(Planning Level),对来⾃⽣产层的信息进⾏评价,组织编排并协助⽣产部门进⾏决策。

在这⼀层中,不论是信息量还是传输速率和距离都是最⼤的。

·控制层(Control Level),对每个⽣产层进⾏协调。

解释isa总线,eisa总线及pci总线的工作特点

ISA、EISA和PCI总线的工作特点如下:

1.ISA总线:

•数据传输速率较慢,最大传输速率仅为8MB/s。

•允许多个CPU共享系统资源,但CPU资源占用较高,且数据传输带宽较小。

•基于ISA总线的扩展插槽颜色一般为黑色,长度比PCI接口插槽要长。

•已逐渐被淘汰,被PCI总线所取代。

2EISA总线:

•具有较大的带宽,约为32位数据总线,最高可达33MHz。

•传输速度较快,最高可达20MB/s。

•提供16个插槽,更好地支持外围设备的安装和升级。

•支持多种新技术和功能特性,如内存映射、DMA控制器、中断控制器等。

3PCI总线:

•具有地址数据多路复用的高性能的32位或64位同步总线。

•总线引脚数目和部件数量较少,降低了成本及布线的复杂度。

•支持线性突发传输模式,确保了总线不断满载数据进行高速传输。

•设计独立于处理器的,具有严格的总线规范和良好的兼容性。

•隐蔽的总线仲裁减小了仲裁开销,极小的存取延迟,采用总线主控和异步数据转移操作。

•提供数据和地址奇偶校验功能,保证了数据的完整性和准确性。

•与CPU的时钟频率无关,能支持多个外设,设备间通过局部总线可以完成数据的快速传递,有效解决了数据传输的瓶颈问题。

•对扩展卡和元件能够进行自动配置,实现设备的即插即用。

总的来说,PCI总线在数据传输速率、设计灵活性、兼容性和扩展性等方面具有优势,因此在现代计算机系统中得到广泛应用。

ISA(PC/104) 总线信号时序简介SBS Science & Technology Co., Ltd.APPN-002ISA(PC/104)总线信号时序简介目录1.0 ISA概况 2.0 ISA文献2.1 ISA规范 2.2 ISA书籍3.0 ISA结构形式 4.0 PC/104结构形式 5.0 ISA信号描述 6.0 ISA时序图 7.0 ISA信号用法 8.0 ISA连接器引脚 9.0 PC/104总线连接引脚盛博科技1APPN-002ISA(PC/104)总线信号时序简介1.0 ISA 概况ISA总线 即工业标准结构 Industry Standard Architecture 十世纪八十年代早期IBM在佛罗里达州Boca Raton研发实验室 出的个人电脑 其中包括了8位ISA总线 1984年 最早起源于二 IBM于1981年推IBM推出了PC-AT 这是第一个全面实现16位结构的ISA总线 IBM最初命名的 AT总线 首先被记录于IBM出版的 The PC-AT TechnicalReference 上 此书包括了图表和BIOS清单 这样类似于康柏的其它公司很容易 就生产出了IBM兼容的产品 由于IBM将 AT总线”作为一项商标进行保护 其它生产兼容IBM产品的公司就不能使用 AT总线 这个名称 结果 人们在行业 中创造了 ISA 并将其作为这种总线的新名称 这个名称最后被包括IBM在内的所有公司采用 尽管 The PC-AT Technical Reference 包含了详细的图表和BIOS清单 但其 因未包含严格的时序 规范及其它必要条件而未成为一个很好的总线规范 结果 对ISA各种各样的实现造成了一些产品之间的兼容性问题 的问题 迄今为止 渐渐形成了许多ISA总线规范 但是不幸的是 为了减轻因兼容造成 这些规范也不尽相同没有产生出一个完全统一的ISA总线规范2.0 ISA 文献2.1 ISA 规范有关ISA总线规范的文档有如下几篇 EISA Specification, Version 3.12――这篇文档包括ISA总线规范 并规定了 扩展工业标准结构 定义了ISA总线上32位扩展 IEEE Draft Standard P996 这篇文档描写了标准PC类系统的机械和电 子规范 通过/.付费可以向IEEE订购 PS/2 Technical Reference 这篇来自IBM的文档内容包括在一些IBM计 算机PS/2线上使用ISA总线的信号定义和时序图2.2 ISA书籍两本对ISA总线进行了详细描述的书是 ISA & EISA Theory and Operation, by Edward Solari. (Annabooks) (ISBN 0-929392-15-9) ISA System Architecture, by Don Anderson and Tom Shanley. (MindShare) (ISBN 0-201-40996-8)盛博科技2APPN-002ISA(PC/104)总线信号时序简介3.0 ISA结构形式8 位卡:(At the card)(At the computer)16 位卡:(At the card)(At the computer)盛博科技3APPN-002ISA(PC/104)总线信号时序简介4.0 PC/104结构形式与ISA板不同 义相同PC/104 8位/16位总线模块具有同样尺寸 全为地 Gnd与ISA板总线信号定但多A32/B32;C0/D0;C19/D19引脚盛博科技4APPN-002ISA(PC/104)总线信号时序简介5.0 ISA 信号描述SA19-SA0System Address 地址位19:0用于对系统中内存和I/O设备的寻址 内存寻址时 使用SA19:SA0配合LA23:LA17 能寻址多达16兆的内存 低16位,可以用来定位64K的I/O地址 号在BALE为高时有效 持有效 SA19是最高位 I/O寻址中 只使用 地址信SA0为最低位而由BALE的下降沿锁定通过读或写命令使信号保 但也可以由ISA这些信号通常由系统微处理器或DMA控制器驱动扩展板的Bus Master 来取得ISA总线的控制权LA23-LA17Unlatched Address 23:17位是系统中内存地址 址多达16兆的内存 它们和SA19:SA0可以共同寻 由于它们是非锁存的 当BALE为高时这些信号才有效故在整个总线周期中它们并不总是保持有效状态 用BALE下降沿锁存这些信 号的译码AENAddress Enable 用于DMA传送过程中关闭总线系统微处理器和其它设备的 传送通道 制 当AEN有效时 总线上的地址 数据和读写信号由DMA控制器控 以防止DMA周期中出现不正确ISA扩展板的片选译码应包含AEN信号的片选BALEBuffered Address Latch Enable 用来锁存LA23:LA17信号或者译码这些信号 BALE下降沿用于锁存LA23:LA17 在DMA周期中BALE被强制为高 此信号 与AEN并用时表明一个有效的微处理器或DMA地址CLKSystem Clock 是一个自行运转的时钟 它的频率一般在7MHz到10MHz之间 系统时钟在一些ISA板的应用中保证与 该频率值在ISA标准中并未严格定义 系统微处理器的同步工作盛博科技5APPN-002ISA(PC/104)总线信号时序简介SD15 - SD0System Data SD15:SD0是ISA总线上的数据总线 最低位 8位设备的数据传送通过SD7:SD0来完成 其中SD15是最高位 SD0是 SD15:SD0则用于传送16位设备的数据 当16位设备向8位设备传送数据时 需将16位信号转换成两个8位 周期通过SD7:SD0来进行传送-DACK0 to -DACK3 and -DACK5 to -DACK7DMA Acknowledge 0:3和5:7分别被用来确认DRQ0:DRQ3和DRQ5:DRQ7的 DMA请求DRQ0 to DRQ3 and DRQ5 to DRQ7DMA Requests 用于ISA板向DMA控制器提出服务请求 或者Bus Master设备 申请总线控制权的请求 多个DMA请求可能同时断定有效 发出请求的设备必须保持请求信号有效直到系统板发出相应的DACK信号-I/O CH CKI/O Channel Check I/O CH CK由ISA板生成进而引发非屏蔽中断 时表明发现了不可恢复的错误 当它有效I/O CH RDYI/O Channel Ready 允许较慢速ISA板通过插入等待状态 延长I/O或内存读写 周期 好 I/O CH RDY通常处于高 以插入等待状态 就绪 ISA板将I/O CH RDY拉低 未准备使用I/O CH RDY插入等待状态的设备需可以完成读写周期时 地址译码和读/写信号有效后立即使I/O CH RDY信号为低 当设备释 放 I/O CH RDY回高-IORI/O Read 线上 由总线控制设备驱动 并且指令所选的I/O设备将数据读到数据总-IOWI/O Write 由总线控制设备驱动 指令所选的I/O设备从数据总线上获取数据盛博科技6APPN-002ISA(PC/104)总线信号时序简介IRQ3 to IRQ7 and IRQ9 to IRQ12 and IRQ14 to IRQ15Interrupt Requests 向系统微处理器发出信号 提示来自ISA板的请求 当IRQ 线由低向高跳变时产生中断请求 请求必须一直保持为高直到CPU通过其中断 服务程序确认了这个请求 请求有不同的优先权 来自IRQ9:IRQ12 而来自IRQ3:IRQ 7IRQ14 :IRQ15的请求优先被处理 的请求较后处理 IRQ7优先级最低IRQ9优先级最高-SMEMRSystem Memory Read 指令一个所选定的Memory设备将数据送到数据总线 该信号仅在对1M以内的Memory空间读时才有效 SMEMR来源于MEMR及低 于1兆的存储译码-SMEMWSystem Memory Write 指令将当前数据总线上的数据写入一个所选定的 Memory设备 该信号仅在对1M以内的Memory空间写时才有效 SMEMR来源 于MEMR及低于1兆的存储译码-MEMRMemory Read 指令将一个所选定的Memory设备数据读出送到数据总线 它在 整个Memory存储读周期中都有效-MEMWMemory Write 指令将当前数据总线上的数据存储到一个所选定的Memory设 备中 它在整个Memory存储写周期中都有效-REFRESHMemory Refresh 该信号为低时表明正在进行内存刷新操作OSCOscillator 是一个时间段为70毫微秒的时钟(14.31818 MHz) 该信号与系统时 钟不同步盛博科技7APPN-002ISA(PC/104)总线信号时序简介RESET DRVReset Drive在电源开启或系统复位时来复位或初始化系统逻辑 高电平有效TCTerminal Count 在DMA通道操作中当计数完成时产生的终端计数信号-MASTERMaster 和DRQ线一起获得ISA板上ISA总线的控制权 后 权 设备将MASTER信号拉低 在此状态下 使得其获得系统地址 当接收到一个DACK 数据和控制线的控制 在读/设备将在驱动地址和数据线之前等待一个时钟周期写命令之前等待两个时钟周期-MEM CS16Memory Chip Select 16 ISA板将该信号拉低以指示这是一个16位的Memory读 写操作 它由LA23:LA17地址线译码来驱动-I/O CS16I/O Chip Select 16 I/O设备将该信号拉低以指示这是一个16位的Memory读写操 作 它由SA15:SA0地址线译码来驱动-0WSZero Wait State 由一个总线从设备驱动使其拉低 状态即可完成一个总线周期 由地址译码产生 说明不插入任何额外等待 -OWS 完成一个无需等待的16位Memory周期-SBHESystem Byte High Enable 该信号为低时表明数据在数据总线高位部分传送(D15 至 D8)盛博科技8APPN-002ISA(PC/104)总线信号时序简介6.0 ISA总线时序图8位 I/O 总线周期BALE SA(15:0) -SBHE -IOR/W SD(7:0) (READ) SD(7:0) (WRITE) I/OCHRDY ________ __| |_________________________________________ _ ______________________________________________ __ _><______________________________________________><__ ______________ _______ |______________________________| _____________ -------------------------------------<_____________>__________________________________ ----------------<__________________________________>__________________ _ _ _ _ _ _ _ _ _ _ _ _ _________ |________________________|8 位 Memory 总线循环_____ ________| |______________________________________ _ ________________ ________________________________ LA(23:17) _><________________><________________________________ _______ ________________________________________ __ SA(19:0) _______><________________________________________><__ ______________ _______ -MEMR/W |______________________________| _____________ SD(7:0) -------------------------------------<_____________>(READ) __________________________________ SD(7:0) ----------------<__________________________________>(WRITE) __________________ _ _ _ _ _ _ _ _ _ _ _ _ _________ I/OCHRDY |________________________| BALE盛博科技916位I/O总线周期________BALE ______________| |_____________________________ _____________ __________________________________ __ SA(15:0) _____________><__________________________________><__ _________________ ___ -IOCS16 |_______________________________|_____________________ ______ -IOR/W |________________________|__________________SD(15:0) -----------------------------<__________________>---- (READ)________________________SD(15:0) -----------------------<________________________>---- (WRITE)_______________________ _ _ _ _ _ _ _ _ _ _ ______I/OCHRDY |___________________|16位Memory总线周期1个或多个等待状态______BALE _________________| |____________________________ ___ ________________________ ______________________ LA(23:17) ___><________________________><______________________ ________________ ________________________________ _ SA(19:0) ________________><________________________________><_ _______ ______________________ -MEMCS16 |______________________|________________________ ______ -MEMR/W |_____________________|_______________SD(15:0) --------------------------------<_______________>---- (READ)_____________________SD(15:0) --------------------------<_____________________>---- (WRITE)__________________________ _ _ _ _ _ _ _ _ __________ I/OCHRDY |_______________|6位Memory总线周期0等待状态______BALE _________________| |____________________________ ___ ________________________ ______________________ LA(23:17) ___><________________________><______________________ ________________ _________________________ ________ SA(19:0) ________________><_________________________><________ _______ ______________________ -MEMCS16 |______________________|_________________________ ______________________ -0WS |____|________________________ ________________ -MEMR/W |___________|______SD(15:0) --------------------------------<______>------------- (READ)____________SD(15:0) --------------------------<____________>------------- (WRITE)DMA读______________DRQ(n) __| |___________________________________ _______________ __________ -DACK(n) |__________________________|____________________________________AEN,BALE ________| |_______ _______________ ___________________________ _______ SA(15:0) _______________><___________________________><_______ -SBHE________________ ________________________ _________ SA(19:16) ________________><________________________><_________ LA(23:17)____________________ __________ -MEMR |_____________________|____________SD(15:0) -------------------------------<____________>-------- ______________________ ___________ -IOW |__________________|__________TC _______________________________| |__________ ________________________ _____________________ I/OCHRDY |______|DMA写______________DRQ(n) __| |___________________________________ _______________ __________ -DACK(n) |__________________________|____________________________________AEN,BALE ________| |_______ _______________ ___________________________ _______ SA(15:0) _______________><___________________________><_______ -SBHE________________ ________________________ _________ SA(19:16) ________________><________________________><_________ LA(23:17)____________________ __________ -IOR |_____________________|____________SD(15:0) -------------------------------<____________>-------- ______________________ ___________ -MEMW |__________________|__________TC _______________________________| |__________ ________________________ _____________________ I/OCHRDY |______|Bus Master周期___________________________________DRQ(n) __| |______________ _______________ __________ -DACK(n) |__________________________|__________________ _______ -MASTER |__________________________|__________________ _______ AEN ________| |__________________________| |_ _____________________________________________________ BALE ________| |_ ________________________ ___________ ______________ SA(19:0) ________________________><___________><_______________ -SBHE________________________ ___________ ______________ LA(23:17) ________________________><___________><___________________________________________ _________________ -IOR,-IOW |_____|-MEMR,-MEMW_____SD(15:0) -------------------------------<_____>---------------内存刷新周期_______________ _______________ -REFRESH |_____________________|_________________ ____________ ____________________ SA(9:0) _________________><____________><____________________ ______________________ ________________ -SMEMR |_____________|_________________________ _ _ _ _ ___________________ I/OCHRDY |_______|7.0 ISA信号用法图例I/O = 输入/输出I = 输入O = 输出- = 不需要的信号I/O出现在括号里表明这个信号是可选信号下表是ISA系统板上典型的信号使用情况Signal Name System Board Usage Signal Name System BoardUsageAEN O-MEM CS16 I/O BALE O-MEMR I/O CLK O-MEMW I/O -DACK O OSC O DRQ I-REFRESH I/O -IO CS16 I RESET DRV O -I/O CH CK I SA I/O I/O CH RDY I/O SD I/O -IOR I/O-SBHE I/O -IOW I/O-SMEMR I/O IRQ I-SMEMW I/O LA I/O TC I/O -MASTER I-0WS I下表是ISA扩展板上典型的信号使用的情况Signal Name ISA BusMasterISA 16-bitMem SlaveISA 16-bitI/O SlaveISA 8-bitMem SlaveISA 8-bitI/O SlaveISA DMADeviceAEN --I-I-BALE -I-(I)--CLK (I)(I)(I)(I)(I)(I) -DACK I----I DRQ O----O -IO CS16 I-O----I/O CH CK(O)(O)(O)(O)(O)(O) I/O CH DY I(O)(O)(O)(O)--IOR O-I-I I -IOW O-I-I I IRQ (O)(O)(O)(O)(O)(O) LA(23:17) O I-(I)---MASTER O------MEM CS16 I0-----MEMR O I-(I)---MEMW O I-(I)--OSC (I)(I)(I)(I)(I)(I) -REFRESH (O)I-I--RESET DRV I I I I I I SA(16:0) O I I I I-SA(19:17) -(I)-(I)--SD(7:0) I/O I/O I/O I/O I/O I/O SD(15:8) I/O I/O I/O--(I/O) -SBHE O I I----SMEMR ---I---SMEMW ---I--TC -----(I) -0WS -(O)-(O)(O)-8.0 ISA 连接引脚Signal Name Pin Pin Signal Name Ground B1A1-I/O CH CK RESET DRV B2A2SD7+5 V dc B3A3SD6IRQ 9B4A4SD5-5 V dc B5A5SD4DRQ2B6A6SD3-12 V dc B7A7SD2-0WS B8A8SD1+12 V dc B9A9SD0Ground B10A10I/O CH RDY -SMEMW B11A11AEN-SMEMR B12A12SA19-IOW B13A13SA18-IOR B14A14SA17-DACK3B15A15SA16DRQ3B16A16SA15-DACK1B17A17SA14DRQ1B18A18SA13-REFRESH B19A19SA12 CLK B20A20SA11IRQ7B21A21SA10IRQ6B22A22SA9IRQ5B23A23SA8IRQ4B24A24SA7IRQ3B25A25SA6-DACK2B26A26SA5TC B27A27SA4BALE B28A28SA3+5 V dc B29A29SA2OSC B30A30SA1Ground B31A31SA0Key Signal Name Pin Pin Signal Name -MEM CS16D1C1-SBHE-IO CS16D2C2LA23IRQ10D3C3LA22IRQ11D4C4LA21IRQ12D5C5LA20IRQ15D6C6LA19IRQ14D7C7LA18-DACK0D8C8LA17DRQ0D9C9-MEMR -DACK5D10C10-MEMWDRQ5D11C11SD08-DACK6D12C12SD09DRQ6D13C13SD10-DACK7D14C14SD11DRQ7D15C15SD12+5 V dc D16C16SD13-MASTER D17C17SD14Ground D18C18SD159.0 PC/104总线引脚引脚信号名用途In/OutA1 -IOCHCK Bus NMI input INA2 SD7 Data Bit 7 I/OA3 SD6 Data Bit 6 I/OA4 SD5 Data Bit 5 I/OA5 SD4 Data Bit 4 I/OA6 SD3 Data Bit 3 I/OA7 SD2 Data Bit 2 I/OA8 SD1 Data Bit 1 I/OA9 SD0 Data Bit 0 I/OA10 IOCHRDY Processor Ready Ctrl INEnable I/O A11 AEN AddressA12 SA19 Address Bit 19 I/OA13 SA18 Address Bit 18 I/OA14 SA17 Address Bit 17 I/OA15 SA16 Address Bit 16 I/OA16 SA15 Address Bit 15 I/OA17 SA14 Address Bit 14 I/OA18 SA13 Address Bit 13 I/OA19 SA12 Address Bit 12 I/OA20 SA11 Address Bit 11 I/OA21 SA10 Address Bit 10 I/OA22 SA9 Address Bit 9 I/OA23 SA8 Address Bit 8 I/OA24 SA7 Address Bit 7 I/OA25 SA6 Address Bit 6 I/OA26 SA5 Address Bit 5 I/OA27 SA4 Address Bit 4 I/OA28 SA3 Address Bit 3 I/OA29 SA2 Address Bit 2 I/OA30 SA1 Address Bit 1 I/OA31 SA0 Address Bit 0 I/OA32 GND Ground N/APC/104总线接口P1A引脚信号名用途In/OutB1 GND Ground N/AReset OUT B2 RESET SystemPower N/A B3 +5V +5vB4 IRQ9 Int Request 9 INPower N/A B5 -5V -5vB6 DRQ2 DMA Request 2 INPower N/A B7 -12V -12vB8 ENDXFR Zero wait state INPower N/A B9 +12V +12vPin N/A B10 N/A KeyB11 -SMEMW Mem Wrt, Io 1M I/OB12 -SMEMR Mem Rd, Io 1M I/OWrite I/O B13 -IOW I/Oread I/O B14 -IOR I/OB15 -DACK3 DMA Ack 3 OUTB16 DRQ3 DMA request 3 INB17 -DACK1 DMA Ack 1 OUTB18 DRQ1 DMA request 1 INB19 -REFRESH MemoryRefresh I/OClock OUTB20 SYSCLK SysB21 IRQ7 Int Request 7 INB22 IRQ6 Int Request 6 INB23 IRQ5 Int Request 5 INB24 IRQ4 Int Request 4 INB25 IRQ3 Int Request 3 INB26 -DACK2 DMA Ack 2 OUTCount OUT B27 T/C TerminalB28 BALE Addrs Latch En OUTPower N/A B29 +5V +5vClk OUT B30 OSC 14.3MHzB31 GND Ground N/A B32 GND Ground N/APC/104总线接口P1B引脚信号名用途In/OutC0 GND Ground N/A C1 SBHE Bus High Enable I/OC2 LA23 Address bit 23 I/OC3 LA22 Address bit 22 I/OC4 LA21 Address bit 21 I/OC5 LA20 Address bit 20 I/OC6 LA19 Address bit 19 I/OC7 LA18 Address bit 18 I/OC8 LA17 Address bit 17 I/ORead I/O C9 -MEMR MemoryWrite I/OC10 -MEMW MemoryC11 SD8 Date Bit 8 I/OC12 SD9 Date Bit 9 I/OC13 SD10 Date Bit 10 I/OC14 SD11 Date Bit 11 I/OC15 SD12 Date Bit 12 I/OC16 SD13 Date Bit 13 I/OC17 SD14 Date Bit 14 I/OC18 SD15 Date Bit 15 I/OPin N/AC19 Key KeyPC/104总线接口P2C引脚信号名用途In/OutD0 GND Ground N/A D1 -MEMCS16 16-bit Mem Access IND2 -IOCS16 16-bit I/O Access IND3 IRQ10 Interrupt Request 10 IND4 IRQ11 Interrupt Request 11 IND5 **D6 IRQ15 Interrupt Request 15 IND7 IRQ14 Interrupt Request 14 IND8 -DACK0 DMA Acknowledge 0 OUTD9 DRQ0 DMA Request 0 IND10 -DACK5 DMA Acknowledge 5 OUTD11 DRQ5 DMA Request 5 IND12 -DACK6 DMA Acknowledge 6 OUTD13 DRQ6 DMA Request 6 IND14 -DACK7 DMA Acknowledge 7 OUTD15 DRQ7 DMA Request 7 INPower N/A D16 +5V +5VD17 -MASTER Bus Master Assert IND18 GND Ground N/A D19 GND Ground N/APC/104总线接口P2D。

系统总线的类型

系统总线的类型

1、ISA总线

ISA(industrialstandardarchitecture)总线标准是IBM公司1984年为推出PC/AT机而建立的系统总线标准,所以也叫AT总线。

它是对XT总线的扩展,以适应8/16位数据总线要求。

它在80286至80486时代应用非常广泛,以至于现在奔腾机中还保留有ISA总线插槽。

ISA总线有98只引脚。

2、EISA总线

EISA总线是1988年由Compaq等9家公司联合推出的总线标准。

它是在ISA总线的基础上使用双层插座,在原来ISA总线的98条信号线上又增加了98条信号线,也就是在两条ISA信号线之间添加一条EISA信号线。

在实用中,EISA总线完全兼容ISA总线信号。

3、VESA总线。

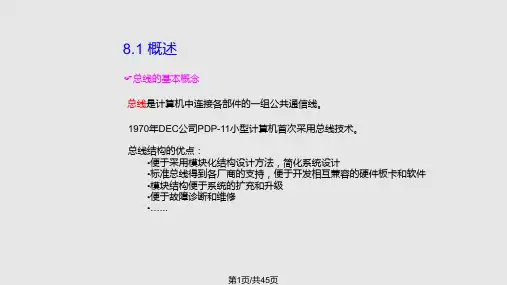

计算机基本接口原理——计算机系统的ISA总线计算机系统的ISA总线主ISISISA BUS的操作时序目要ISA BUS的基本特点ISA BUS是最早的计算机总线, 它是IBM公司倡导的开放的PC系统标准总线IS机(8086/8088为处理器) 系统随包ISA BUS的机械规格(1)XT槽AT槽机箱后部XT槽AT槽ISA BUS的机械规格(2)XT插分部分其中A,B,C和D等4部分,其中A1和B1位于计算机机箱的后部,A和C面为元件面,B和D面为焊接面。

共31x2+18x2=98个引脚。

各引脚的中心间距为0.1英寸(即2.54mm)允ISA BUS接口卡(仅用XT总线)“金手指”兼容ISA BUS的PC104总线模块XT部分AT部分XT部分CPU I/O扩展ISA BUS的电气信号(1)类型名称方向有效电平功能说明XT槽的电气信号(1)时钟与定位信号OSC O-周期为70ns的振荡信号,占空比1/2 CLK O-周期为176ns的系统时钟,占空比1/2 RESDRV O H系统复位信号0WS I H零等待状态信号数据总线SD0~SD7I/O-8位宽度的双向数据总线供电电源+5V,+12V-5V, -12VGND--为接口提供4种电源,注意:各电源能够提供给接口卡的功率取决于计算机的电源。

ISA BUS的电气信号(2)类型名称方向有效电平功能说明XT槽的电气信号(2)地址总线SA0~SA19O-20位宽度的地址总线BALE O H总线控制器发出的地址锁存允许允许信号AEN O HDMAC发出的允许DMA控制器控制地址总线、数据总线和读写控制线的标志信号IRQ3~7,9I H I/O接口的中断请求信号输入DRQ1~3I H I/O接口的DMA传输请求信号输入DACK1~3O L允许DMA传输应答信号输出类型名称方向有效电平功能说明XT槽的电气信号(3)控制总线T/C O L当前DMA通道计数器结束的标志信号IOR,IOW I/O L I/O接口的读和写控制信号SMEMR,SMEMW O L存储器的读和写控制信号输出(小于1M Bytes空间)I/OCHCK I L向CPU提供I/O或存储器奇偶错输入I/OCHRDY I HI/O通道就绪信号,若是低速I/O设备或存储器,在检测到一个有效地址或一个读/写命令时,使该信号变低,总线周期被自动延长整数倍(但不超过10倍)REFRESH I/O L存储器刷新周期指示信号类型名称方有效功能说明AT槽的电气信号(1)向电平数据总线SD8~SD15I/O-数据总线的高8位(双向数据总线)地址总线LA16~LA23I/O-存储器和I/O设备的最高7位地址SBHE I/O H高8位数据允许信号IRQ10~12, 14,15I H I/O接口的中断请求信号输入DRQ0,5~7I H I/O接口的DMA传输请求信号输入DACK0,5~7O L允许DMA传输应答信号输出类型名称方有效功能说明AT槽的电气信号(2)向电平控制总线MEMCS16I L存储器的16位片选信号输入I/OCS16I L I/O接口的16位片选信号输入MASTER I L外设控制总线的请求输入信号MEMR,MEMWI/O L存储器读和写控制信号(在整个16M Bytes空间内)供电电源+5VGND--+5V供电电源,给接口卡提供供电电源引脚和信号排列AT部分XT部分D面C面B面A面ISA BUS操作时序ISA BUS是一种多主控(Multi-Master)总线, 外设可以通过master信号申请控制总线IS存I/O读,I/O写中刷ISA BUS操作时序(1)8位存储器读/写操作时序ISA BUS操作时序(2)具有I/OCHRDY复位的8位存储器读/写操作时序具有0WS置位的8位存储器读/写操作时序具有I/OCHRDY复位的16位存储器读/写操作时序ISA BUS操作时序(5)8位I/O读/写操作时序ISA BUS操作时序(6)具有I/OCHRDY复位的8位I/O读/写操作时序具有0WS置位的8位I/O读/写操作时序ISA BUS操作时序(8)16位I/O读/写操作时序ISA BUS操作时序(9)具有I/OCHRDY复位的16位I/O读/写操作时序中断请求周期时序在中断请求周期中, IRQn信号有效与CLK是异步的, 首先通过PIC向CPU申请中断(INTR), IRQn与INTR都需要保持到CPU响应该中断请求为止ISA BUS操作时序(11)中断应答周期时序ISA BUS操作时序(12)具有1个等待状态的8MHzDMA传送周期时序总结ISA BUS的基本特点ISIS信号ISISISA总线的I/O读/写操作过程。

码和缓冲器被选通。

保持时间没有表示出来,然而它是存在的。

通常保持时间是通过在 WRITE 完成之后或对于 READ 是在总线上出现数据之后,延迟 SLAVE 信号一个保持时间而被加进受控设备的。

而主控接收到受控信号的转变之后,使它的动作推迟一个保持时间也同样可以把保持时间加到主控设备上。

全互锁异步协定的优点主要可靠性以及在处理通过较长总线连接且具有各种不同响应时间的设备时的高效率。

⒊ 半同步总线因为异步总线的传输延迟严重地限制了最高的频带宽度,因此,总线设计师结合同步和异步总线的优点设计出混合式的总线,即半同步总线,半同步总线的定时信号如图 8-4 所示。

这种总线有两个控制信号,即由主控来的 CLOCK 和受控来的 WAIT 信号,它们起着异步总线 MASTER 和 SLAVE 的作用,但传输延迟是异步总线的一半,这是因为成功的握手只需要一个来回行程。

对于快速设备,这种总线本质上是由时钟信号单独控制的同步总线。

如果受控设备快得足以在一个时钟周期内作出响应的话,那么它就不发 WAIT 信号。

这时的半同步总线像同步总线一样地工作。

如果受控设备不能在一个周期内作出响应,则它就使 WAIT 信号变高,而主控设备暂停。

只要 WAIT 信号高电平有效,其后的时钟周期就会知道主控设备处于空闲状态,当受控设备能响应时.它使 WAIT 信号变低,而主控设备运用标准同步协定的定时信号接收受控设备的回答。

这样,半同步总线就具有同步总线的速度和异步总线的适应性。

8.2 PC 总线PC 总线又称为在板局部总线。

即只是单板机上的 I/O 扩展总线,不支持多主CPU 的并行处理,不存在多 CPU 共享资源,不存在也不需要总线仲裁。

PC 机采用开放式的结构,即在底板上设置一些标准扩展插槽 (Slot) ,要扩充 PC 机的功能,只要设计符合插槽标准的适配器板,然后将板插入插槽即可。

一、 ISA 工业标准总线ISA 是工业标准体系结构 (Industrial Standard Architecture) 的缩写,是一种在原始 IBM PC 引入的 8 位总线结构, 1984 年在 IBM PC/AT 中将其扩展到 16 位。

isa总线标准定义作者:佚名来源:不详点击数:1050 更新时间:2008年01月08日isa总线标准ISA 是Industry Standard Architecture 的缩写ISA插槽是基于ISA总线(Industrial Standard Architecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。

其工作频率为8MHz左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡已及所谓的多功能接口卡等扩展插卡。

其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。

ISA 是8/16bit 的系统总线,最大传输速率仅为8MB/s ,但允许多个CPU 共享系统资源。

由于兼容性好,它在上个世纪80年代是最广泛采用的系统总线,不过它的弱点也是显而易见的,比如传输速率过低、CP U占用率高、占用硬件中断资源等。

后来在PC‘98 规范中,就开始放弃了ISA 总线,而Intel 从i810 芯片组开始,也不再提供对ISA 接口的支持。

ISA总线扩展插槽由两部分组成,一部分有62引脚,其信号分布及名称与PC/XT总线的扩展槽基本相同,仅有很小的差异。

另一部分是AT机的添加部分,由36引脚组成。

这36引脚分成两列,分别称为C列和D列。

isa接口卡的外观isa插槽的外观ISA接口引脚定义引脚定义方向说明A1 /I/O CH CK I/O channel check; active low=parity errorA2 D7 Data bit 7A3 D6 Data bit 6A4 D5 Data bit 5A5 D4 Data bit 4A6 D3 Data bit 3A7 D2 Data bit 2A8 D1 Data bit 1A9 D0 Data bit 0A10 I/O CH RDY I/O Channel ready, pulled low to lengthen memory cycles A11 AEN Address enable; active high when DMA controls busA12 A19 Address bit 19A13 A18 Address bit 18A14 A17 Address bit 17A15 A16 Address bit 16A16 A15 Address bit 15A17 A14 Address bit 14。

ISA总线ISA总线是采用80286 CPU的 IBM PC/AT机中使用的总线,它是在8位的PC/XT总线的基础上扩展而成的16位总线结构。

该总线同8位的 PC/XT总线保持了即兼容性。

80286与8088 CPU最明显的差别在于数据信号的位数,8088对外的数据总线只有8位,而80286为16位。

为了使ISA总线与原有的XT总线相兼容,ISA 总线保留了原有XT总线的所有信号,仅作了部分新的定义,而另外增加了高位的数据信号和与此有关的扩展信号,诸如SBHE、-MEMCS16、-IOCS16等信号。

除了数据传输线增加外,寻址能力的增加也是提高性能的方式。

80286的寻址能力达到了16MB,这样相应的 ISA总线上的地址信号也增加到了24条,即增加了4条(LA20~LA23)。

随着 PC系统的发展,外围设备的类型也不断增加,对于硬件中断与 DMA 通道也提出了更多的要求,原有的6个中断请求与3个 DMA通道已不能满足需要, ISA总线将中断的数目由6个扩充到15个,而 DMA通道则由3个增加到8个。

ISA总线扩展槽的插座是在原来 XT总线(62线)的基础上增加了一条短插座,该短插槽有36个引脚,并且与原 XT插槽在一条直线上,因此加上原来 XT 总线的62线,一共有98个引脚。

表3- 5列出了 ISA总线增加信号的排列。

表3- 5 ISA总线增加的36芯的信号定义在ISA总线上62芯和36芯插座上重新定义和增加的信号:(l)地址总线LA17~LA23(I/O):ISA总线中新增的地址信号线,可以给系统提供多达16MB 的寻址能力。

此信号在ALE信号为高电平时才有效,并且在 CPU周期过程中是不锁定的,因此并不保持整个周期有效,它们的用途是为一个等待状态存储周期生成存储器译码信号。

(2)数据总线SD8~SD15(I/O):系统数据总线的高字节信号,为存储器和I/O接口提供高8位总线数据。

为保持与XT总线的兼容性,可通过增加的16位存储器或16位I/O接口控制信号确定所用的数据线位数。

ISA总线概述ISA总线: (Industry Standard Architecture:工业标准体系结构)是IBM公司为PC/AT电脑而制定的总线标准,为16位体系结构,只能支持16位的I/O设备,数据传输率大约是16MB/S。

也称为AT标准。

开始时PC机面向个人及办公室,定义了8位的ISA总线结构,对外公开,成为标准(ISO ISA标准)。

第三方开发出许多ISA扩充板卡,推动了PC机的发展。

1984年推出IBM-PC/AT系统,ISA从8位扩充到16位,地址线从20条扩充到24条。

1988年,康柏、HP、NEC等9个厂商协同把ISA扩展到32位,即EISA总线(Extended ISA)。

ISA总线引线定义RESET、BCLK:复位及总线基本时钟,BLCK=8MHz。

SA19-SA0:存储器及I/O空间20位地址,带锁存。

LA23-LA17:存储器及I/O空间20位地址,不带锁存。

BALE:总线地址锁存,外部锁存器的选通。

AEN:地址允许,表明CPU让出总线,DMA开始。

SMEMR#、SMEMW#:8位ISA存储器读写控制。

ISA总线引线定义:主要信号说明MEMR#、MEMW#:16位ISA存储器读写控制。

SD15-SD0:数据总线,访问8位ISA卡时高8位自动传送到SD7-SD0。

SBHE#:高字节允许,打开SD15-SD8数据通路。

MEMCS16#、IOCS16#:ISA卡发出此信号确认可以进行16位传送。

I/OCHRDY:ISA卡准备好,可控制插入等待周期。

NOWS#:不需等待状态,快速ISA发出不同插入等待。

I/OCHCK#:ISA卡奇偶校验错。

IRQ15、IRQ14、IRQ12-IRQ9、IRQ7-IRQ3:中断请求。

DRQ7-DRQ5 、DRQ3-DRQ0: ISA卡DMA请求。

DACK7#-DACK5#、DACK3#-DACK0#:DMA请求响应。

MASTER#:ISA主模块确立信号,ISA发出此信号,与主机内DMAC配合使ISA卡成为主模块,全部控制总线。

ISA总线介绍范文ISA(Industry Standard Architecture)总线是一种计算机总线标准,用于将计算机的中央处理器(CPU)、内存和输入/输出设备连接在一起。

它是IBM PC/AT计算机中使用的主要总线标准,它的发展历史可以追溯到1980年代初。

本文将介绍ISA总线的历史、特点和发展,并分析其对计算机技术的影响。

ISA总线最早是于1981年由IBM公司引入,用于IBMPC/AT计算机。

它是一个16位总线,传输速度为4.77MHz。

ISA总线提供了扩展插槽,用于插入各种类型的ISA适配器卡,如图形卡、声卡、网络卡等等。

这些适配器卡通过总线与主板上的CPU和内存通信,实现计算机系统的功能扩展。

ISA总线的特点有几个方面。

首先,它是一个并行总线,可以一次传输多个位的数据。

其次,它是非同步总线,即数据传输的时钟频率可以与CPU和内存的时钟频率不同。

ISA总线还采用了基于共享中断请求(IRQ)和直接内存访问(DMA)的中断和数据传输方式,这大大减轻了CPU的负担。

然而,随着计算机技术的发展,ISA总线逐渐暴露出一些问题。

首先,它的传输速度相对较慢,无法满足日益增长的计算机性能需求。

其次,ISA总线的设计限制了计算机系统的扩展能力,无法支持更多的设备和功能。

此外,ISA总线还存在复杂的硬件技术和软件兼容性问题。

然而,由于许多早期的计算机系统中仍然使用ISA适配器卡,为了保持与这些系统的兼容性,计算机制造商仍然在主板上提供了ISA插槽。

随着时间的推移,由于硬件技术和市场需求的变化,ISA插槽逐渐被PCI插槽所取代,直到2000年左右,主流计算机系统中已经没有ISA插槽了。

然而,即使在今天,仍有一些老旧的计算机系统或嵌入式系统使用ISA总线。

此外,由于在一些特殊应用中,ISA总线仍然具有一些独特的优势,如兼容性、成本和稳定性,因此还有一些ISA适配器卡仍然在市场上销售。

总的来说,ISA总线虽然已经被更高性能的PCI总线所取代,但作为计算机技术发展的重要里程碑之一,它对计算机系统的发展产生了重要影响。

ISA总线ISA总线是IBM PC/AT机(CPU是80286)所用的系统总线:PC/AT总线经过标准化之后的名称,IEEE将ISA总线作为IEEE P996推荐标准,这是一个16位兼8位的总线标准。

如果忽略标准化细节,则可认为16位ISA总线就是PC /AT总线。

由于IBM PC/AT与IBM PC、IBM PC/XT机(CPU都是8088)所用的Pc总线兼容,所以可认为8位ISA总线(16位ISA总的低8位部分)就是PC 总线。

引脚信号图9.1所示为16位ISA总线板卡(又称I/O扩展板或接口板)及插槽外形示意图,元件面和焊接面共有31+18个引脚(A1~A31、B1~B31、C1~C18和D1~D18),其中A1~A31、Bl~B31是低8位部分即8位ISA总线所用的信号。

8位ISA总线板卡及插槽与该图的区别在于没有36个引脚(C1一C18和D1~D18)那部分。

显然,8位ISA总线板卡可以插在16位的插槽中。

表9.1给出了16位ISA总线前62个引脚(亦是8位ISA总线的全部引脚)信号定义,表9.2给出了16位ISA总线的后36个引脚信号定义。

下面对引脚信号做一些简要说明,首先是62线部分(8位ISA总线)。

①D7~DO:8位数据线,双向,三态。

对于16位ISA总线,它们是数据线的低8位。

②A19~A0:20位地址线,输出。

③SMEMR(上划线)、SMEMW(上划线):存储器读、写命令,输出,低电平有效。

④IOR(上划线)、IOW(上划线):I/O读、写命令,输出,低电平有效⑤AEN:地址允许信号,输出,高电平有效。

该信号由DMAC发出,为高表示DMAC正在控制系统总线进行DMA传送,所以它可用于指示DMA总线周期。

⑥BALE:总线地址锁存允许,输出。

该信号在CPU总线周期的Tl期间有效,可作为CPU总线周期的指示。

⑦I/O CH RAY:I/O通道准备好,输入,高电平有效。

该引脚信号与808 6的READY功能相同,用于插入等待时钟周期。

⑧I/OCHCK(上划线):I/0通道校验,输入,低电平有效。

它有效表示板卡上出现奇偶校验错。

⑨IRQ7~IRQ2:6个中断请求信号,输入,分别接到中断控制逻辑的主8259A的中断请求输入端IR7~IR2(参看第五章的图5.23)。

这些信号由低到高的跳变表示中断请求,但应一直保持高电平,直到CPU响应中断为止。

它们的优先级别与所连接的IR线相同,即IRQ2在这6个请求信号中级别最高,IRQ7的级别最低。

⑩DRQ3~DRQl:3个DMA请求信号,输入,高电平有效。

它们分别接到DMA控制器8237A的DMA请求输入端DREQ3~DREQl。

因此,优先级别与它们相对应(D RQ1的级别最高,DRQ 3的级别最低)。

⑪DACK3(上划线)~DACKl(上划线):3个DMA响应信号,输出,低电平有效。

⑫T/C:计数结束信号,输出,高电平有效。

它由DMAC发出,用于表示进行DMA传送的通道编程时规定传送字节数已经传送完。

但它没有说明是哪个通道,这要结合DMA响应信号DACK(上划线)来判断。

⑬OSC:振荡器的输出脉冲。

⑭CLK:系统时钟信号,输出。

系统时钟的频率通常在4.77 MHz一8 MHz内选择,最高频率为8.3 MHz。

CLK是由()SC的输出3分频产生的,也就是说()SC的频率应是CLK的3倍。

⑮RESET:系统复位信号,输出,高电平有效。

该信号有效时表示系统正处于复位状态,可利用该信号复位总线板卡上的有关电路。

⑯NOWS:零等待状态,输入,低电平有效。

用于缩短按照缺省设置应等待的时钟数,当它有效时,不再插入等待时钟。

⑰REFRESH(上划线):刷新信号,双向,低电平有效,由总线主控器的刷新逻辑产生。

该信号有效表示存储器正处于刷新周期,以下是对36线部分16位ISA总线的高8位)的简要说明:⑱ SDl5~SD8:数据总线的高8位,双向,三态。

⑲SBHE:总线高字节传送允许,三态信号。

该信号用来表示SDl5~SD8上正进行数据传送。

⑳LA23~LAl7:非锁存的地址线,在BALE为高电平时有效。

将它们锁存起来,并和已锁存的低位地址线(A19~A0)组合在一起,可形成24位地址线,因而使系统的寻址能力扩大到16 MB。

_MEMR(上划线),MEMW(上划线):存储器读、写信号,低电平有效。

这两个信号在所有的存储器读或写周期有效。

相比之下,前面所介绍的SMEMR(上划线)和SMEMW(上划线)仅当访问存储器的低1 MB时才有效。

+MEMCSl6(上划线):存储器片选16,输入,低电平有效。

该信号用来表示当前的数据传输是具有一个等待时钟的16位存储器总线周期。

1 I/OCCSl6(上划线):I/O片选16,输入,低电平有效。

该信号为集电极开路,为低表示当前的数据传输是具有一个等待时钟的16位I/O总线周期。

2 MASTER(上划线):总线主控信号,输入,在ISA总线的主控器初始化总线周期时产生,低电平有效。

该信号与I/O通道上的I/0处理器的DRQ 线一起用于获取对系统总线的控制权。

3 IRQl5~IRQ10:6个中断请求信号,输入,接到中断控制逻辑的从8 259A。

4 DRQ7~DRQ5、DACK7(上划线)~DACK5(上划线)、DACK0(上划线):通道7~5的DMA请求和相应的DMA响应信号(另有一个通道0的响应信号)。

这3个通道可进行16位DMA传送。

ISA总线时序ISA总线的时序和8086/8088的时序基本相同,但也有一些区别。

有了8086/8088时序基础,对ISA总线时序的理解主要在于以下几点:①地址和数据已不再分时复用信号线,因此在整个总线周期内有效。

②和8086/8088的最大模式一样,存储器读/写和I/O读/写的控制信号已分开,进行一种操作只需一个控制信号。

③一个典型的存储器读/写周期还是由T1、T2、T3和T4组成,而I/O读/写周期和DMA周期都自动插入了一个等待时钟周期。

④I/O CH RAY相当于8086/8088时序中的:READY信号,当总线板卡上的存储器或I/0电路较慢时,可利用该信号迫使CPU插入等待时钟周期,但等待时钟周期不得超过10个。

⑤8位ISA总线在存储器读/写周期可用到20位地址,而16位.|SA总线在存储器读/写周期中可使用24位地址。

但由于受I/O指令的限制,8位和16位ISA总线的I/0读/写周期都只能使用低16位地址。

⑥BALE在CPU总线周期的T1期间有效,它的基本作用是进行地址锁存,但也可以作为一个新的CPU总线周期已开始的标志。

⑦AEN有效表示DMAC正在控制系统总线,所以它可以作为系统处于DMA 总线周期的标志。

ISA总线接口执行ISA总线规范的电路称为。

ISA总线接口。

通过ISA总线接口可以为系统扩充存储器,也可以扩充I/O设备。

在实际应用中对后者的需求更大,因为机器主板上一般已经或者可以安装足够的存储器,而I/O设备是各种各样的,系统对I/O设备的需求也不尽相同。

正因为如此,ISA总线又被归类于I/O扩展总线。

注意,I/O设备是一个广义的概念,可以是像打印机、硬盘那样实实在在的设备,也可以是像A/D转换器、D/A转换器、计数器那样的电路。

当I/O设备是一个电路时,通常和总线接口做在一个总线板卡上,习惯称之为某某接口板(如A/D接口板)或某某接口(如D/A接口)。

从ISA总线的引脚信号以及总线时序看,和8086/8088最大模式时的系统三总线以及8086/8088的总线周期时序差别不大,因此,在设计ISA总线接口特别是I/O接口时,除了下面三点需要注意外,可以采用与设计8086/8088接口几乎相同的方法。

这三点是:1.当设计非DMA方式的I/O接口时,应把AEN为低作为该接口工作的使能条件,以确保在总线上进行DMA传送时该接口不工作,否则DMA传送时所发出的地址与该接口设计地址相同时该接口会误操作。

2.系统对ISA总线上的I/O端口地址采用部分译码方法,只译码A9~AO或A10~A0,在选择接口地址时应避开系统已占用的地址以及它们的重叠区。

③如果所要设计的接口中包含需要CPU插入等待时钟的功能,则需设计一个I/0 CHRAY产生电路,以便在必要时使总线上的I/O CH RAY线为低电平。

但该电路与总线上的I/O CH RAY线的电气连接以及有效信号出现和持续时间等方面有一些要求,实际应用时需再参阅其详细资料。

第六章已经举了一个ISA总线接口的例子——可编程定时中断请求产生电路。

为使读者进一步了解ISA总线接口的设计,这里再举一例。

例9.1 设计能采集24路脉冲量的8位ISA总线接口,要求基地址可变。

为了能读取计数器的工作状态,这里选用8254。

适当选取采样时间间隔,可保证在下一次采样之前16位的计数器不会计满(即记录的脉冲数不超过65535),这样用8片8 254即可。

为使占用的端口地址连续且译码电路简单,这里用一片3线一8线译码器(74LSl 38)来产生8个8254片选信号。

读取计数器的值一般采用程序直接控制方式,即该接口工作于非DMA方式,因此应把AEN为低作为该接口工作的使能条件。

显然,这应安排在能对整个接口电路起作用的地方。

这里的做法是:将AEN作为基地址可变电路中的二进制数比较器74LS688的使能信号,当AEN为低时,74LS688能工作,从而使译码器74LSl38以及作为数据缓冲器的74LS245在本接口所用任一地址出现时也能工作,此时能对8254进行正常读/写;当总线中有DMA操作时,AEN变成高电平,74LS 688被禁止,使得74LSl38和74LS245也被禁止,于是,8254与外界的联系被切断,不会被误操作。

图9.2所示是该接口的具体电路图,读者可以自行分析,并参考进行一些.ISA总线接口设计。