ISA总线与高速数据采集卡的接口技术

- 格式:pdf

- 大小:198.95 KB

- 文档页数:6

系统ISA接口实现原理钧天科技有限公司版权所有侵权必究目录上框ISA接口的具体实现:(AUX侧) (4)上框ISA接口的具体实现:(单板侧) (5)下框ISA接口的具体实现:(TSI侧) (6)下框ISA接口的具体实现:(单板侧) (6)8930系统的ISA总线按照上下框分了两路,上框由AUX出,下框由主备TSI分别出主备ISA总线。

上下框的ISA总线原理一样,所不同的是下框ISA总线有主备,各线路板的ISA接口需要进行选择。

上框ISA接口的具体实现:(AUX侧)AUX上面的数据,地址总线由850小系统扣板而来,到上框各单板的片选信号由AUX扣板的高位地址A[24:21]经FPGA译码而得,读写信号直接由850小系统扣板而来24位地址用CPU输出的读写信号MR/W控制245的数据方向,用/CS_OUTA信号控制245的通断。

MR/W:MR/W由扣板的CPU经过244直接输出MR/W为高时,AUX读上框各单板的数据,245数据由背板到AUXMR/W为低时,AUX写上框各单板的数据,245数据由AUX到背板/CS_OUTA:/CS_OUTA由AUX输出的到各单板的片选信号在逻辑里或门输出/CS_OUTA为高时,245关断,/CS_OUTA为低时,245打开请看原理图。

地址线不经过任何控制,仅由244隔离,直接输出到背板。

上框ISA接口的具体实现:(单板侧)在8930系统中,通过244,245把背板ISA总线和单板ISA总线进行隔离,通过CPLD管脚输出2个信号/OE_ADDR_A, /OE_DATA_A控制244,245的通断。

这2个OE信号在单板进行上拉.单板ISA总线能进行工作条件:(由245的/OE管脚控制)1. 扣板不在位2. 该槽位的片选信号有效在CPLD检测到扣板不在位或片选信号有效时,打开245的\OE门。

各单板还用DIR_DA TA_A信号控制ISA数据总线的流向DIR_DATA_A由背板WR信号决定:(可以不经过CPLD,直接把由母板过来的W/R信号连接到245的DIR管脚。

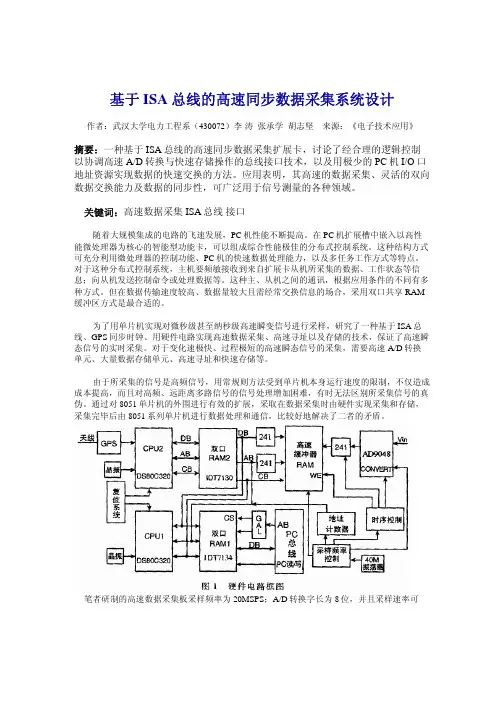

基于ISA总线的高速同步数据采集系统设计作者:武汉大学电力工程系(430072)李涛张承学胡志坚来源:《电子技术应用》摘要:一种基于ISA总线的高速同步数据采集扩展卡,讨论了经合理的逻辑控制以协调高速A/D转换与快速存储操作的总线接口技术,以及用极少的PC机I/O口地址资源实现数据的快速交换的方法。

应用表明,其高速的数据采集、灵活的双向数据交换能力及数据的同步性,可广泛用于信号测量的各种领域。

关键词:高速数据采集 ISA总线接口随着大规模集成的电路的飞速发展,PC机性能不断提高。

在PC机扩展槽中嵌入以高性能微处理器为核心的智能型功能卡,可以组成综合性能极佳的分布式控制系统。

这种结构方式可充分利用微处理器的控制功能、PC机的快速数据处理能力,以及多任务工作方式等特点。

对于这种分布式控制系统,主机要频敏接收到来自扩展卡从机所采集的数据、工作状态等信息;向从机发送控制命令或处理数据等。

这种主、从机之间的通讯,根据应用条件的不同有多种方式。

但在数据传输速度较高、数据量较大且需经常交换信息的场合,采用双口共享RAM 缓冲区方式是最合适的。

为了用单片机实现对微秒级甚至纳秒级高速瞬变信号进行采样,研究了一种基于ISA总线、GPS同步时钟、用硬件电路实现高速数据采集、高速寻址以及存储的技术,保证了高速瞬态信号的实时采集。

对于变化速极快、过程极短的高速瞬态信号的采集,需要高速A/D转换单元、大量数据存储单元、高速寻址和快速存储等。

由于所采集的信号是高频信号,用常规则方法受到单片机本身运行速度的限制,不仅造成成本提高,而且对高频、远距离多路信号的信号处理增加困难,有时无法区别所采集信号的真伪。

通过对8051单片机的外围进行有效的扩展,采取在数据采集时由硬件实现采集和存储,采集完毕后由8051系列单片机进行数据处理和通信,比较好地解决了二者的矛盾。

笔者研制的高速数据采集板采样频率为20MSPS;A/D转换字长为8位,并且采样速率可变;存储容量为512K字节,符合ISA总线标准。

pcie高速采集卡的采样原理

PCIe高速采集卡(PCIe high-speed acquisition card)是一种用于数据采集和信号处理的硬件设备,它通过PCI Express(PCIe)接口与计算机连接。

采集卡的采样原理可以概括为以下几个步骤:

1. 时钟同步:采集卡首先需要与输入信号进行时钟同步,以确保准确的采样。

一般情况下,采集卡会使用自己的时钟源或者外部的参考时钟来与输入信号进行同步。

2. 信号采样:一旦时钟同步完成,采集卡就开始对输入信号进行采样。

采样过程中,采集卡会按照一定的采样率(即每秒采样的次数)将输入信号离散化为数字信号。

采集卡上的模数转换器(ADC)负责将连续的模拟信号转换为离散的数字信号。

3. 数据传输:采集卡将采样到的数字信号通过PCIe接口传输给计算机。

PCIe接口提供了高速的数据传输通道,能够满足高速数据采集的需求。

传输过程中,采集卡会将采样数据打包成数据包,并通过PCIe总线发送给计算机。

4. 数据处理:计算机接收到采集卡传输的数据后,可以使用相应的软件对数据进行处理和分析。

这些软件可以根据具体的应用需求,对数据进行滤波、频谱分析、数据压缩等操作,以提取所需的信息。

需要注意的是,采集卡的采样原理会因具体的硬件设计而有所差异,不同的采集卡可能会采用不同的ADC芯片、时钟同步方式和数据处理算法等。

因此,在具体应用中,需要根据采集卡的规格和说明书来了解其采样原理和技术特点。

PCI,ISA,AGP,SATA接口介绍.txt18拥有诚实,就舍弃了虚伪;拥有诚实,就舍弃了无聊;拥有踏实,就舍弃了浮躁,不论是有意的丢弃,还是意外的失去,只要曾经真实拥有,在一些时候,大度舍弃也是一种境界。

PCI插槽是基于PCI局部总线(Pedpherd Component Interconnect,周边元件扩展接口)的扩展插槽,其颜色一般为乳白色,位于主板上AGP插槽的下方,ISA插槽的上方。

其位宽为32位或64位,工作频率为33MHz,最大数据传输率为133MB/sec(32位)和266MB/sec(64位)。

可插接显卡、声卡、网卡、内置Modem、内置ADSL Modem、USB2.0卡、IEEE1394卡、IDE接口卡、RAID卡、电视卡、视频采集卡以及其它种类繁多的扩展卡。

PCI插槽是主板的主要扩展插槽,通过插接不同的扩展卡可以获得目前电脑能实现的几乎所有功能,是名副其实的“万用”扩展插槽。

ISA插槽是基于ISA总线(Industrial Standard Architecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。

其工作频率为8MHz 左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡已及所谓的多功能接口卡等扩展插卡。

其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。

目前还能在许多老主板上看到ISA插槽,现在新出品的主板上已经几乎看不到ISA插槽的身影了,但也有例外,某些品牌的845E主板甚至875P主板上都还带有ISA插槽,估计是为了满足某些特殊用户的需求。

AGP插槽是基于Intel出台的AGP(Accelerated Graphics Port)规范而制造的专门用于显卡的主板扩展插槽.AGP插槽不与PCI、ISA插槽处于同一水平位置,而是内进一些,通常都是棕色。

AGP插槽按倍速来区分,主要经历了AGP 1X、AGP 2X、AGP 4X、AGP PRO-即AGP 8X。

ASI异步串行口,SDI、TS、ASI、DS3码流的区别就是传输流数据信号的一种接口类型有三种:即同步并行接口(SPI) 改:SPI全称是"Serial Peripheral Interface",意为串行外围接口,不是什么同步并行接口,是串行的.、异步串行接口(ASI)和同步串行接口(SSI)。

其中,ASI和SPI接口较常用。

ASI接口的数据传输速率为270Mb/s,在进行码率调整之前,需要将ASI接口中的同步字节删除,进行串并转换,再进一步处理。

SPI接口传输数据率可变,帧与帧之间必须是连续的。

ASI接口卡的主要功能是将MPEG-2的传送流数据用DVB-ASI或SPI接口以恒定码率传送出去。

传送流数据可以是编码器、复用器或者别的传送流产生器产生并通过计算机的PCI总线按批传送至该传送卡。

传送卡先将数据缓存,然后根据用户所要求的输出码率将数据输出。

传送码率可在用户控制界面上预先设定,要求该码率与数据输入速率保持一致。

可应用于图像传输系统、数据传输系统、监控系统、电视会议系统、机顶盒前端等。

我们在使用编解码、复用、适配设备时常常会接触到TS流、SDI、ASI、SD3接口,它们的说明书也常常把ASI称作TS流,它们之间有什么不同呢?我们知道模拟信号(也叫连续信号)经过抽样、量化后变成在时间和幅度上都不连续的信号(也叫离散信号),这样的信号还不是数字信号,需要把离散信号转换成数字符号(如自然二进制码),这种码流是没有经过编码压缩的基带信号,码率较大,占用较大的传输带宽,这种码流的传输接口是SDI接口,也叫串行数字接口,码率是270 M,它属于信道码流,有些厂家的编码器除了复合视频输入端口还有SDI输入端口。

TS流是信源码流,最高码率为44.209 Mbit/s,它是经过信源编码后的压缩码流,为了使欲传输的信源信息在传输速率一定的条件下更快更多地传输,还要把数据进行压缩,也就是通过信源编码去掉信息中多余的部分,从而提高通信的有效性,信源编码包括霍夫曼编码、LZ 编码等多种SDI 是Serial Digital Interface 的缩写,也就是串行数字接口串行接口是把数据字的各个比特以及相应的数据通过单一通道顺序传送的接口。

解释isa总线,eisa总线及pci总线的工作特点

ISA、EISA和PCI总线的工作特点如下:

1.ISA总线:

•数据传输速率较慢,最大传输速率仅为8MB/s。

•允许多个CPU共享系统资源,但CPU资源占用较高,且数据传输带宽较小。

•基于ISA总线的扩展插槽颜色一般为黑色,长度比PCI接口插槽要长。

•已逐渐被淘汰,被PCI总线所取代。

2EISA总线:

•具有较大的带宽,约为32位数据总线,最高可达33MHz。

•传输速度较快,最高可达20MB/s。

•提供16个插槽,更好地支持外围设备的安装和升级。

•支持多种新技术和功能特性,如内存映射、DMA控制器、中断控制器等。

3PCI总线:

•具有地址数据多路复用的高性能的32位或64位同步总线。

•总线引脚数目和部件数量较少,降低了成本及布线的复杂度。

•支持线性突发传输模式,确保了总线不断满载数据进行高速传输。

•设计独立于处理器的,具有严格的总线规范和良好的兼容性。

•隐蔽的总线仲裁减小了仲裁开销,极小的存取延迟,采用总线主控和异步数据转移操作。

•提供数据和地址奇偶校验功能,保证了数据的完整性和准确性。

•与CPU的时钟频率无关,能支持多个外设,设备间通过局部总线可以完成数据的快速传递,有效解决了数据传输的瓶颈问题。

•对扩展卡和元件能够进行自动配置,实现设备的即插即用。

总的来说,PCI总线在数据传输速率、设计灵活性、兼容性和扩展性等方面具有优势,因此在现代计算机系统中得到广泛应用。

基于ISA的高速数据采集系统的设计【摘要】在我国常用的通道式数据接收机中,实现波形处理主要依靠高速数据采集系统。

在本文实践研究中,笔者在设计一个能够基于ISA总线的高速数据采集系统,采用了目前应用比较广泛的先进先出(FIFO)、A/D转换器,该系统的数据采集频率可达到50MHz,同时在数据采集与主机异步数据传送时采用I、Q正交双通道结构;系统设计完成之后分析系统的ADC动态特性,分析结果显示系统高速数据采集系统的设计完全能够满足系统预期指标。

【关键词】高速ADC;动态特性;ISA总线引言随着科学技术的发展和数据采集系统的广泛应用,针对数据采信系统人们提出了更高的要求,其主要包括采样频率、精度、分辨率、控制方式及输入电压范围等方面的主要技术指标。

本研究中,笔者在介绍数据采集技术的一些基本概念的基础上,重点讨论高速数据采集系统的设计和实现,并对系统的ADC动态特性进行了分析。

1、数据采集基本技术所谓数据采集,是指采集一些模拟信号(模拟量)将其转换为数字信息(数字量),然后再经储存、处理及显示的整个过程。

如下图1-1为典型的数据采集系统框图。

如上图1-1所示,我们假设通过数据采集系统采集多路模拟量,对A/D转换器与各路模拟量之间的通道采用模拟多路开关进行轮流切换,从而使其在一个特定的时间内,只有一路模拟量信号能够输入到A/D转换器,以此达到分时转换的目的。

A/D转换器为采样通道的核心,它决定着数据采集的精度和速度这两大指标因素。

1.1数据采集的相关参数分析数据采集中所涉及到的采样定理、编码、量化过程及误差、采样方式等数据采集中的一些基本概念,以下将进行分析介绍。

(1)信号采样、量化及编码通常一个带宽模拟信号x(t)根据采样定理限制在0~fm,均匀采样值由唯一的一系列时间间隔不大于1/2fm秒进行确定。

这在信号为最高频率的情况下,相当于每一周期提最采样值最少要两个,Xs(nT)为设采样后所得到的采样信号,采样间隔为Ts。

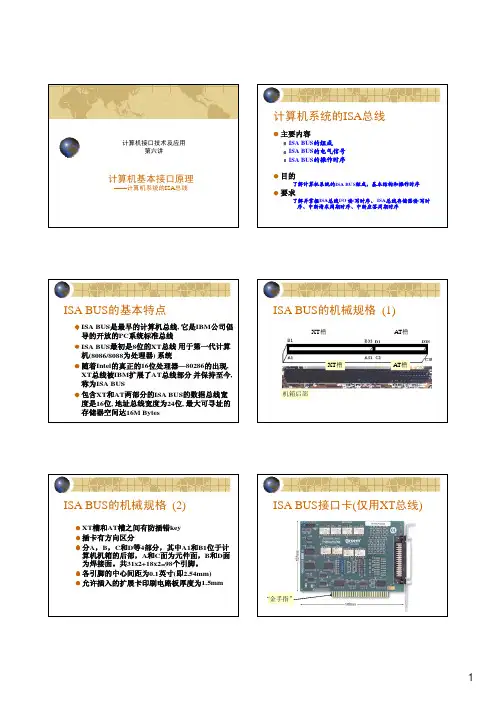

计算机基本接口原理——计算机系统的ISA总线计算机系统的ISA总线主ISISISA BUS的操作时序目要ISA BUS的基本特点ISA BUS是最早的计算机总线, 它是IBM公司倡导的开放的PC系统标准总线IS机(8086/8088为处理器) 系统随包ISA BUS的机械规格(1)XT槽AT槽机箱后部XT槽AT槽ISA BUS的机械规格(2)XT插分部分其中A,B,C和D等4部分,其中A1和B1位于计算机机箱的后部,A和C面为元件面,B和D面为焊接面。

共31x2+18x2=98个引脚。

各引脚的中心间距为0.1英寸(即2.54mm)允ISA BUS接口卡(仅用XT总线)“金手指”兼容ISA BUS的PC104总线模块XT部分AT部分XT部分CPU I/O扩展ISA BUS的电气信号(1)类型名称方向有效电平功能说明XT槽的电气信号(1)时钟与定位信号OSC O-周期为70ns的振荡信号,占空比1/2 CLK O-周期为176ns的系统时钟,占空比1/2 RESDRV O H系统复位信号0WS I H零等待状态信号数据总线SD0~SD7I/O-8位宽度的双向数据总线供电电源+5V,+12V-5V, -12VGND--为接口提供4种电源,注意:各电源能够提供给接口卡的功率取决于计算机的电源。

ISA BUS的电气信号(2)类型名称方向有效电平功能说明XT槽的电气信号(2)地址总线SA0~SA19O-20位宽度的地址总线BALE O H总线控制器发出的地址锁存允许允许信号AEN O HDMAC发出的允许DMA控制器控制地址总线、数据总线和读写控制线的标志信号IRQ3~7,9I H I/O接口的中断请求信号输入DRQ1~3I H I/O接口的DMA传输请求信号输入DACK1~3O L允许DMA传输应答信号输出类型名称方向有效电平功能说明XT槽的电气信号(3)控制总线T/C O L当前DMA通道计数器结束的标志信号IOR,IOW I/O L I/O接口的读和写控制信号SMEMR,SMEMW O L存储器的读和写控制信号输出(小于1M Bytes空间)I/OCHCK I L向CPU提供I/O或存储器奇偶错输入I/OCHRDY I HI/O通道就绪信号,若是低速I/O设备或存储器,在检测到一个有效地址或一个读/写命令时,使该信号变低,总线周期被自动延长整数倍(但不超过10倍)REFRESH I/O L存储器刷新周期指示信号类型名称方有效功能说明AT槽的电气信号(1)向电平数据总线SD8~SD15I/O-数据总线的高8位(双向数据总线)地址总线LA16~LA23I/O-存储器和I/O设备的最高7位地址SBHE I/O H高8位数据允许信号IRQ10~12, 14,15I H I/O接口的中断请求信号输入DRQ0,5~7I H I/O接口的DMA传输请求信号输入DACK0,5~7O L允许DMA传输应答信号输出类型名称方有效功能说明AT槽的电气信号(2)向电平控制总线MEMCS16I L存储器的16位片选信号输入I/OCS16I L I/O接口的16位片选信号输入MASTER I L外设控制总线的请求输入信号MEMR,MEMWI/O L存储器读和写控制信号(在整个16M Bytes空间内)供电电源+5VGND--+5V供电电源,给接口卡提供供电电源引脚和信号排列AT部分XT部分D面C面B面A面ISA BUS操作时序ISA BUS是一种多主控(Multi-Master)总线, 外设可以通过master信号申请控制总线IS存I/O读,I/O写中刷ISA BUS操作时序(1)8位存储器读/写操作时序ISA BUS操作时序(2)具有I/OCHRDY复位的8位存储器读/写操作时序具有0WS置位的8位存储器读/写操作时序具有I/OCHRDY复位的16位存储器读/写操作时序ISA BUS操作时序(5)8位I/O读/写操作时序ISA BUS操作时序(6)具有I/OCHRDY复位的8位I/O读/写操作时序具有0WS置位的8位I/O读/写操作时序ISA BUS操作时序(8)16位I/O读/写操作时序ISA BUS操作时序(9)具有I/OCHRDY复位的16位I/O读/写操作时序中断请求周期时序在中断请求周期中, IRQn信号有效与CLK是异步的, 首先通过PIC向CPU申请中断(INTR), IRQn与INTR都需要保持到CPU响应该中断请求为止ISA BUS操作时序(11)中断应答周期时序ISA BUS操作时序(12)具有1个等待状态的8MHzDMA传送周期时序总结ISA BUS的基本特点ISIS信号ISISISA总线的I/O读/写操作过程。

数据采集 电 子 测 量 技 术 EL ECTRONIC M EASUREM EN T TEC HNOLO GY 第31卷第6期2008年6月 基于ISA总线的数据采集卡的设计及应用贺小亮1 李艾华1 王帆胜2(1.第二炮兵工程学院502教研室 西安 710025;2.中国人民解放军第6916工厂 廊坊 065000)摘 要:本文介绍了基于ISA总线的数据采集卡的硬件电路和软件设计。

针对传统数据采集卡中电压测量电路的零点校正和满刻度校正是用滑动变阻器来实现的,设计了一种新的采用D/A转换芯片、存储器和集成运算放大器的电路,代替了传统的滑动变阻器校正方法,实现了自动校正,提高了调整精度。

采用新的校正电路的另一个优点是可以采用各种非线性校准技术,对电压测量电路的非线性进行自动校准。

关键词:ISA总线;数据采集;自动校正中图分类号:TP18 文献标识码:ADesign and application of the data acquisition card based on ISA busHe XiaoLiang1 Li Aihua1 Wang Fansheng2(1.t he Second Artillery Engineering College,Xiπan710025;2.t he6916t h Plant of PL A,Langfang065000)Abstract:This paper presents the hardware circuit and software design of data acquisition card based on ISA ing the D/A convert chip,memorizer and integrated OP,the new circuit is designed instead of the traditional emendation with slip rheostat.The result shows that this design can achieve the auto2emendation with high precision,and auto2 calibrate the nonlinear with calibration of nonlinear technology in the voltage measurement circuit.K eyw ords:ISA bus;data acquisition;auto calibrating0 引 言目前,工业系统总线具有代表性的有ISA总线、PXI 总线和PCI总线,其中ISA总线因其产生最早、应用接口简单仍在许多对传输速度要求不是很高的场合被使用。

信时都需要在总线上实现启动数据传输状态和停止数据传输状态,数据传输时序为最高位在前。

2.设置状态寄存器时应设置为连接转换模式且Tout输出极性为高电平。

3.写EEPROM通常需要10ms的时间,所以在每一次写寄存器操作后都需要等待10ms再进行下一次写操作。

4.由于SDA,SCL为漏极开路I/O,因此一定要有上拉电阻。

参考文献1Dallas semiconductor data book and CD-ROM,19982何立民.I IC总线应用系统设计.北京航空航天大学出版社,19953龚福民.I IC串行总线及其软件实现.电子技术应用, 1998,6器件应用PCI9052在ISA与PCI总线接口中的应用北京理工大学(北京100081)王宝全周国勇军械工程学院(石家庄050003)周忠来杜恩祥摘要PCI9052是PLX公司推出的PCI总线接口芯片,能够实现ISA总线与PCI总线的无缝连接,可方便地将原有的ISA插卡移植到PCI总线。

文中主要介绍了该芯片的ISA接口模式,并给出了一个实际应用PCI9052的系统。

关键词PCI总线ISA总线PCI9052PCI总线是近年来在工作站和个人微机中得到广泛使用的一种局部总线规范。

PCI总线可提供32位或64位数据宽度。

在32位数据宽度下,可提供最大132M B/s的数据传输率。

随着计算机技术的发展,对高速、高性能板卡的需求将会越来越大,微机中低性能的ISA总线必将被淘汰。

因此,只有符合PCI标准的板卡,才能适应未来的需要。

因为ISA总线已经得到了广泛的应用,ISA插卡大量存在。

当设计一款新的PCI插卡时,如果能够利用已有的同类ISA插卡,将ISA插卡移植到PCI,必将大大缩短开发周期,提高开发效率,节约开发成本。

1PC I9052的ISA接口模式1.1基本特点PLX公司生产的PCI9052是一种功能强、使用灵活的PCI总线控制器专用芯片,该芯片符合PCI 局部总线规范2.1版,可作为PCI总线目标设备(slave),实现基本的传送要求。

采用复杂可编程逻辑器件与ISA总线相结合实现数据采集系统设计数据采集是工业测量和控制系统中的重要部分。

它是测控现场的模拟信号源与上位机之间的接口,其任务是采集现场连续变化的被测信号。

系统应将所采集的模拟数据信号尽可能真实、不失真地显示给控制人员。

随着计算机技术和EDA技术的发展,由于复杂可编程逻辑器件(CPLD)具有高集成度、小体积、低成本、低功耗以及高稳定性等诸多优点而广泛使用到诸如传统工业控制等各个领域。

基于ISA的接口电路,其布线要求远没有PCI或USB接口板高。

由于它能够提供16位I/O操作,对I/O的直接读写可以完全不考虑复杂的驱动程序和应用程序,因而在ISA 总线上开发接口电路目前仍是首先考虑的方法。

因此,这里提出一种基于CPLD和ISA总线的数据采集系统设计。

1 系统硬件设计数据采集系统的硬件电路主要包括:CPLD逻辑控制电路、8254定时器电路、A/D转换电路。

该系统硬件设计框图如图1所示。

1.1 CPLD逻辑控制电路该系统使用XC9572作为主控器件。

XC9572是一款高性能可编程逻辑器件,内含4个36 v 18功能模块,具有l 600个可用系统门。

ISA总线上的地址、控制指令和数据被送进CPLD,经处理后送到相应电路中。

由A/D转换电路得到的数据也返回到CPLD进行处理,并经ISA总线送至计算机中。

图2为数据采集系统的逻辑控制电路,Ul是数据缓冲器74HC245,由lSA总线的读/写信号(IOR/IOW)和板卡选择信号(BSEL)决定数据的流向。

比较器74LS688和XFl组成板卡选择信号发生电路。

通过在XFl上的跳线可确定采集系统板的基地址。

该系统基地址设置为280H。

ISA总线上的读写信号,经缓冲器的数据信号(LADO~LAD7),地址信号(A0~A3)均与。

ISA总线ISA总线接口ISA总线又称AT总线,是在PC/AT微机上所配备的扩展系统总线。

PC/AT的扩展总线系统设计的最大速度为...(Industry Standard Architecture),即ISA总线标准。

EISA总线是由COMPAQ等兼容机厂商联合于1988年9月推出的一种与IBM的MCA总线抗衡的增强型总线。

EISA总线是对ISA总线的扩展,除了保留符合ISA标准的98个引脚外,又增加了90个引脚,这90个引脚包括16条数据线、27条地址线、12条控制线、26条电源线和地线、5条保留线和4条系统制造商专用线。

EISA总线本质上是32位的ISA总线,插槽与所有ISA卡完全兼容。

与MCA类似的是,它也可以允许通过软件来配置EISA卡PCI总线接口PCI总线的英文全称为Peripheral Component Interconnect。

即外部设备互联总线,是于1993年推出的PC局部总线标准。

PCI总线的主要特点是传输速度高,目前可实现66M 的工作频率,在64位总线宽度下可达到突发(Burst)传输速率533MB/s。

可以满足大吞吐量的外设的需求。

VESA(video electronics standard association)总线标准是1992年由60家附件卡制造商联合推出的一种局部总线,简称为VL(VESA local bus)总线。

它的推出为微机系统总线体系结构的革新奠定了基础。

VESA总线主要目的是用于视频插卡,以提高视频性能。

VESA总线系统考虑到CPU与主存和Cache 的直接相连,通常把这部分总线称为CPU总线或主总线,其他设备通过VL总线与CPU总线相连,所以VL总线被称为局部总线。

并行外部设备总线SCSI第6章系统总线接口本章介绍了微机主板的各种标准系统总线和通用,专用接口的技术规格特点,也介绍了它们的使用方法等. 6.1 主板上的系统总线6.2 系统I/O总线的标准6.3 系统设备接口退出6.1 主板上的系统总线6.1.1 总线原理主板上的系统总线是传输数据的通道,就物理特性而言就是一些并行的印刷电路导线,通常根据传送信号的不同将它们分别称为地址(address bus),数据(data bus)和控制(Control bus)三大总线.在数字电路中,逻辑信号1,0是采用电平的高低来表示的,假如高电平表示1,低电平就表示0,由此抽象为二进制数的1和0,并以数位二进制数组成各种代码,来表示各种信息,如用7位二进制数的ASCII码表示英文字符.系统处理各种信息,实际上就是处理一组组二进制数,进一步说,就是在总线上不断传送高,低电平信号.由于元器件性能所限,电路的工作速度也是有限的,即不可能在一秒钟内开关任意多次.我们把系统总线电路每秒钟电平转换的最高次数,称为总线频率f,单位为MHz.频率f的倒数1/f称为总线时钟周期.6.1.2 总线分类总线大致可以分为四类:1.片内总线片内总线也称为CPU总线.它位于CPU处理器内部,是CPU内部各功能单元之间的连线,片内总线通过CPU 的引脚延伸到外部与系统相连.2.片间总线片间总线也称为局部总线(Local BUS).它是主板上CPU与其它一些部件间直接连接的总线.3.系统总线:系统总线也称为系统输入输出总线(System I/O Bus).它是系统各个部件连接的主要通道,它还具有不同标准的总线扩展插槽对外部开放,以便各种系统功能扩展卡插入相应的总线插槽与系统连接.4.外部总线外部总线也称为通信总线.它是电脑与电脑之间的数据通信的连线,如网络线,电话线等.外部总线通常是借用其它电子工业已有的标准,如RS-232C,IE1364标准等.6.1.3 总线构成这里主要介绍的是系统总线,即主板的系统I/O总线和总线扩展插槽.系统I/O总线是数据总线,地址总线和控制总线的总称.数据总线传送的是数据信号,可双向传送.它的线数即总线宽度取决于系统采用的CPU的字长指标.系统总线的宽度是指其数据线的位数.地址总线传送的是内存(或I/O接口)的地址信号,单向传送.它的线数与系统采用的CPU的地址线宽度一致,它决定了CPU直接寻址的内存容量.控制总线传送的是CPU和其它控制芯片发出的各种控制信号,如:读/写周期W/R,指令/代码传送D/C,存储器或IO口访问M/IO和系统复位Reset等.系统中的各个局部电路均需通过这三大总线互相连接,实现了全系统电路的互连.在主板上,系统I/O总线还连接到一些特定的插槽上去对外开放,以便于外部的各种扩展电路板连入系统.这些插座被称为系统I/O总线扩展插槽(System Input/Output Bus Expanded Slot).系统I/O总线的示意图如图6-1.图6-1 微机的系统I/O总线6.2 系统I/O总线的标准PC机主板上采用最多的系统I/O总线标准有ISA,VESA,PCI和AGP等,目前仍保留着ISA,但主要是使用PCI和AGP.主板上的系统总线插槽如图6-2所示.图6-2 主板上的系统I/O总线插槽6.2.1 以往的总线标准1.PC总线和ISA总线PC总线最初用于IBM PC/XT机主板,并在以后的PC/AT和各种286,386兼容机主板上继续使用,目的是便于保留老的PC扩展卡.在后来制定的ISA总线标准中被称为8位ISA总线,目前已被淘汰.PC总线是配合Intel 8088处理器的,因此是8位总线,具有8位数据线和20位地址线,直接内存寻址能力为220即1MB.它的扩展插槽是黑色的,有62个触点,分列两边,每边31个.PC总线扩展插槽的引脚配置如图6-3所示.图6-3 PC总线扩展插槽的引脚配置ISA总线标准来源于IBM PC/AT机主板使用的系统I/O总线和扩展插槽,所以也称为AT总线(AT Bus),87年成为国际通用总线标准ISA(Industry Standard Architecture)即工业标准结构总线.ISA是针对Intel 80286 CPU设计的,因此是16位总线,数据线16位和地址线24位,即直接内存寻址为16MB.它的工作时钟是8.33MHz,数据传输率为8.33MB/S.16位ISA总线是在8位ISA总线插槽的沿伸方向上增加了一个双排共36触点的插槽,新增的插槽引脚把8位数据和20位地址扩展成16位数据线和24位地址线.因此16位ISA插槽同8位ISA插槽保持了互换性,即16位ISA槽也可以使用8位ISA卡.低速ISA标准与高速的32位386,486和Pentium CPU形成了一定的矛盾,但为了允许保留使用老的ISA 卡,主板仍保留至少一个ISA插槽.ISA总线扩展插槽的引脚配置如图6-4所示,插槽的触点信号定义如表6-1.图6-4 ISA总线扩展插槽表6-1 ISA总线插槽的信号定义2.MCA和EISA总线这两种总线由于特定的原因,在PC机上很少采用.MCA(Micro Channel Architecture)即微通道结构总线来源于IBM PS/2机,是为32位的Intel 80386 CPU设计的.MCA是32位总线,数据线32位,地址线32位,直接内存寻址为4GB.它工作时钟为33MHz,数据传输率提高到20MB/S.它可以接16个外设.由于MCA技术不开放,且与ISA不兼容,以后在微机上很少使用.EISA(Extend Industry Standard Architecture)即扩展ISA总线,它是Compaq等兼容机厂商为对抗IBM的32位MCA总线和保持对ISA总线的兼容性而推出的.EISA支持386CPU,是32位总线.它的32位地址也可直接寻址4GB内存.EISA的工作时钟与ISA一样是8.33MHz,数据传输率是33MB/S.EISA的插槽外形与ISA一样,但在槽内的底部又增加了一排触点,用以扩充32位数据,32位地址和控制信号等.这样EISA既可用于32位扩展卡,又可兼容老的8位,16位ISA扩展卡.在EISA插槽上,EISA卡可以更深地插入,以便与下一排触点连接,取得32位支持.EISA的结构用当时的工艺技术制做是比较复杂的,因而成本很高,通常用于服务器和工作站.EISA总线扩展插槽的引脚配置如图6-5所示.图6-5 EISA总线扩展插槽3.VESA总线VESA(Video Electronic Standard Association)总线是以视频电子标准协会制定而得名,也叫VL BUS(VESA Local Bus)即VESA局部总线.它是专门为Intel 80486 CPU系统的高速视频信号处理而设计的.VESA是32位高速总线,也允许扩展到64位.它的工作时钟为33MHz,最大允许到66MHz,数据传输率高达133MB/S.VESA是在ISA总线的黑色插槽的延伸方向上增加了一个新的浅色插槽,它有双排共116个触点,单独提供32位数据线和32位地址线.因此32位的VESA总线槽同16位的ISA总线槽保持了互换性,即在VESA 扩展槽上也可以插ISA扩展卡,只是VESA扩展卡比较长.只有使用VL BUS扩展卡才能发挥它的32位高速总线的优势.最典型的VESA显示卡是ET-4000 VGA 和Trident 9440 VL-BUS Graphics Adaptor等.VL BUS还允许在32位插槽上再延长一个50引脚的插槽,从而扩展为64位的VESA总线.32位的VESA 总线扩展插槽的引脚配置如图6-6所示.图6-6 VESA总线扩展插槽6.2.2 目前主流总线标准6.2.2.1 PCI总线PCI(Peripheral Component Interconnect)即外部设备互联总线,顾名思义,它的初衷就是使外设主芯片能快捷地连入系统.PCI是专门为Intel Pentium处理器设计的,它也是一种高性能的PC机局部总线(Local Bus).PCI是32位总线,工作时钟是33MHz,数据传输率为133MB/S.PCI的高速性能使之能支持各种高速设备,特别是3D图形加速卡.目前PCI扩展卡已成为微机高速扩展卡的主流,包括显示卡,声卡,Modem卡,网卡和视频卡等.目前在一些高档机上也有64位PCI总线,工作时钟提高到66MHz,数据传输率可达528MB/S.PCI还有如下优点:1.PCI支持PnP(Plug and Play)即插即用功能.2.PCI总线支持猝发数据传送方式,大大提高了总线的数据传输率.3.PCI支持总线主控和同步操作.4.PCI采用多路复用技术,可以在有限的空间里加大总线宽度,提高总线利用率.5.PCI总线通过局部总线控制器与CPU相连,因此PCI可以不依赖于CPU的主频和种类,接入的PCI设备也不影响CPU.6.主板的芯片组内含PCI桥(PCI Bridage),通过这个缓冲控制器,可以实现6个PCI扩展槽同时工作.PCI 是白色插槽独立结构,与ISA扩展卡不兼容.它的插槽每边62线,共124线.64位的PCI总线扩展槽是在32位PCI插槽上延长,每边增加32线而成.PCI总线插槽分为5V供电电源和3.3V供电电源两种,为避免这两种不同的扩展卡插错,3.3V的插槽的定位挡片Key的位置改设在12,13引脚处.电源为3.3V和5V的32位PCI总线扩展插槽的引脚配置如图6-7所示.插槽的触点信号定义如表6-2.图6-7 5V和3.3V电源的PCI扩展槽的引脚配置6.2.2.2 AGP总线AGP(Accelerate Graphic Port)即加速图形接口,它是Intel专门为Pentium Ⅱ系统的图形控制器设计的系统总线结构,它十分默契地配合着Pentium Ⅱ的高速浮点运算能力和MMX技术,目前几乎垄断了3D 图形加速卡的接口.AGP是32位数据总线,工作时钟是66MHz,数据传输率为264MB/S,是PCI的二倍.第二代增强AGP 2×的工作时钟是133MHz,数据传输率达到532MB/S,是PCI的四倍.目前奔腾III主板已采用了AGP 4×,数据宽度扩展到64位,工作时钟133MHz,数据传输率高达1GB/S.AGP总线将显示卡与主板的芯片组直接相连,进行点对点传输,所以它不是那种通用性的总线,它只用于支持AGP图形加速卡.Intel公司推出了支持AGP的440LX和BX等芯片组.Pentium II CPU,440BX和AGP的系统结构如图6-8.图6-8Pentium Ⅱ,440BX和AGP系统结构AGP加速图形接口在PC图形控制器和系统内存之间提供了高速通道,可使图形控制器直接从主内存执行纹理映射,而不必局限于少量的显示缓存中.AGP还有助于加速从CPU到图形控制器的解码视频流,不需要将预取的纹理缓存到显存中,这使得3D程序运行更快.AGP插槽完全独立于原系统总线,且与以前的图形控制芯片,PCI控制芯片和CPU不兼容.AGP插槽为棕色,124个触点分列两边和上下两排,结构较复杂.AGP扩展插槽的引脚配置如图6-9所示.Intel还推出了一种AGP Pro插槽,目的是解决显示卡的电源供应和散热问题.它比原来的AGP插槽加长,并且要占用与其相邻的PCI插槽.图6-9 AGP扩展插槽6.3 系统设备接口6.3.1 主板上的设备接口主机的重要性前面已经充分说明了,但是作为一个有效的计算机系统,外部设备也是不可或缺的.如果没有最基本的外存设备和输入输出设备,计算机主机系统就无法运行和与用户交互.微型计算机的外部设备主要包括外存设备和输入输出设备(I/O设备),常用的外部存储器有软盘和软盘驱动器,硬盘,光盘和光盘驱动器,磁带和磁带机等,常用的输入设备有键盘,鼠标,扫描仪,麦克风,数码相机,摄像机和光笔等,常用的输出设备有显示器,打印机,功放扬声器和绘图仪等.在安装新硬件时,常常要为其配置I/O口地址(I/O Port Address),端口地址是CPU访问,区别各个不同硬件设备的标志,任何设备占用的I/O口地址都不相同,而一个设备也可能占用几个连续或不连续的I/O口地址.比如声卡就可能占用0220-022FH这16个连续的I/O口地址.如果几个硬件分配了相同的I/O口地址,CPU就无法正确访问它们,这些硬件也就无法正常工作,这种故障叫做I/O口地址冲突.由于外部设备各自的特点,主机与外设间交换的信息载体形式(模拟,数字,电压,电流),数据传送的速率和方式(串行,并行)等都会有所不同,因此必须在它们之间建立多种数据转换和缓冲的界面,这就是各种规格的输入输出接口(Input/Output Interface Port),简称I/O接口.微机采用的通信接口标准有计算机专用的也有电器设备领域通用的,有某一类外设专用的也有不同外部设备通用的.专用接口如硬盘接口IDE,键盘鼠标接口PS/2和显示器接口(VGA口)等.通用I/O通信接口按其数据传送的形式不同可以分为串行接口和并行接口两大类.串行接口是用一条线路将二进制数据按顺序一位位地传送,每个时钟传送一位,至少8个时钟才能传送1字节二进制数据.它的特点是线路简单但速度较慢,适合于慢速远距离的数据传送.例如RS-232C串行接口就用于鼠标器,Modem和终端等.并行接口是用8条线路同时分别传送1字节二进制数据的8位,1个时钟就可以传送1字节二进制数据.它的特点是线路复杂(8条数据线)但速度较快,适合于快速近距离的数据传送.例如通用并行接口就用于打印机,扫描仪等外设.软盘,硬盘和光盘等也都采用专门的并行接口.在早期的PC机上,各个I/O接口都集中做在一块"I/O多功能卡"上,包括1个软盘口,1或2个硬盘口,2个通用串口,1个通用并口和1个游戏棒口,将此卡插入ISA槽便使系统增加了各个接口的功能.到了586机,就把接口的控制芯片集成到主板上,进一步地又把接口控制功能集成到南桥芯片中,把各个接口插座直接做到主板后沿,形成标准ATX主板.这样就简化了结构,提高了接口性能和可靠性,还降低了成本.6.3.2 硬件I/O接口的系统资源1.硬件设备的I/O端口地址CPU与外设之间的访问要通过硬件的I/O接口,相互交换的数据要在I/O接口电路的数据缓冲寄存器中暂存,CPU控制硬件工作方式和速度的命令也要存入I/O接口电路的控制寄存器,这些寄存器统称为I/O 端口.CPU正是通过访问硬件设备的各个I/O端口来控制该设备工作的,因此所有设备的I/O端口寄存器都必须统一编码,并且不能重复.系统会自动(或用户手工)为每个设备的各个端口分配相应的I/O口地址.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机从0000-04D1H段的I/O口地址的硬件占用情况:x0000-xFFFF……(也可以见:控制面板,系统,设备管理,计算机属性) 要求熟悉几个基本硬件的I/O口地址:串口1(COM1)3F8-3FF,串口2(COM2)2F8-2FF,并口1(LPT1)即打印机378-37B,声卡的游戏棒,声音SB16,MIDI(MPU401)和声音WSS,显示卡,标准IDE硬盘控制器170-177和370-377,标准软盘控制器3F0-3F5.2.硬件设备的IRQ号一些硬件设备除了占用I/O端口地址外,还具有向CPU申请硬件中断的能力,因此还占有中断请求(IRQ)号的系统资源.PC系统的IRQ中断号共有16个(IRQ 0-15),可以分配给16个设备使用,每个设备单独占用一个IRQ号.当某个设备向CPU发出中断申请,CPU可以根据其IRQ号加以响应,运行相应的中断处理程序.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机的16个IRQ中断申请号的分配情况:IRQ0-15(也可以见:控制面板,系统,设备管理,计算机属性)3.硬件设备的DMA通道号DMA(Direct Memory Access)是某些数据量大的硬件设备与主机快速交换数据的特殊工作方式,如软盘,硬盘,声卡等.在DMA控制器的控制下,设备与内存直接交换数据,并不占用CPU时间,CPU再与内存交换数据.因此DMA方式比CPU直接访问速度较慢的设备的方式要高效得多.PC系统的DMA通道共有8个(DMA0-7),DMA通道号不一定被一个设备独占,几个硬件设备可以共用一个DMA通道,只要它们不是同时使用它.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机的8个DMA通道号的分配情况:DMA0-7(也可以见:控制面板,系统,设备管理,计算机属性)6.3.3 标准串行接口和并行接口1.串行接口PC机通常配置有两个RS-232C异步串行通信接口和一个并行接口.串口一的逻辑名为COM1/COM3,9针D型插座,通常用来接鼠标.串口二的逻辑名为COM2/COM4,25针D型插座,连接Modem,数码相机和磁卡机等外设.串行接口的9针和25针插座针孔配置见图6-10,各针孔的信号定义如表6-3.图6-10 串口插座针孔配置2.并行接口标准并行接口的逻辑名为LPT1,也叫打印机接口(Printer),是一个25针的D型插座,用来连接打印机和扫描仪等外设.并行接口插座针孔配置见图6-11.各针孔的信号定义如表6-4.图6-11 并口的引脚配置在BIOS Setup中,并行接口有Normal,EPP和ECP三种模式供选择.Normal接口是一种低速的并口模式,也叫SPP(Singl Parallel Port)即单向并口,它的数据传输率为40Kb/S,适合将结果输出到普通打印机上,所有并口外设都支持此种模式.EPP接口(Enhanced Parallel Port)即增强并行接口,在外部设备间进行双向通信,数据传输率在400Kb/S 以上.目前多数打印机和扫描仪都支持EPP模式.ECP接口(Extended Capabilities Port)即扩展并行接口,具有和EPP一样高的速率和双向通信能力,但在多任务环境下,它能使用直接存储器访问方式(DMA),所需缓冲区也不大.但ECP模式容易引起冲突.许多新型的并行设备,如激光打印机,扫描仪等要求EPP,ECP或EPP+ECP模式.因此在CMOS Setup中应根据设备的要求适当选择并口模式.6.3.4 新型串口USBUSB(Universal Serial Bus)是通用串行总线,是一种新型高速串行接口.USB仅用一个4针方形标准插座,采用菊花链的形式就可以把许多外设逐一连接起来,并且不会损失信号带宽.USB的推出使得接口性能大大提高,主机与外设的连接变得非常简单和有效,它正在逐步取代PC机上原有的串行,并行等各种接口.目前USB能支持的外设有扫描仪,数码相机,打印机,显示器,键盘,鼠标等.要使用USB设备,就要求主板和操作系统都支持USB接口.Pentium以上的主板一般都采用了支持USB 的芯片组和BIOS程序,主板上也都有USB插座.Windows 97,98和NT4.0等都支持USB接口.如果使用早期的Windows 95和NT 3.0等,就需要安装USB接口驱动程序.最后还需在安装了USB设备后安装相应的设备驱动程序.目前市场上有USB扩展卡,将其插到PCI插槽上,引导Windows 98后就可以方便地为系统增加两个USB.Pentium MMX主板上一般有一个10针的双USB接口,需要用USB转接电缆将两个USB插座引出. 与以往的接口相比,USB有许多优点:/doc/2718735481.html,B的12Mb/s的数据传输率比以前的串口快100倍,比并口快10倍,即使多个设备接在一个USB口上,也能获得满意的操作速度./doc/2718735481.html,B接口允许带电"热插拔"设备,无须关机.而且USB接口控制器可以立即感知拔去或插上的设备,直接驱动,无须重新启动系统.因此只有USB设备才算是真正意义的即插即用设备./doc/2718735481.html,B接口设备可采用"级联"方式连接,即每个接入设备也提供一个USB插座供下一个设备连接.一个USB控制器可以支持最多127个设备,每个设备的连接电缆可长达5米./doc/2718735481.html,B接口可以向外部提供+5V,0.5A电源,这使得一些小功率的外设可以省去自身的电源电路./doc/2718735481.html,B接口简单可靠,4个连线分别是:+5V电源,信号1(-),信号2(+)和接地GND.6.3.5 新型串口IEEE 1394IEEE 1349是一种新型高效的串行接口,它与USB有不少相似之处.它使用六芯电缆,包括两对双绞线信号线和两根电源线.它的最大传输电流可达1.5A,传输数据的直流电压可以在8到40V之间变换.1394与USB一样,也可以"热插拔",是真正的即插即用接口.它也向外设提供电源,也采用串行链接方式,可以连接多台设备.1394与USB的主要差别在于它无须Hub就可以连接63台设备.1394还规定了两种传输模式,一种是传输速率为12.5,25或50Mb/S 的底版模式(Backplane Mode),另一种是传输速率为100,200或400Mb/S的电缆模式(Cable Mode).在400Mb/S时只要用50%的带宽就可以支持高质量的数字化视频信息流.IEEE1394的传输速率远高于USB,它支持的产品范围也涵盖了USB,所以IEEE1394应该比USB更具前景.但是由于IEEE1394的技术要求和生产成本较高,目前价格昂贵,还很少被家用和商用PC采用.习题1.微机系统有哪几类总线,总线的三个组成部分是什么2.掌握ISA,VESA,PCI和AGP总线的规格和特点.3.掌握串口,并口的规格,特点和系统资源.4.掌握USB接口的规格和特点.。

16位,12通道,500K,同步,数据采集卡YG-EB1309用户手册1. 概述YG-EB1309高精度数据采集卡适用于提供了PC104 总线的嵌入式微机。

其操作系统可选用经典的MS-DOS、Linux或目前流行的 Windows 系列等多种操作系统。

YG-EB1309高精度模入接口卡安装使用简便、功能齐全。

其A/D 转换启动方式可以选用程控频率触发、程控单步触发、以及外部时钟同步触发等多种方式。

A/D转换后的数据结果通过先进先出存储器(FIFO)缓存后由PC104总线读出。

为方便用户,本卡还提供了符合TTL电平的8路数字量输入和24路数字量输出信号通道。

2. 主要技术参数2.1模入部分2.1.1输入通道数:12路同步2.1.2 输入信号范围:±2.5V;±5V;±6V;±10V;±12V;2.1.3 输入阻抗:≥10MΩ2.1.4 输入通道选择方式:12通道同步2.1.5 A/D转换分辩率:16位2.1.6 A/D最高转换速率:500KHz2.1.7 A/D采样程控频率:1KHz/5KHz/10KHz/50KHz/100KHz/200KHz/500KHz/外部时钟2.1.8 A/D启动方式:程控频率触发/程控单步触发/外部TTL信号触发2.1.10 FIFO存储器容量:20K×16bit(全满)/10K×16bit(半满)2.1.11 数据读取识别方式:FIFO半满查询/FIFO非空查询/FIFO半满中断2.1.12 系统综合误差:≤0.02% F.S2.2 开关量部分2.2.1 输入路数:8路TTL电平2.2.2 输出路数:24路TTL电平2.3 电源部分2.3.1 支持外部电源输入或PC104接口取电。

2.3.2 功率:+5V(±10%)≤500mA2.4环境要求:工作温度:10℃~40℃相对湿度: 40%~80%存贮温度:-55℃~+85℃2.5 外型尺寸:长×高=90mm×96mm3. 工作原理YG-EB1309高精度模入接口卡主要由高速高精度放大电路、高精度模数转换电路、先进先出(FIFO)缓冲存储器电路、开关量输入输出电路和接口控制逻辑电路等部分组成。

PCI总线接口技术及其在高速数据采集系统中的应用数据采集是数字信号处理中非常重要的环节。

对于不同的任务,数据采集要达到的技术指标也不相同。

对于瞬态信号,雷达信号和图像处理都需要几MB/s 甚至几十MB/s 的超高速采集速率。

目前用于PC 机的数据采集卡大部分是基于ISA 总线的,这种结构的最大缺点是传输速率太低,不能实现数据的实现高速传输。

PCI 总线推出后,以其突出的性能备受计算机和通信业界的青睐,将取代以往的总线, 成为高档机及高性能工作站外部件的基石。

PCI 作为局部总线,一边与处理器和存储器总线接口;另一边为外设扩展提供了高速通道。

33MHz、32 位的PCI 总线可以实现132MB/s 的数据传输速率;64 位的PCI 总线性能加倍。

开发以PCI 总线为基础的数据采集设备是技术发展的必然要求。

在实际工作中,利用PCI 总线将采集数据直接传到系统内存,可有效解决数据的实时传输和存储,为信号的实时处理提供方便。

1 数据采集系统的结构与功能本数据采集系统应用于雷达视频回波信号的处理。

信号由两路正交视频回波信号组成,故采用双通道。

采集指标:2 路采集信号,采样率为40M 个样本, A/D 采样字长是10 位。

每路数字信号字长取16 位,两路合成路共32 位,将32 位数据分别传入系统内存的不同区域,以便后续处理。

系统设计以PCI 总线控制器为基础,通过DMA 方式分别将32 位数据传输系统内存的不同区域。

主要功能模块有:PCI 总线控制器、双口SRAM、采集控制芯片EPLD、A/D 部分。

系统框图如图1 所示。

2 PCI 总线控制器的实现PCI 总线是一个地址/数据、命令/字节选择信号复用的总线。

它采用主从。

isa卡设计方案ISA卡设计方案ISA(Industry Standard Architecture)卡是一种用于扩展计算机功能的插槽卡。

在早期的个人计算机中,ISA卡是一种常见的插槽接口标准,用于连接各种外部设备、接口卡和扩展板。

本文将介绍一种基于ISA卡的设计方案。

设计目标:1. 提供一个方便的接口,使用户可以方便地插入和移除ISA卡。

2. 支持多种类型的ISA卡,如网络卡、声卡、输入输出接口卡等。

3. 提供高速数据传输和稳定的信号质量。

设计要点:1. 插槽设计:1) 使用标准的ISA插槽设计,以保持与已有设备的兼容性。

2) 采用弹簧插座设计,使用户可以方便地插入和移除卡片。

3) 插槽内部使用金属屏蔽,以提供良好的EMI屏蔽效果。

4) 插槽底部设计通孔,以便于散热和防止静电积累。

2. 电路设计:1) 采用高质量的电子元器件,以确保电路的稳定性和可靠性。

2) 使用专业的布线技术,以保证信号传输的稳定性和可靠性。

3) 使用高速的总线,以支持高速数据传输。

3. 驱动程序:1) 提供通用的驱动程序接口,以支持多种类型的ISA卡。

2) 开发易于使用和稳定性良好的驱动程序,以提供良好的用户体验。

3) 提供兼容性测试工具,以确保ISA卡和驱动程序的兼容性。

总结:以上是一种基于ISA卡的设计方案,旨在提供一个方便的接口,支持多种类型的ISA卡,并提供高速数据传输和稳定的信号质量。

通过合理的插槽设计、高质量的电路设计和稳定性良好的驱动程序,我们可以实现一个功能强大、易于使用和稳定可靠的ISA卡系统。

ISA总线与高速数据采集卡的接口技术

作者:王会霞, 刘教民, 王晓宏, 孙壮志

作者单位:王会霞,王晓宏,孙壮志(工业大学(天津)), 刘教民(科技大学(石家庄))

被引用次数:2次

1.陈太洪基于ISA总线的数据采集板设计[期刊论文]-工业控制计算机2007,20(7)

2.瞿英.王海竹.Qu Ying.Wang Haizhu ISA总线与高速数据采集卡的接口技术[期刊论文]-江苏电器2003(6)

3.詹恩奇.肖虎卡尔逊传感器数据采集模块的设计与实现[期刊论文]-仪表技术与传感器2001(9)

4.柴玉新.梁鸿一种基于ISA总线的数据采集处理系统[会议论文]-2005

5.朱然刚.叶春逢.钟子发.ZHU Ran-gang.YE Chun-feng.ZHONG Zi-fa基于VHDL实现逻辑控制的高速数据采集系统[期刊论文]-微处理机2005,26(3)

6.贺小亮.李艾华.王帆胜.He XiaoLiang.Li Aihua.Wang Fansheng基于

ISA总线的数据采集卡的设计及应用[期刊论文]-电子测量技术2008,31(6)

7.程学庆.高品贤ISA总线多路数据采集卡研制[期刊论文]-实用测试技术2002,28(6)

8.赵小英.王会霞.郭鸿涌应用ISA总线实现高速数据采集[期刊论文]-河北科技大学学报2001,22(4)

9.李涛.张承学.胡志坚基于ISA总线的高速同步数据采集系统设计[期刊论文]-电子技术应用2002,28(4)

10.蒋志峰.蒋伟峰.刘济林.JIANG Zhi-feng.JIANG Wei-feng.LIU Ji-lin基于ISA总线接口电路的设计及研究[期刊论文]-实验室研究与探索2000,19(1)

1.顾光武.赵世平.廖俊必基于ISA总线的活塞自动检测及分选机[期刊论文]-计量技术 2005(4)

2.顾光武.赵世平.廖俊必基于ISA总线的活塞自动检测及分选机[期刊论文]-工具技术 2005(1)

本文链接:/Conference_104182.aspx。