数字逻辑技术第七章

- 格式:doc

- 大小:15.00 KB

- 文档页数:2

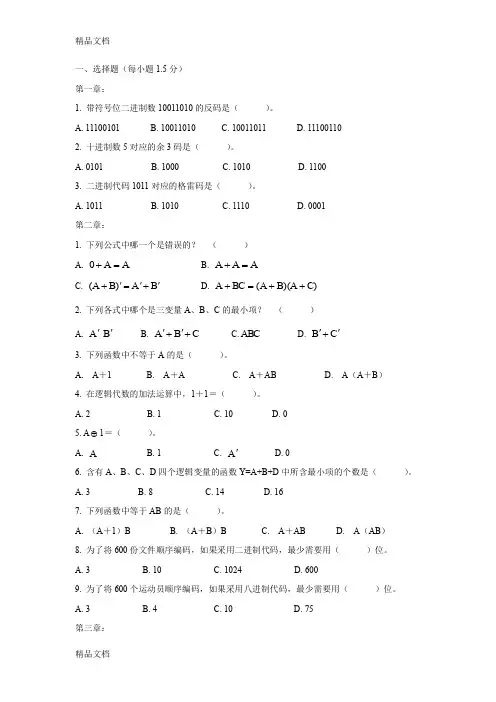

一、选择题(每小题1.5分)第一章:1. 带符号位二进制数10011010的反码是( )。

A. 11100101B. 10011010C. 10011011D. 111001102. 十进制数5对应的余3码是( )。

A. 0101B. 1000C. 1010D. 11003. 二进制代码1011对应的格雷码是( )。

A. 1011B. 1010C. 1110D. 0001第二章:1. 下列公式中哪一个是错误的? ( )A. A A 0=+B. A A A =+C. B A )B A ('+'='+D. )C A )(B A (BC A ++=+2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( )A. B A ''B. C B A +'+'C.ABCD. C B '+'3. 下列函数中不等于A 的是( )。

A. A +1B. A +AC. A +ABD. A (A +B )4. 在逻辑代数的加法运算中,1+1=( )。

A. 2B. 1C. 10D. 05. A ⊕1=( )。

A. AB. 1C. A 'D. 06. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是()。

A. 3 B. 8 C. 14 D. 167. 下列函数中等于AB 的是( )。

A. (A +1)BB. (A +B )BC. A +ABD. A (AB )8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。

A. 3B. 10C. 1024D. 6009. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。

A. 3B. 4C. 10D. 75第三章:1. 采用漏极开路输出门电路(OD 门)主要解决了( )。

A. CMOS 门不能相“与”的问题B. CMOS 门的输出端不能“线与”的问题C. CMOS 门的输出端不能相“或”的问题2. 下列哪个特点不属于CMOS 传输门?( )A. CMOS 传输门属于双向器件。

《数字逻辑与数字系统》教学大纲一、使用说明(一)课程性质《数字逻辑与数字系统》是计算机科学与技术专业的一门专业基础课。

(二)教学目的通过本课程的学习,可以使学生熟悉数制与编码,逻辑函数及其化简,集成逻辑部件,中大规模集成组合逻辑构件。

掌握组合逻辑电路分析和设计,同步时序逻辑电路分析和设计,异步时序逻辑电路分析和设计;中规模集成时序逻辑电路分析和设计。

了解可编程逻辑器件,数字系统设计,数字系统的基本算法与逻辑电路实现,VHDL语言描述数字系统。

为专业课的学习打下坚实的基础。

(三)教学时数本课程理论部分总授课时数为68课时。

(四)教学方法理论联系实际,课堂讲授。

(五)面向专业计算机科学与技术专业。

二、教学内容第一章数制与编码(一)教学目的与要求通过本章学习使学生掌握数制的表示及转换,二进制数的算术运算,二进制码,原码、补码、反码。

(二)教学内容模拟信号,数字信号,数制的表示及转换,二进制数的算术运算,二进制码,原码、补码、反码。

重点与难点:数制,二进制码,逻辑运算,逻辑代数的基本定律和规则,逻辑函数的化简。

第一节进位计数制1、十进制数的表示2、二进制数的表示3、其它进制数的表示第二节数制转换1、二进制数与十进制数的转换2、二进制数与八进制数、十六进制数的转换第三节带符号数的代码表示1、真值与机器数2、原码3、反码4、补码5、机器数的加、减运算6、十进制数的补数第四节码制和字符的代码表示1、码制2、可靠性编码3、字符代码(三)教学方法与形式课堂讲授。

(四)教学时数2课时。

第二章逻辑代数与逻辑函数(一)教学目的与要求通过本章学习使学生掌握逻辑代数的基本运算,逻辑代数的基本公式、定理及规则。

逻辑函数表达式的形式与转换方法,逻辑函数的代数法及卡诺图法化简。

(二)教学内容逻辑代数的基本运算、基本公式、定理及规则。

逻辑函数表达式的形式与转换方法,逻辑函数的代数法及卡诺图法化简。

重点与难点:逻辑代数的公式、定理及规则。

《数字逻辑设计及应用》课程教学大纲课程编号:53000540适用专业:电子信息、电气工程、自动控制及其他应用数字技术的相关专业学时数:64 学分数:4 开课学期:第4学期先修课程:《大学物理》、《软件技术基础》、《电路分析基础》、《模拟电路基础》执笔者:姜书艳编写日期:2011.9 审核人(教学副院长):一、课程性质和目标授课对象:全日制大学本科二年级课程类别:学科基础课教学目标(本课程对实现培养目标的作用;学生通过学习该课程后,在思想、知识、能力和素质等方面应达到的目标):“数字逻辑设计及应用”课程是信息技术类专业所共有的一门重要学科基础课程,同时也是一门重要工程技术课程,是研究数字系统硬件设计的入门课程。

在本课程中,将介绍数字逻辑电路的分析设计方法和基本的系统设计思想;培养同学综合运用知识分析解决问题的能力和在工程性设计方面的基本素养。

通过实验和课外上机实验的方式,使同学深入了解和掌握数字逻辑电路的分析设计方法和电路的运用过程。

通过本课程的学习,使学生掌握数字逻辑电路的基本理论、基本分析和设计方法,为学习后续课程准备必要的数字电路知识。

本课程在培养学生严肃认真的科学作风和逻辑思维能力、分析设计能力、归纳总结能力等方面起重要作用。

二、课程内容安排和要求(一)教学内容、要求及教学方法1. 课堂理论教学(64学时)第一章引论(2学时)了解:数字电路的发展及其在信息技术领域中的地位;数字信号与模拟信号之间的关系及数字信号的特点;数字系统输入输出特性及其逻辑特点,数字逻辑电路的主要内容。

第二章信息的数字表达(4学时)掌握:十进制、二进制、八进制和十六进制数的表示方法以及它们之间的相互转换、二进制数的运算;符号数的表达:符号-数值码(Signed-Magnitude System、原码),二进制补码(two's complement,补码)、二进制反码(ones' complement, 反码)表示以及它们之间的相互转换;符号数的运算;溢出的概念。

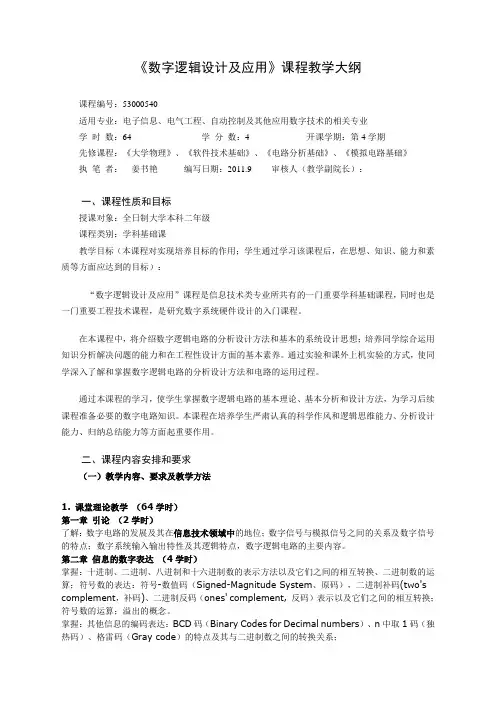

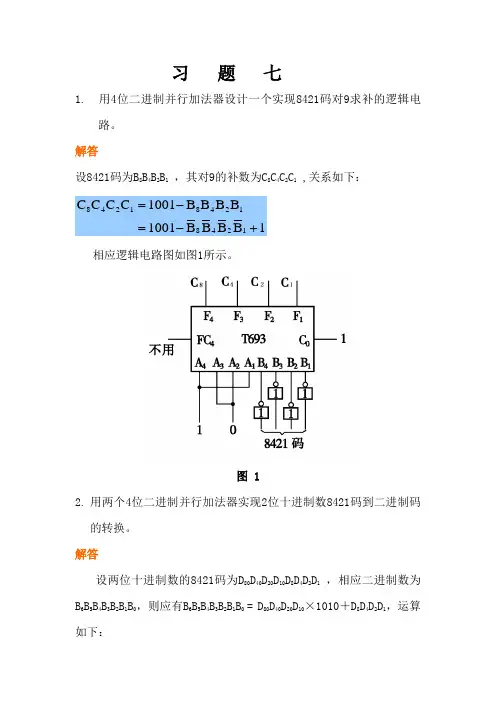

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。

第七章 存储器和可编程器件7—1 填空1.半导体存储器按功能分有_RAM __和__ROM _两种。

2.ROM 主要由__存储矩阵____和__地址译码器____和输出缓冲器三部分组成,按照工作方式的不同进行分类,ROM 可分为_MROM __、_PROM __和_EPROM __三种。

3.某EPROM 有位8数据线,13位地址线,则其存储容量为_8K ×8b __。

4.随机存储器按照存储原理可以分为_____SRAM ______和___DRAM ________,其中______DRAM_____由于具有“漏电”特性,因此需要进行_____刷新______操作。

7—2 图7.2是16⨯4位ROM ,3A 2A 1A 0A 为地址输入,3D 2D 1D 0D 为数据输出,试分别写出3D 2D 1D 0D 的逻辑表达∑=)15,10,6,2(3m D ∑=)15,12,11,8,7,4,3(2m D ∑=)12,9,6,3,0(1m D ∑=)14,13,12,11,8,7,6,5,2,0(0m D7—3 由一个三位二进制加法计数器和一个ROM 构成的电路如图7.3(a )所式。

1. 写出输出1F 2F 3F 的表达式;2. 画出CP 作用下1F 2F 3F 的波形(计数器的初态为“0”)。

答:∑=)5,4,2,1(1m F ∑=)6,5,3(2m F∑=)6,5,4,2,1,0(3m F2、波形如图所示。

注意:F 为组合逻辑。

A A A A 3210图7.2123F F F 图7.3(a )123F F F 图7.3(a )图7.3(b )W 7第8章 脉冲波形的产生及整形8-1 图8.1(a )为由555定时器和D 触发器构成的电路,请问: 1. 555定时器构成的是哪种脉冲电路? 2. 在图(b )中画出C U O1U O2U 的波形; 3. 计算O1U O2U 的频率;4. 如果在555定时器的第5脚接入4V 的电压源,则O1U 的频率将为多少?答:1、该电路为多谐振荡器。

第七章半导体存储器习题

一、选择题

1.一个容量为1K×8的存储器有个存储单元。

A.8 B.8K C.8000 D.8192 2.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A.2 B.4 C.8 D.32

3.寻址容量为16K×8的RAM需要根地址线。

A.4 B.8 C.14 D.16 E.16K 4.若RAM的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有条。

A.8 B.16 C.32 D.256 5.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

A.8×3 B.8K×8 C.256×8 D. 256×256 6.采用对称双地址结构寻址的1024×1的存储矩阵有。

A.10行10列 B.5行5列 C.32行32列 D.1024行1024列 7.随机存取存储器具有功能。

A.读/写

B.无读/写

C.只读

D.只写

8.欲将容量为128×1的RAM扩展为1024×8,则需要控制各片选端的辅助译码器的输出端数为。

A.1

B.2

C.3

D.8

9.欲将容量为256×1的RAM扩展为1024×8,则需要控制各片选端的辅助

译码器的输入端数为。

A.4

B.2

C.3

D.8

10.只读存储器ROM在运行时具有功能。

A.读/无写

B.无读/写

C.读/写

D.无读/无写 11.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容。

A.全部改变 B.全部为0 C.不可预料 D.保持不变 12.随机存取存储器RAM中的内容,当电源断掉后又接通,存储器中的内容。

A.全部改变

B.全部为1

C.不确定

D.保持不变 13.一个容量为512×1的静态RAM具有。

A.地址线9根,数据线1根

B.地址线1根,数据线9根

C.地址线512根,数据线9根

D.地址线9根,数据线512根 14.用若干RAM实现位扩展时,其方法是将相应地并联在一起。

A.地址线 B.数据线 C.片选信号线 D.读/写线 15.PROM的与陈列(地址译码器)是。

A.全译码可编程阵列

B. 全译码不可编程阵列

C.非全译码可编程阵列

D.非全译码不可编程阵列

二、判断题(正确打√,错误的打×)

1.实际中,常以字数和位数的乘积表示存储容量。

()

2. RAM由若干位存储单元组成,每个存储单元可存放一位二进制信息。

()

3.动态随机存取存储器需要不断地刷新,以防止电容上存储的信息丢失。

()

4.用2片容量为16K×8的RAM构成容量为32K×8的RAM是位扩展。

()5.所有的半导体存储器在运行时都具有读和写的功能。

()6. ROM和RAM中存入的信息在

电源断掉后都不会丢失。

()7. RAM中的信息,当电源断掉后又接通,则原存的信息不会改变。

()8.存储器字数的扩展可以利用外加译码器控制数个芯片的片选输入端来实现。

()9. PROM的或阵列(存储矩阵)是可编程阵列。

()

10. ROM的每个与项(地址译码器的输出)都一定是最小项。

()

三、填空题

1.存储器的和是反映系统性能的两个重要指标。

2. ROM用于存储固定数据信息,一般由、和三部分组成。

3. 随机读写存储器不同于ROM,它不但能读出所存信息,而且能够写入信

息。

根据存储单元的工作原理,可分为和两种 4. PROM和ROM的区别在于它的或阵列是的。