数字逻辑第七章

- 格式:ppt

- 大小:1.22 MB

- 文档页数:96

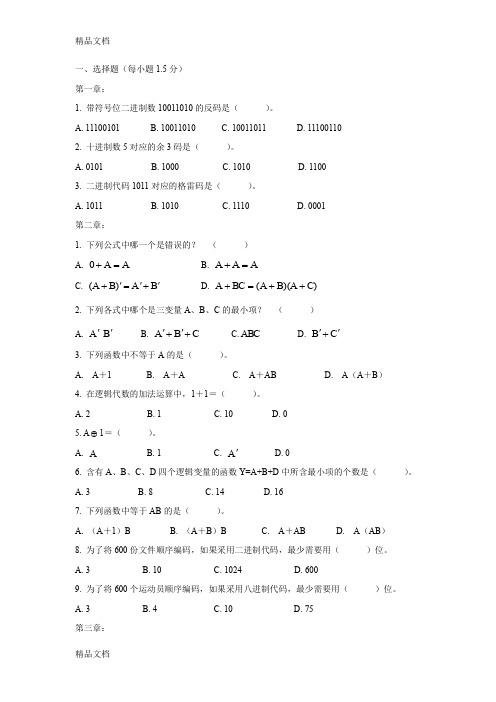

一、选择题(每小题1.5分)第一章:1. 带符号位二进制数10011010的反码是( )。

A. 11100101B. 10011010C. 10011011D. 111001102. 十进制数5对应的余3码是( )。

A. 0101B. 1000C. 1010D. 11003. 二进制代码1011对应的格雷码是( )。

A. 1011B. 1010C. 1110D. 0001第二章:1. 下列公式中哪一个是错误的? ( )A. A A 0=+B. A A A =+C. B A )B A ('+'='+D. )C A )(B A (BC A ++=+2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( )A. B A ''B. C B A +'+'C.ABCD. C B '+'3. 下列函数中不等于A 的是( )。

A. A +1B. A +AC. A +ABD. A (A +B )4. 在逻辑代数的加法运算中,1+1=( )。

A. 2B. 1C. 10D. 05. A ⊕1=( )。

A. AB. 1C. A 'D. 06. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是()。

A. 3 B. 8 C. 14 D. 167. 下列函数中等于AB 的是( )。

A. (A +1)BB. (A +B )BC. A +ABD. A (AB )8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。

A. 3B. 10C. 1024D. 6009. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。

A. 3B. 4C. 10D. 75第三章:1. 采用漏极开路输出门电路(OD 门)主要解决了( )。

A. CMOS 门不能相“与”的问题B. CMOS 门的输出端不能“线与”的问题C. CMOS 门的输出端不能相“或”的问题2. 下列哪个特点不属于CMOS 传输门?( )A. CMOS 传输门属于双向器件。

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。