数字逻辑课后答案第七章

- 格式:pdf

- 大小:358.89 KB

- 文档页数:17

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。

数字电路第七章答案第七章可编程逻辑器件第一节基本内容一、基本知识点(一)可编程逻辑器件基本结构可编程逻辑器件是70年代发展起来的新型逻辑器件,相继出现了只读存储器、可编程只读存储器、可编程逻辑阵列、可编程阵列逻辑、通用阵列逻辑和可擦写编程逻辑器件等多个品种,它们的组成和工作原理基本相似。

的基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而的“与或”结构对实现数字电路具有普遍意义。

在中,输入电路中为了适应各种输入情况,每一个输入信号都配有一缓冲电路,使其具有足够的驱动能力,同时产生原变量和反变量输出,为与门阵列提供互补信号输入。

输出电路的输出方式有多种,可以由或阵列直接输出,构成组合方式输出,也可以通过寄存器输出,构成时序方式输出。

输出既可以是低电平有效,也可以是高电平有效;既可以直接接外部电路,也可以反馈到输入与阵列,由此可见的输出电路根据不同的可编程逻辑器件有所不同。

(二)可编程逻辑器件分类1.按编程部位分类有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程(2)与或阵列均可编程(3)与阵列可编程,或阵列固定归纳上述的结构特点,列于表7-1。

表7-1 各种的结构特点2.按编程方式分类(1)掩膜编程(2)熔丝与反熔丝编程(3)紫外线擦除、电可编程(4)电擦除、电可编程(5)在系统编程()(三)高密度可编程逻辑器件通常衡量可编程逻辑器件芯片的密度是以芯片能容纳等效逻辑门的数量,一般是以2000为界限,即芯片容纳等效逻辑门小于2000门,称它为低密度可编程逻辑器件或简单的可编程逻辑器件(),若大于2000等效逻辑门,称为高密度可编程逻辑器件()。

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 00 1 0 0 00 1 1 1 11 0 0 0 01 0 1 1 11 1 0 1 11 1 1 0 07.证明下列等式(1)A+A B=A+B证明:左边= A+A B=A(B+B)+A B=AB+A B+A B=AB+A B+AB+A B=A+B=右边(2)ABC+A B C+AB C=AB+AC证明:左边= ABC+A B C+AB C= ABC+A B C+AB C+ABC=AC(B+B)+AB(C+C)=AB+AC=右边(3)EDCCDACBAA)(++++=A+CD+E 证明:左边=EDCCDACBAA)(++++=A+CD+A B C+CD E=A+CD+CD E=A+CD+E=右边(4) C B A C B A B A ++=C B C A B A ++ 证明:左边=C B A C B A B A ++=C B A C AB C B A B A +++)( =C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式 (1) F=A+ABC+A C B +CB+C B = A+BC+C B (2) F =(A+B+C )(A+B+C) = (A+B)+C C = A+B(3) F =ABC D +ABD+BC D +ABCD+B C = AB+BC+BD (4) F=C AB C B BC A AC +++= BC(5) F=)()()()(B A B A B A B A ++++=B A 9.将下列函数展开为最小项表达式 (1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14) 10.用卡诺图化简下列各式(1)C AB C B BC A AC F +++=0 ABC00 01 11 1011111化简得F=C(2)C B A D A B A D C AB CD B A F++++=111111AB CD 00 01 11 1000011110化简得F=D A B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111AB CD 00 01 11 1000011110化简得F=D BC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=AC AD B A ++11.利用与非门实现下列函数,并画出逻辑图。

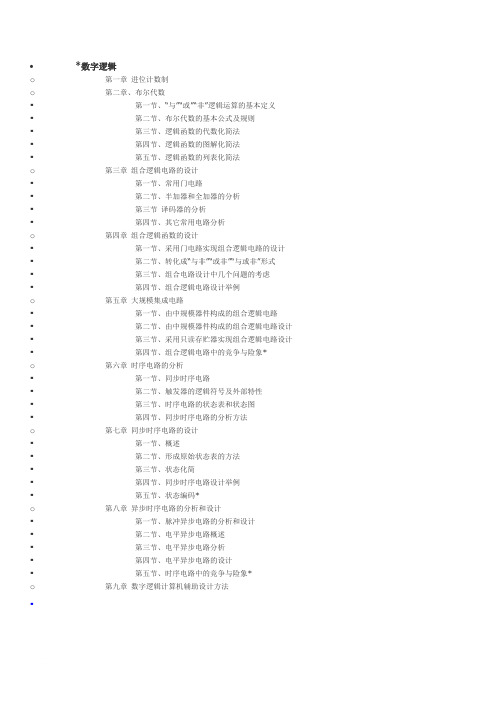

*数字逻辑o第一章进位计数制o第二章、布尔代数▪第一节、“与”“或”“非”逻辑运算的基本定义▪第二节、布尔代数的基本公式及规则▪第三节、逻辑函数的代数化简法▪第四节、逻辑函数的图解化简法▪第五节、逻辑函数的列表化简法o第三章组合逻辑电路的设计▪第一节、常用门电路▪第二节、半加器和全加器的分析▪第三节译码器的分析▪第四节、其它常用电路分析o第四章组合逻辑函数的设计▪第一节、采用门电路实现组合逻辑电路的设计▪第二节、转化成“与非”“或非”“与或非”形式▪第三节、组合电路设计中几个问题的考虑▪第四节、组合逻辑电路设计举例o第五章大规模集成电路▪第一节、由中规模器件构成的组合逻辑电路▪第二节、由中规模器件构成的组合逻辑电路设计▪第三节、采用只读存贮器实现组合逻辑电路设计▪第四节、组合逻辑电路中的竞争与险象*o第六章时序电路的分析▪第一节、同步时序电路▪第二节、触发器的逻辑符号及外部特性▪第三节、时序电路的状态表和状态图▪第四节、同步时序电路的分析方法o第七章同步时序电路的设计▪第一节、概述▪第二节、形成原始状态表的方法▪第三节、状态化简▪第四节、同步时序电路设计举例▪第五节、状态编码*o第八章异步时序电路的分析和设计▪第一节、脉冲异步电路的分析和设计▪第二节、电平异步电路概述▪第三节、电平异步电路分析▪第四节、电平异步电路的设计▪第五节、时序电路中的竞争与险象*o第九章数字逻辑计算机辅助设计方法▪3 / 205 / 207 / 209 / 2011 / 20A. B. C. D. 参考答案:D13 / 2015 / 2017 / 20。

第七章 时序逻辑电路1.电路如图P7.1所示,列出状态转换表,画出状态转换图和波形图,分析电路功能。

图P7.1 解:(1)写出各级的W.Z 。

D 1=21Q Q ,D 2=Q 1,Z=Q 2CP( 2 ) 列分析表( 3 ) 状态转换表(4)状态转换图和波形图。

Q 2 Q 1 D 2 D 1 Q 2n+1 Q 1n+1 Z 0 0 0 1 0 1 0 0 1 1 0 1 0 0 1 0 0 0 0 0 1 1 1 1 0 1 0 1Q 2 Q 1 Q 2n+1 Q 1n+1 Z 0 0 0 1 0 0 1 1 0 0 1 0 0 0 1 1 1 1 0 1CPCP Q 1 0 Q 1 0Z( b )Q 2 Q 1 /Z( a )01/011/1 10/100/0图7.A1本电路是同步模3计数器。

2. 已知电路状态转换表如表P7.1所示,输入信号波形如图P7.2所示。

若电路的初始状态为Q2Q1 = 00,试画出Q2Q1的波形图(设触发器的下降沿触发)。

解:由状态转换表作出波形图3. 试分析图P7.3所示电路,作出状态转换表及状态转换图,并作出输入信号为0110111110相应的输出波形(设起始状态Q2Q1 = 00)。

( a )表P7.1XQ2 Q10 10001101101/110/010/001/111/110/011/000/1Q2n+1 Q1n+1/ZCPXQ1 0Q2 0Z图P7.2CPXQ1 0Q1 0Z图P7.A2( b )解:(1)写W.Z 列分析表J 1 = XQ 2 1Q Q X K 1 = X( 2 ) 作出状态转换表及状态转换图(3)作出输出波形图:1 根据状态转换表,作出状态的响应序列,设y = Q 2Q 1 X : 0 1 1 0 1 1 1 1 1 0 y n : 0 02 1 0 2 13 3 3 y n+1: 0 2 1 0 2 1 3 3 3 0Z : 1 1 1 1 1 1 1 0 0 12 根据状态响应序列画响应的输出波形。

第一章逻辑门电路§1-1 基本门电路一、填空题1.与逻辑;Y=A·B2.或逻辑;Y=A+B3.非逻辑;Y=4.与;或;非二、选择题1. A2. C3. D三、综合题1.2.真值表逻辑函数式Y=ABC§1-2 复合门电路一、填空题1.输入逻辑变量的各种可能取值;相应的函数值排列在一起2.两输入信号在它们;异或门电路3.并;外接电阻R;线与;线与;电平4.高电平;低电平;高阻态二、选择题1. C2. B3. C4. D5. B三、综合题1.2.真值表逻辑表达式Y1=ABY2=Y3==A+B 逻辑符号3.第二章组合逻辑电路§2-1 组合逻辑电路的分析和设计一、填空题1.代数;卡诺图2.n;n;原变量;反变量;一;一3.与或式;1;04.组合逻辑电路;组合电路;时序逻辑电路;时序电路5.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1. ×2. √3. √4. √5. ×6. √四、综合题1.略2.(1)Y=A+B(2)Y=A B+A B(3) Y=ABC+A+B+C+D=A+B+C+D3. (1) Y=A B C+A B C+ A B C + ABC=A C+AC(2) Y=A CD+A B D+AB D+AC D(3) Y=C+A B+ A B4. (a)逻辑函数式Y= Y=AB+A B真值表逻辑功能:相同出1,不同出0 (b)逻辑函数式Y=AB+BC+AC真值表逻辑功能:三人表决器5.状态表逻辑功能:相同出1,不同出0逻辑图1. 6.Y=A ABC+B ABC+C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

§2-2 加法器一、填空题1.加数与被加数;低位产生的进位2.加数与被加数;低位产生的进位3.加法运算二、选择题1. A2. C三、综合题1.略2.略3.§2-3 编码器与比较器一、填空题1. 编码2. 101011;010000113. 十;二;八;十六4. 0;1;逢二进一;10;逢十进一5. 二进制编码器;二—十进制编码器6. 两个数大小或相等7. 高位二、选择题1. A2. B3. C4. B三、综合题1.略2.(1)10111;00100011(2)00011001;19(3)583. (1)三位二进制(2)1,1,0(3)1,1,14.§2-4 译码器与显示器一、填空题1. 编码器;特定含意的二进制代码按其原意;输出信号;电位;解码器2. 二进制译码器;二—十进制译码器;显示译码器3. LED数字显示器;液晶显示器;荧光数码管显示器4. 1.5~3;10mA/段左右5. 共阴极显示译码器;共阳极显示译码器;液晶显示译码器二、选择题1. A;D2. A三、判断题1.√2.×3.×4.√5.√四、综合题七段显示译码器真值表f=D C B A +D C B A +D C B A+D CB A +D C B A +D C B A =D+B A +C A +C B =DB AC AC B§2-5 数据选择器与分配器一、填空题1.多路调制器;一只单刀多掷选择开关;地址输入;数字信息;输出端2.从四路数据中,选择一路进行传输的数据选择器3.地址选择;输出端二、选择题1. D2. A;C三、判断题1. √2. ×四、综合题1.略2. Y=A B D0+A BD1+A B D2+ABD3第三章触发器§3-1 基本RS触发器与同步RS触发器一、填空题1.两个;已转换的稳定状态2.R S+RSQ n;R+S=13. R S Q n+ R S;RS=04.置0;置15.相同;低电平;高电平6.时钟信号CP7.D触发器8.空翻二、选择题1.D2.B3.A4.B5.B6.D三、判断题1. ×2. ×3. √4. ×5. ×6. ×四、综合题1.略2.3.4.5.略§3-2主从触发器与边沿触发器一、填空题1.空翻2.置0、置1、保持、翻转3.D、J Q n+K Q n4.保持、置1、清0、翻转5.电平、主从6.一次变化7.边沿触发器8.不同、做成9.置0、置1、时钟脉冲二、选择题1.A2.A3.D4.B5.A6.C7.D8.B9.A10.D三、判断题1. √2. ×3. ×4. ×5. √6. ×7. √8. √四、综合题1.2.3.4.略5.略6.§3-3触发器的分类与转换一、填空题1.T、T'2. T Q n+ T Q n、Q n3.1、04. Q n、Q n5. 16. T'7. T8. T'二、选择题1.D2.D3.D4.B5.B三、判断题1. ×2. ×3. ×4. ×四、分析解答题1.2.3.略4.略5.略第四章时序逻辑电路§4-1 寄存器一、填空题1.输入信号;锁存信号2.接收;暂存;传递;数码;移位二、选择题1. C2. B;A三、判断题1. √2. ×3. √四、综合题1.JK触发器构成D触发器,即Q n+1= D。

数字逻辑课程作业_A交卷时间:2016-05-04 16:55:11 一、单选题1.(4分)如图x1-275A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第一章收起解析答案D解析第一章补码2.(4分)以下电路中常用于总线应用的有()A. TSL门B.OC门C. 漏极开路门D.CMOS与非门纠错得分:0知识点:第三章收起解析答案A解析第三章其他类型的TTL与非门电路3.(4分)如果异步二进制计数器的触发器为10个,则计数状态有()种A. A:20B. B:200C. C:1000D. D:1024纠错得分:0知识点:第九章收起解析答案D解析第九章计数器4.(4分)用n个触发器构成的计数器,可得到的最大计数模是()A. (A) nB. (B) 2nC. (C) 2nD. (D)2n-1纠错得分:4知识点:第六章收起解析答案C解析第六章触发器电路结构和工作原理5.(4分)如图x1-109A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第四章收起解析答案C解析第四章组合逻辑电路的分析6.(4分)如图x1-229A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第五章收起解析答案D解析第五章译码器7.(4分)如图x1-218A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第十一章收起解析答案C解析第十一章数字系统概述8.(4分)化简如图h-d-1-22A. AB. BC. CD. D纠错得分:0知识点:第三章收起解析答案A解析第三章逻辑代数基础/逻辑函数的化简9.(4分)如图x1-371A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第十一章收起解析答案C解析第十一章数字系统概述10.(4分)如图x1-165A. (A)B. (B)C. (C)D. (D)纠错得分:0知识点:第二章收起解析答案D解析第二章逻辑函数表达式的形式和转换方法11.(4分)如图x1-342A. (A)B. (B)C. (C)D. (D)纠错得分:4知识点:第五章收起解析答案C解析第五章数据选择器12.(4分)数字系统工作的特点是具有___ 。