Storm_IV_E30_V1.3开发板管脚分配

- 格式:xls

- 大小:32.50 KB

- 文档页数:24

详解Arduino Uno开发板的引脚分配图及定义(重要且基础)首先开发板实物图如下:在本篇文章中,我们将详细介绍Arduino开发板的硬件电路部分,具体来说,就是介绍Arduino Uno开发板的引脚分配图及定义。

Arduino Uno微控制器采用的是Atmel 的ATmega328。

Arduino Uno开发板的引脚分配图包含14个数字引脚、6个模拟输入、电源插孔、USB连接和ICSP插头。

引脚的复用功能提供了更多的不同选项,例如驱动电机、LED、读取传感器等。

在这篇文章中,我们将介绍Arduino Uno引脚的功能。

Arduino Uno引脚分配图Arduino Uno引脚分配- 电源Arduino Uno开发板可以使用三种方式供电:●直流电源插孔-可以使用电源插孔为Arduino开发板供电。

电源插孔通常连接到一个适配器。

开发板的供电范围可以是5-20V,但制造商建议将其保持在7-12V之间。

高于12V时,稳压芯片可能会过热,低于7V可能会供电不足。

●VIN引脚- 该引脚用于使用外部电源为Arduino Uno开发板供电。

电压应控制在上述提到的范围内。

●USB电缆- 连接到计算机时,提供500mA/5V电压。

在电源插孔的正极与VIN引脚之间链接有一个极性保护的二极管,额定电流为1安培。

您使用的电源决定了可用于电路的功率。

例如,使用USB为电路供电时,电流最大限制在500mA。

考虑到该电源也用于为MCU、外围设备、板载稳压器和与其连接的组件供电。

当通过电源插座或VIN为电路供电时,可用的最大电流取决于Arduino开发板上的5V和3.3V稳压器。

●5v和3v3根据制造商的数据手册,它们提供稳压的5V和3.3v,向外部组件供电。

●GND在Arduino Uno引脚分配图中,可以看到有5个GND引脚,它们都是互连的。

GND引脚用于闭合电路回路,并在整个电路中提供一个公共逻辑参考电平。

务必确保所有的GND(Arduino、外设和组件)相互连接并且有共同点。

创新开发平台实验指导书实验指导书威世达通信操纵技术〔北京〕2021年8月第一节:FT3150/PL3150模块及其底板 (8)一、FT3150模块及底板 (8)二、PL3150模块及底板 (10)第二节:DI模块 (12)一、硬件原理及连接 (12)二、组网 (13)第一步:创建lonMaker网络 (13)第二步:添加DI设备 (16)第三步:通过配置属性对节点的功能进行配置 (19)三、摸索及实验 (26)第三节:DO模块 (28)一、硬件原理及连接 (28)二、组网 (28)第一步:打开之前创建的LonMaker网络 (28)第二步:添加DO设备 (30)第三步:通过配置属性对节点的功能进行配置 (33)三、摸索及实验 (36)第四节:AI模块 (39)一、硬件原理及连接 (39)二、组网 (40)第一步:创建LonMaker网络 (40)第二步:添加AI设备 (41)第三步:通过配置属性对节点的功能进行配置 (42)三、摸索及实验 (44)第五节:AO模块 (46)一、硬件原理及连接 (46)第一步:打开之前创建的LonMaker网络 (47)第二步:添加AO设备 (47)第三步:通过配置属性对节点的功能进行配置 (48)第四步:PID功能块 (52)三、摸索及实验 (54)第六节:LCD模块 (57)一、硬件连接 (57)二、组网 (57)第一步:打开之前创建的LonMaker网络 (57)第二步:添加LCD设备 (58)第三步:通过配置属性对节点的功能进行配置 (60)三、摸索及实验 (62)第七节:网关 (63)一、硬件连接 (63)二、组网 (63)第一步:创建新的LonMaker网络 (63)第二步:添加Gate设备 (64)第三步:连接绑定 (64)三、摸索及实验 (67)实验一:第一个NodeBuilder项目 (69)一、目标 (69)二、描述 (69)三、实验步骤 (69)第一步:创建一个LonMaker网络 (69)第二步:从LonMaker中启动NodeBuilder并创建一个新的项目 (70)第三步:从NodeBuilder启动设备模板向导并创建一个新的设备模板 (71)第四步:Build一个简单的应用程序 (74)第五步:在LonMaker网络中添加使用新设备模板的设备 (75)实验二:为设备添加设备接口 (76)二、描述 (77)三、实验步骤 (77)第一步:打开之前创建的LonMaker网络及NodeBuilder (77)第二步:为设备添加一个功能块和设备接口 (77)第三步:为新的功能块添加具体功能 (80)实验三:使用NodeBuilder代码向导 (82)一、目标 (82)二、描述 (83)三、实验步骤 (83)第一步:打开之前创建的LonMaker网络及NodeBuilder (83)第二步:使用NodeBuilder代码向导为设备添加一个功能块 (84)第三步:为新的功能块添加具体功能 (88)实验四:输入网络变量数组的处理 (91)一、目标 (91)二、描述 (91)三、实验步骤 (92)第一步:使用代码向导创建DI、DO设备模板 (92)第二步:创建DI设备并添加DI功能代码 (94)第三步:创建DO设备并添加DO功能代码 (95)实验五:指导函数及Debugger操作 (96)一、目标 (96)二、描述 (97)三、实验步骤 (97)第一步:进入Debug状态并设置断点 (97)第二步:一步一步执行代码 (99)组态一:人机界面实验 (101)一、创建网络 (101)1、运行LNS DDE Server。

XSSA30-U213-V1开发板数据手册西安智多晶微电子有限公司XIAN Intelligence Silicon Technology 西安市高新区科技二路72号西安软件园西岳阁102室邮编710075文档修订历史目录1 开发板简介 (3)1.1概述 (4)1.2特点 (4)2 开发板框图 (5)3 开发板引脚分配................................................................................................................................... .63.1时钟引脚............................................................................................................................... .63.2以太网接口........................................................................................................................... .73.3HDMI TX接口 (9)3.4SD卡接口 (11)3.5EEPROM存储芯片 (11)3.6摄像头接口 (11)3.7USB转串口 (13)3.8按键 (14)3.9LED指示灯 (14)3.1040P牛角插座 (14)1.开发板简介1.1 概述:为了更好让客户评估智多晶28nm 30K逻辑FPGA 芯片,我们设计了一款可用于前期评估和移植验证的平台,该开发板的核心器件是西安智多晶的SA5Z-30-D1-8U213,基于低功耗28nm CMOS铜工艺,可用于工业控制、视频接口处理等领域客户的前期评估。

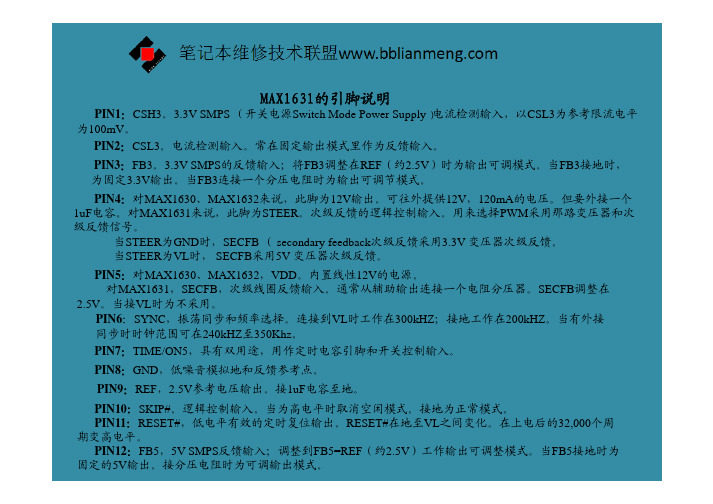

MAX1631的引脚说明PIN1:CSH3。

3.3V SMPS(开关电源Switch Mode Power Supply )电流检测输入,以CSL3为参考限流电平为100mV。

PIN2:CSL3。

电流检测输入。

常在固定输出模式里作为反馈输入。

PIN3:FB3。

3.3V SMPS的反馈输入;将FB3调整在REF(约2.5V)时为输出可调模式。

当FB3接地时,为固定3.3V输出。

当FB3连接一个分压电阻时为输出可调节模式。

PIN4:对MAX1630、MAX1632来说,此脚为12V输出。

可往外提供12V,120mA的电压。

但要外接一个1uF电容。

对MAX1631来说,此脚为STEER。

次级反馈的逻辑控制输入。

用来选择PWM采用那路变压器和次级反馈信号。

当STEER为GND时,SECFB(secondary feedback次级反馈采用3.3V 变压器次级反馈。

当STEER为VL时,SECFB采用5V 变压器次级反馈。

PIN5:对MAX1630、MAX1632,VDD。

内置线性12V的电源。

对MAX1631,SECFB,次级线圈反馈输入。

通常从辅助输出连接一个电阻分压器。

SECFB调整在。

当接时为不采用。

2.5V VLPIN6:SYNC,振荡同步和频率选择。

连接到VL时工作在300kHZ;接地工作在200kHZ。

当有外接同步时时钟范围可在240kHZ至350Khz。

PIN7:TIME/ON5,具有双用途,用作定时电容引脚和开关控制输入。

PIN8:GND,低噪音模拟地和反馈参考点。

PIN9:REF,2.5V参考电压输出。

接1uF电容至地。

PIN10:SKIP#。

逻辑控制输入。

当为高电平时取消空闲模式。

接地为正常模式。

PIN11:RESET#,低电平有效的定时复位输出。

RESET#在地至VL之间变化。

在上电后的32,000个周32000期变高电平。

PIN12:FB5,5V SMPS反馈输入;调整到FB5=REF(约2.5V)工作输出可调整模式。

msp430引脚引脚功能引脚名称序号I/O 说明Avcc 64 模拟供电电源正端.只为ADC和DAC的模拟部分供电Avss 62 模拟供电电源负端.只为ADC和DAC的模拟部分供电DVcc 1 数字供电电源正端.为所有数字部分供电DVss 63 数字供电电源负端.为所有数字部分供电P1.0/TACLK 12 I/O 通用数字I/O引脚/定时器A时钟信号TACLK 输入P1.1/TA0 13 I/O 通用数字I/O引脚/定时器A捕捉:CCI0A输入,比较:OUT0输出P1.2/TA1 14 I/O 通用数字I/O引脚/定时器A捕捉:CCI1A输入,比较:OUT1输出P1.3/TA2 15 I/O 通用数字I/O引脚/定时器A捕捉:CCI2A输入,比较:OUT2输出P1.4/SMCLK 16 I/O 通用数字I/O引脚/SMCLK信号输出P1.5/TA0 17 I/O 通用数字I/O引脚/定时器A,比较:OUT0输出P1.6/TA1 18 I/O 通用数字I/O引脚/定时器A,比较:OUT1输出P1.7/TA2 19 I/O 通用数字I/O引脚/定时器A,比较:OUT2输出P2.0/ACLK 20 I/O 通用数字I/O引脚/ACLK输出P2.1/TAINCLK 21 I/O 通用数字I/O引脚/定时器A,INCLK上的时钟信号P2.2/CAOUT/TA0 22 I/O 通用数字I/O引脚/定时器A捕获:CCI0B输入/比较器输出P2.3/CA0/TA1 23 I/O 通用数字I/O引脚/定时器A,比较:OUT1输出/比较器A输入P2.4/CA1/TA2 24 I/O 通用数字I/O引脚/定时器A,比较:OUT2输出/比较器A输入P2.5/Rosc 25 I/O 通用数字I/O引脚,定义DCO标称频率的外部电阻输入P2.6/ADC12CLK/ 26 I/O 通用数字I/O引脚,转换时钟-12位ADC,DMA通道0外部触发器P2.7/TA0 27 I/O 通用数字I/O引脚/定时器A比较:OUT0输出P3.0/STE0 28 I/O 通用数字I/O引脚,USART0/SPI模式从设备传输使能端P3.1/SIMO0/SDA 29 I/O 通用数字I/O引脚,USART0/SPI模式的从入/主出,I2C数据P3.2/SOMI0 30 I/O 通用数字I/O引脚,USART0/SPI模式的从出/主入P3.3/UCLK0/SCL 31 I/O 通用数字I/O引脚,USART0/SPI模式的外部时钟输入,USART0 P3.4/UTXD0 32 I/O 通用数字I/O引脚,USART0/UART模式的传输数据输出P3.5/URXD0 33 I/O 通用数字I/O引脚,USART0/UART模式的接收数据输入P3.6/UTXD1 34 I/O 通用数字I/O引脚,USI1/UART模式的发送数据输出P3.7/URXD1 35 I/O 通用数字I/O引脚,USI1/UART模式的接收数据输入P4.0/TB0 36 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR0P4.1/TB1 37 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR1P4.2/TB2 38 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR2P4.3/TB3 39 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR3P4.4/TB4 40 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR4P4.5/TB5 41 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR5P4.6/TB6 42 I/O 通用数字I/O引脚,捕获I/P或者PWM输出端口-定时器B7 CCR6P4.7/TBCLK 43 I/O 通用数字I/O引脚,输入时钟TBCLK-定时器B7P5.0/STE1 44 I/O 通用数字I/O引脚,USART1/SPI模式从设备传输使能端P5.1/SIMO1 45 I/O 通用数字I/O引脚,USART1/SPI模式的从入/主出P5.2/SOMI1 46 I/O 通用数字I/O引脚,USART1/SPI模式的从出/主入P5.3/UCLK1 47 I/O 通用数字I/O引脚,USART1/SPI模式的外部时钟输入,USART0/SPI 模式的时钟输出- 8 -P5.4/MCLK 48 I/O 通用数字I/O引脚,主系统时钟MCLK输出P5.5/SMCLK 49 I/O 通用数字I/O引脚,子系统时钟SMCLK输出P5.6/ACLK 50 I/O 通用数字I/O引脚,辅助时钟ACLK输出P5.7/TboutH/ 51 I/O 通用数字I/O引脚,将所有PWM数字输出端口为高阻态-定时器B7P6.0/A0 59 I/O 通用数字I/O引脚,模拟量输入A0-12位ADC P6.1/A1 60 I/O 通用数字I/O引脚,模拟量输入A1-12位ADC P6.0/A2 61 I/O 通用数字I/O引脚,模拟量输入A2-12位ADC P6.0/A3 2 I/O 通用数字I/O引脚,模拟量输入A3-12位ADC P6.0/A4 3 I/O 通用数字I/O引脚,模拟量输入A4-12位ADC P6.0/A5 4 I/O 通用数字I/O引脚,模拟量输入A5-12位ADC P6.0/A6/DAC0 5 I/O 通用数字I/O引脚,模拟量输入A6-12位ADC,DAC.0输出P6.0/A7/DAC1/ 6 I/O 通用数字I/O引脚,模拟量输入A7-12位ADC,DAC.1输出,SVS输入RST/NMI 58 I 复位输入,不可屏蔽中断输入端口或者Bootstrap Lload启动(FLASHTCK 57 I 测试时钟,TCK是芯片编程测试和bootstrap loader启动的时钟输入端口TDI 55 I 测试数据输入,TDI用作数据输入端口,芯片保护熔丝连接到TDITDO/TDI 54 I/O 测试数据输出端口,TDO/TDI数据输出或者编程数据输出引脚TMS 56 I 测试模式选择,TMS用作芯片编程和测试的输入端口VeREF+ 10 I/P 外部参考电压的输入VREF+ 7 O 参考电压的正输出引脚VREF-/VeREF- 11 O 内部参考电压或者外加参考电压的引脚XIN 8 I 晶体振荡器XT1的输入端口,可连接标准晶振或者钟表晶振XOUT/TCLK 9 I/O 晶体振荡器XT1的输出引脚或测试时钟输入XT2IN 53 I 晶体振荡器XT2的输入端口,只能连接标准晶振XT2OUT 52 O 晶体振荡器XT2的输出引脚。

从控制器的管脚定义看特斯拉Model3的功能分配-HVBattery篇终于只剩下最后⼀⼤块、也是我理解相对⽋缺的⾼压部分,现在整理出来供⼤家参考。

图1 特斯拉Model 3⾼压(电机除外)⽹络拓扑框图事实上,正如图1中所⽰,Model 3的⾼压部分主要包含四个模块:HV Battery(即BMS)、HVP(High Voltage Processor,⾼压处理单元)、PCS(Power Conversion System,功率转换系统)、CP(Charge Port ECU,充电⼝控制器),我们依次看下。

⼀、HV Battery/电池管理系统图2 特斯拉Model 3 HV Battery/电池管理系统管脚定义作为和外部系统接⼝的HV Battery/电池管理系统,接⼝看起来不算复杂,我们依次、想到哪⼉说到哪⼉。

1、供电,⾼压系统(CP除外)的低压供电都是从HV Battery/电池管理系统接⼊;2、⾼压互锁,特斯拉Model 3有三个互锁回路:外部⾼压部件(包括电池、电机、压缩机和PTC)、⾼压电池包内部以及充电回路,但是所有的检测都是由HVP/⾼压处理单元完成,佐证如下,图3 HVP/⾼压处理单元发出所有的HVIL状态3、⽹络连接,HV Battery/电池管理系统两路CAN,⼀路挂载Vehicle、⼀路⽤于⾼压系统内部通信,充当了‘⼩’⽹关——这是与常见设计有区分的地⽅;4、来⾃CP的故障输⼊和锁⽌使能没能太理解,因为不属于标准要求或建议、同时有总线通信,为什么还需要硬线的连接?5、碰撞信号输⼊,⾸先⼀点特斯拉Model 3碰撞信号输出只连接了HV Battery/电池管理系统,我们理解即最直接的主正主负继电器拥有最⾼优先级;但是问题在于主正主负继电器实际由HVP/⾼压处理单元驱动?和朋友沟通之后我们认为原因有⼆,⼀是HV Battery/电池管理系统充当了⾼压原理部分的‘⼤脑’、⼀是所有外部接⼝都会经过HV Battery/电池管理系统。

xx大学毕业设计(论文)题目:单片机实现的步进电机控制系统设计作者:系(部):专业班级:指导教师:职称:20 年月日步进电机控制系统的组成如图4.1所示:图4.1 控制系统图3、本课题需要重点研究的、关键的问题及解决的思路[8]步进电机控制程序设计的主要问题有三个:第一、控制脉冲产生;第二、步进电机的旋转方向和时序脉冲的关系;第三、步数的确定。

作为单片机控制步进电机的程序的构成也是主要由这几个问题,因此可以从这三个问题入手:(1)控制脉冲的产生在单片机控制步进电机时,一般来讲,控制是用软件产生的。

方法是先输出一个高电平,然后延时,再输出低电平,再进行延时。

延时时间的长短由步进电机的工作频率决定。

(2)步进电机的旋转方向和时序脉冲的关系产生时序脉冲的方法是:1 单片机的IO 端口,分别控制三相步进电机的A, B, C 三相绕组;2 控制模式写出控制模型;2 制模型的顺序向步进电机输入控制脉冲。

(3)步数的确定步进电机运行的步数可由步距角和需要转过的角度来计算:NZ r b ⋅︒=360θ 式中:b θ-步距角;r Z -转子齿数; N -拍数(一般三拍时N =m 或六拍时N =2m );m -控制绕组相数,m =3毕业设计(论文)任务书学生姓名_1111指导教师_黄云龙、廖东进、朱秋琴职称副教授、助教、助教系别_信息与电子工程系_专业电气年级 03级___班级课题名称单片机实现的步进电机控制系统设计任务与要求:一、设计(论文)要求:本课题的主要任务是通过单片机控制系统,实现对步进电机工作状态的控制。

具体设计方案如下:本设计采用凌阳16 位单片机SPCE061A对步进电机进行控制,通过IO 口输出的具有时序的方波作为步进电机的控制信号,信号经过芯片L298N驱动步进电机;同时,用4X4的键盘来对电机的状态进行控制,并用数码管显示电机的转速,采用74LS164作为4位单个数码管的显示驱动,从单片机输入信号;利用凌阳单片机的语音功能播报电机的转速。

XilinxFPGA引脚功能具体介绍之杨若古兰创作注:技术交流用,但愿对大家有所帮忙.IO_LXXY_# 用户IO引脚XX代表某个Bank内独一的一对引脚,Y=[P|N]代表对上升沿还是降低沿敏感,#代表bank号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能.Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口.在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚酿成输出口.配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bitserial模式下,DIN是旌旗灯号数据的输入;在SPI模式下,MISO 是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位.D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs.An:O,A[25:0]为BPI模式的地址位.配置完成后,变成用户I/O口.AWAKE:O,电源保管挂起模式的形态输出引脚.SUSPEND是一个公用引脚,AWAKE是一个多功能引脚.除非SUSPEND模式被使能,AWAKE被用感化户I/O.MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平无效的片选旌旗灯号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一名数据.FCS_B:O,BPI flash 的片选旌旗灯号.FOE_B:O,BPI flash的输出使能旌旗灯号FWE_B:O,BPI flash 的写使用旌旗灯号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选旌旗灯号.在SPI模式下,为SPI flsah片选旌旗灯号.IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用.DOUT_BUSY:O,在SelectMAP模式下,BUSY暗示设备形态;在位串口模式下,DOUT提供配置数据流.RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平无效的写使能旌旗灯号;配置完成后,如果须要,RDWR_B可以在BANK2中做为Vref.HSWAPEN:I,在配置以后和配置过程中,低电平使用上拉.INIT_B:双向,开漏,低电平暗示配置内存曾经被清理;坚持低电平,配置被延迟;在配置过程中,低电平暗示配置数据错误曾经发生;配置完成后,可以用来唆使POST_CRC形态.SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性.CMPMOSI,CMPMISO,CMPCLK:N/A,保存.M0,M1:I,配置模式选择.M0=并口(0)或者串口(1),M1=主机(0)或者从机(1).CCLK:I/O,配置时钟,主模式下输出,从模式下输入.USERCCLK:I,主模式下,可行用户配置时钟.GCLK:I,这些引脚连接到全局时钟缓存器,在不须要时钟的时候,这些引脚可以作为惯例用户引脚.VREF_#:N/A,这些是输入临界电压引脚.当内部的临界电压不须要时,他可以作为普通引脚.当做作bank内参考电压时,所有的VRef都必须被接上.3.多功能内存控制引脚M#DQn:I/O,bank#内存控制数据线D[15:0]M#LDQS:I/O,bank#内存控制器低数据选通脚M#LDQSN:I/O,bank#中内存控制器低数据选通NM#UDQS:I/O,bank#内存控制器高数据选通脚M#UDQSN:I/O,bank#内存控制器高数据选通NM#An:O,bank#内存控制器地址线A[14:0]M#BAn:O,bank#内存控制bank地址BA[2:0]M#LDM:O,bank#内存控制器低位掩码M#UDM:O,bank#内存控制器高位掩码M#CLK:O,bank#内存控制器时钟M#CLKN:O,bank#内存控制器时钟,低电平无效M#CASN:O,bank#内存控制器低电平无效行地址选通M#RASN:O,bank#内存控制器低电平无效列地址选通M#ODT:O,bank#内存控制器内部内存的终端旌旗灯号控制M#WE:O,bank#内存控制器写使能M#CKE:O,bank#内存控制器时钟使能M#RESET:O,bank#内存控制器复位4.公用引脚DONE_2:I/O,DONE是一个可选的带有内部上拉电阻的双向旌旗灯号.作为输出,这个引脚说明配置过程曾经完成;作为输入,配置为低电平可以延迟启动.PROGRAM_B_2:I,低电平异步复位逻辑.这个引脚有一个默认的弱上拉电阻.SUSPEND:I,电源呵护挂起模式的高电平无效控制输入引脚.SUSPEND是一个公用引脚,而AWAKE是一个复用援用.必须通过配置选项使能.如果挂起模式没有使用,这个引脚接地.TCK:I,JTAG鸿沟扫描时钟.TDI:I,JTAG鸿沟扫描数据输入.TDO:O,JTAG鸿沟扫描数据输出.TMS:I,JTAG鸿沟扫描模式选择5.保存引脚NC:N/A,CMPCS_B_2:I,保存,不接或者连VCCO_26.其它GND:VBATT:RAM内存备份电源.一旦VCCAUX利用了,VBATT可以不接;如果KEY RAM没有使用,推荐把VBATT接到VCCAUX或者GND,也能够不接.VCCAUX:辅助电路电源引脚VCCINT:内部核心逻辑电源引脚VCCO_#:输出驱动电源引脚VFS:I,(LX45不成用)编程时,key EFUSE电源供电引脚.当不编程时,这个引脚的电压应当限制在GND到3.45V;当不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,悬空也能够.RFUSE:I,(LX45不成用)编程时,key EFUSE接地引脚.当不编程时或者不使用key EFUSE时,推荐把该引脚连接到VCCAUX或者GND,然而,也能够悬空.7.GTP 引脚MGTAVCC:收发器混合旌旗灯号电路电源引脚MGTAVTTTX,MGTAVTTRX:发送,接收电路电源引脚MGTAVTTRCAL:电阻校订电路电源引脚MGTAVCCPLL0,MGTAVCCPLL1:锁相环电源引脚MGTREFCLK0/1P,MGTREFCLK0/1N:差分时钟正负引脚MGTRREF:内部校准终端的精密参考电阻引脚MGTRXP[1:0],MGTRXN[1:0]:差分接收端口MGTTXP[1:0],MGTTXN[1:0]:差分发送端口• 1. Spartan6系列封装概述Spartan6系列具有低成本、省空间的封装方式,能使用户引脚密度最大化.所有Spartan6 LX器件之间的引脚分配是兼容的,所有Spartan6 LXT器件之间的引脚分配是兼容的,但是Spartan6 LX和Spartan6 LXT器件之间的引脚分配是不兼容的.表格 1Spartan6系列FPGA封装2. Spartan6系列引脚分配及功能胪陈Spartan6系列有本人的公用引脚,这些引脚是不克不及作为Select IO使用的,这些公用引脚包含:公用配置引脚,表格2所示 GTP高速串行收发器引脚,表格3所示表格 2Spartan6 FPGA公用配置引脚留意:只要LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚.表格 3Spartan6器件GTP通道数目留意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和 FG(G)900中封装了8个GTP通道.如表4,每一种型号、每一种封装的器件的可用IO 引脚数目不尽不异,例如对于LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚.表格 4Spartan6系列各型号封装可用的IO资本汇总表格 5引脚功能胪陈3. Spartan6系列GTP Transceiver引脚如表6所示,对LX25T,LX45T而言,只要一个GTP Transceiver通道,它的地位是X0Y0,所再Bank号为101;其他旌旗灯号GTP Transceiver的解释类似.表格 6GTP Transceiver所在Bank编号关于XILINX FPGA中VRP/VRN管脚的使用XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚.VRP/VRN管脚是一对多功能管脚,当一个BANK使用到某些DCI(Digitally Controlled Impedance)接口电平尺度时,须要通过该BANK的VRP/VRN管脚接入参考电阻.此时,VRN通过一个参考电阻R上拉到Vcco,VRP通过一个参考电阻R下拉到地.VRP/VRN管脚提供一个参考电压供DCI内部电路使用,DCI内部电路根据此参考电压调整IO输出阻抗与内部参考电阻R匹配.当使用到DCI级联时,仅主BANK (master)须要通过VRP/VRN提供参考电压,从BANK (slave)不须要使用VRP/VRN,从BANK的VRP/VRN管脚可当成普通管脚使用.当VRP/VRN不必于DCI功能时,可用于普通管脚.不须要VRP/VRN外接参考电阻的DCI输出接口电平尺度有:HSTL_I_DCIHSTL_III_DCIHSTL_I_DCI_18HSTL_III_DCI_18SSTL2_I_DCISSTL18_I_DCISSTL15_DCI不须要VRP/VRN外接参考电阻的DCI输入接口电平尺度有:LVDCI_15LVDCI_18LVDCI_25LVDCI_DV2_15LVDCI_DV2_18 LVDCI_DV2_25。