DE2管脚分配

- 格式:xlsx

- 大小:22.55 KB

- 文档页数:8

DE2板资源主要包含的步骤:●设计输入:——可通过电路原理图,或硬件描述语言(VHDL、Verilog)的方式将所需要的电路输入到CAD软件中●综合——将所输入的设计转换成由若干逻辑单元(LE)互联构成的电路,这些LE位于FPGA器件中,他们是具有通用性的基本电路模块;●功能仿真——测试综合后的电路在逻辑功能上的正确性,功能仿真不考虑任何时序问题●布局布线(Fitting)——确定所设计的电路使用到的LE的布局方式及相关连线●时序(Timing)分析、时序仿真——分析布局布线后的电路沿不同路径的传输时延,以提供电路的预期性能指标;检验和估计往电路输入节点施加各种测试信号时的实际输出结果●编程和配置——设置FPGA内部的开关(用于配置LE的电路功能和创建所需的连线)将所设计的电路实现到一个物理的FPGA器件中。

这一步一般由厂商所提供的软硬件工具来完成。

再将设计实现到一个FPGA器件方面而言,编程和配置这两个术语经常通用。

主要步骤:1.创建工程2.绘制原理图(或编写代码)3.编译包含综合布局布线等4.分配引脚5.方针和时序分析6.配置FPGADE2的资源非常丰富,包括:1. 核心的FPGA芯片-Cyclone II 2C35 F672C6,从名称可以看出,它包含有35千个LE,在Altera的芯片系列中,不算最多,但也绝对够用。

Altera下载控制芯片- EPCS16以及USB-Blaste对Jtag的支持。

2.存储用的芯片有:512-KB SRAM,8-Mbyte SDRAM,4-Mbyte Flash memory3. 经典IO配置:拥有4个按钮,18个拨动开关,18个红色发光二极管,9个绿色发光二极管,8个七段数码管,16*2字符液晶显示屏4. 超强多媒体:24位CD音质音频芯片WM8731(Mic输入+LineIn+ 标准音频输出),视频解码芯片(支持NTSC/PAL制式),带有高速DAC视屏输出VGA模块。

《基于软核技术的嵌入式系统设计》实验四、NiosII系统设计——电子钟--DE2北京交通大学计算机学院教师:丁晓明本实验指导书演示了NiosII系统的硬件设计,软件设计,能实现一个电子钟功能。

本实验在前面实验的基础上,同学已经能熟练的使用QuartusII软件和模块化输入方法。

本实验主要包括SOPC Builder,NiosII IDE,QuartusII的使用,主要目的在于指导同学学习如何定制一个NiosII硬件系统和如何在此基础上编写软件程序。

实验条件:Cyclone II EP2C35F672C6教学套件QuartusII9.0SOPC Builder9.0NiosII9.0NiosII IDE在本实验中,我们将以Cyclone II EP2C35F672C6学习板为平台,介绍开发一个电子钟的软、硬件方案设计,涉及到的代码,只需要按照实验指导书将代码拷贝到工程文件夹中即可。

(注意:使用cyclone开发板的同学在设置时需要做相应的改动)系统软、硬件需求分析:1. 该系统要实现的功能:(1). 在液晶屏上显示时间,日期(2). 对时间、日期能够进行设置2. 硬件系统组成规划根据系统要实现的功能和开发板配置,本项目中需要用到的Cyclone II开发板上的外围器件有:LCD:电子钟显示屏幕按钮:电子钟设置功能键Flash存储器:存储软、硬件程序SRAM存储器:程序运行时将其导入SRAM根据所用到的外设和器件特性,在SOPC Builder中建立系统要添加的模块包括:NiosII CPU定时器,按键PIO,LCD,外部RAM总线(Avalon三态桥),外部RAM接口,外部Flash接口。

3.软件系统规划要实现系统所需的功能,大量的工作应该集中在软件设计和优化上。

电子钟的软件功能主要分为显示、设置和时间算法三大部分。

1. 显示部分显示部分的功能包括:(1). 显示时间(小时:分钟:秒)(2). 显示日期(年-月-日)2. 设置部分设置部分的功能包括:设置小时,设置分钟,设置年份,设置月份,设置日期和退出设置。

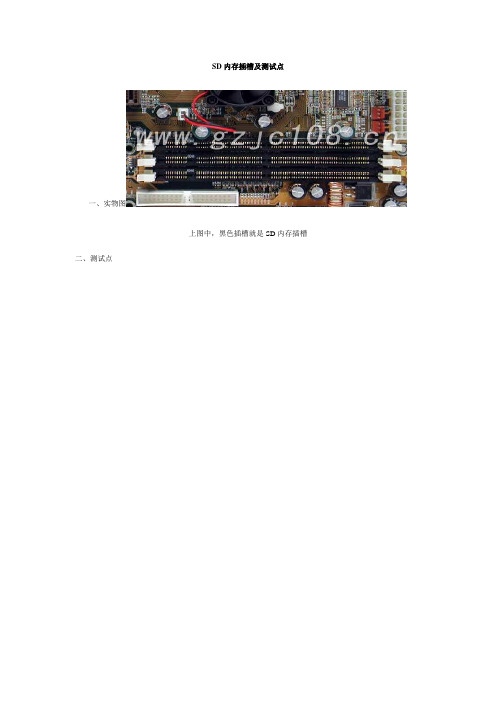

SD内存插槽及测试点一、实物图上图中,黑色插槽就是SD内存插槽二、测试点SD内存插槽测试点:1个供电、4个时钟、6个信号测试点VCC:供电测试点,正常电压3.3V,由场管或橙色线提供CLK0、CLK1、CLK2、CLK3:时钟测试点,频率66/100/133MHZ,电压1.1V-1.6V,由北桥或时钟芯片提供6个信号测试点:CAS#:列选信号RAS#:行选信号/WE#:允许信号(高电平允许读,低电平允许写)/CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压DDR内存插槽及测试点一、实物图上图就是DDR内存插槽实物图二、测试点DDR内存插槽测试点:2个供电、6个时钟、6个信号测试点VCC=2.5V,1.25V:供电测试点CLK0、CLK1、CLK2、CLK3、CLK4、CLK5:时钟测试点,频率266/333/400MHZ,电压1.1V-1. 6V,如果主板有两块时钟芯片,内存时钟由靠近内存的时钟芯片提供;如果只有一个时钟芯片,内存的时钟由北桥提供6个信号测试点:CAS:列选信号RAS:行选信号WE:允许信号(高电平允许读,低电平允许写)CS:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压D58、D56、D18等:是数据线,对地打阻值正常值300-800DDR2内存插槽测试点2009-10-2 10:37:43文/xiaowang 出处:电脑维修家园DDR2内存插槽实物图如下:1、时钟信号点,共有8个时钟信号点,分别位于52、137、138、171、185、186、220、221针脚,正常进,时钟信号点工作电压为1.1V。

2、电压信号点,DDR2内存插槽有2种电压,其中238针脚为3.3V供电脚,51、53、56、59、62、64、69、72、75、78、170、172、175、1 78、181、187、189、191、194针脚为1.8V供电脚。

表1 拨动开关引脚配置

表2 按钮开关引脚配置

表3 LED 引脚配置

表4 七段数码管引脚配置

表5 时钟信号引脚配置信息

表6 LCD 模块引脚配置

表7 HSMC 接口引脚配置

表8 GPIO 引脚配置信息

表9 扩展接口引脚配置信息

表10 ADV7123 引脚配置

表11 音频编解码芯片引脚配置

表12 RS-232 引脚配置

表13 PS/2 引脚配置

表14 千兆以太网芯片引脚配置

表15 TV 解码芯片引脚配置

表16 USB (ISP1362)引脚配置

表17 IR 引脚配置

表18 SRAM 引脚配置

表19 SDRAM 引脚配置

表20 SDRAM 引脚配置

表21 Flash 引脚配置

表22 EEPROM 引脚配置

表23 SD 卡插槽引脚配置。

Altera DE2 使用教程电子信息科学与技术系目录DE2开发板资源: (3)FPGA简要介绍 (5)Quaturs使用基础 (7)用HDL写代码 (22)管脚的输入方式 (25)NIOSII 实验 (25)FAQ (36)DE2开发板资源:Table. DE2 Board InformationFPGA•Cyclone II EP2C35F672C6 with EPCS16 16-Mbit serial configuration deviceI/O Devices•Built-in USB-Blaster TM cable for FPGA configuration•10/100 Ethernet•RS232•Video out (VGA 10-bit DAC)•Video in (NTSC/PAL/multi-format)•USB 2.0 (type A and type B)•PS/2 mouse or keyboard port•Line in/out, microphone in (24-bit Audio CODEC)•Expansion headers (76 signal pins)•Infrared portMemory•8-MBytes SDRAM, 512K SRAM, 4-MBytes flash•SD memory card slotDisplays•16 x 2 LCD display•Eight 7-segment displaysSwitches and LEDs•18 toggle switches•18 red LEDs•9 green LEDs•Four debounced push-button switchesClocks•50-MHz crystal for FPGA clock input•27-MHz crystal for video applications•External SMA clock input可以在目前开发板上做的实验包括基本的VHDL以及Verilog HDL实验接口实验高级实验NIOS II CPU 实验开发套件清单1DE2开发板一个2ByteBlasterII 下载电缆1根35v电源一个4光盘一张FPGA简要介绍FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

/halflife/archive/2010/03/12/1684764.ht mlAbstractSwitches、Lights and MultiplexersRelease: 1.0By yf.x03/12/2010Introduction这个练习的目的是学习如何连接简单的输入、输出设备到一个FPGA芯片,并且用这些器件实现一个电路。

我们将用DE2开发板上的switches SW17-0作为输入,用LED和7-segm ent displays作为输出。

完成DE2 实验练习1(Digital Logic)对与初学者来说是一个比较大的实验。

我估计,每天要花几小时才能完成。

这个实验包括6个部分,主要是组合逻辑电路和使用assign语句。

Part I :第一次使用assign语句Altera 的DE2开发板有18个拨动开关(toggle switch)和18个红色的LED。

Part I非常简单,在实验手册里首先介绍了Verilog的格式,并给出了代码。

需要自己做的部分就是把代码粘贴到Quartus II然后运行。

当你拨动一个开关(比如Switch 1),对应的LED就会亮(比如LEDR1),这部分在实验手册里解释的很详细。

Part 1代码:1/*23(C) yf.x 2010 /45Filename : part1.v67Compiler : Quartus II 9.1 Web Edition89Description : Demo how to use Switch and led1011Release : 03/05/2010 1.01213 */1415//Simple module that conects the SW switchs to the LEDR lights1617module part1(SW,LEDR);1819input [17:0] SW; //toggle switches2021output [17:0] LEDR; //red leds2223assign LEDR=SW;2425endmodulePart II:设计一个8位的2选1多路选择器用Verilog设计一个多路选择器有很多种方法。

※※※※※中断※※※※※百度百科上对“中断”的定义:在计算机执行期间,系统内发生任何非寻常的或非预期的急需处理事件,使得CPU暂时中断当前正在执行的程序而转去执行相应的时间处理程序。

待处理完毕后又返回原来被中断处继续执行或调度新的进程执行的过程。

翻译成白话:有客人要来你家做客,你正在洗菜做饭,你怎么知道客人已经到了呢?有两种办法,一是让客人到了之后按门铃,另一种是你不断地去门口瞧瞧人有没来到。

对应到nios系统中,CPU即“你”,硬件外设即“客人”,硬件有数据更新(“客人”到了),第一种方式称为“硬件中断”(按门铃),第二种方式“轮询”(你在厨房和大门口之间疲于奔命)。

只是作一个比喻而已,没人会傻到痴痴地坐门口等人,但是硬件系统不分傻与不傻,“轮询”也是一种可行的方式,效率低一些罢了。

前面说过,硬件外设将中断请求传到CPU,必须走avalon总线,因此avalon总线得分配一个接口信号负责中断请求的传送,这个信号的名字为irq。

Nios II CPU体系架构支持32个外部硬件中断:irq0~irq31,中断号越低,优先级越高。

我们来看看一个硬件外设-- 电平开关,在以前那个工程DE2_SEG7中加入4位pio组件,当电平开关的值发生改变时,发送一个中断信号给CPU,让CPU跳到中断处理函数--将4位电平开关的值输出到数码管显示。

<1> 加入PIO组件,位宽为4,即4个电平开关这是SOPC组件列表,注意划红圈的地方,多了个中断号irq0<3> Generate "Nios2_system",在Quartus II里分配电平开关引脚SW[0]~SW[3],编译。

接着打开工程目录下的pio.vhd,可以看到pio控制器确实定义有avalon中断信号irq。

<4> 下面打开Nios II IDE,写软件C语言在哪里?2008-03-13 16:55按照Altera的文档,软硬件之间的过渡部分应该是这个样子:上次没把"C语言标准库"算进去,是想另开一篇文章来说,而且上次写那几行程序确实没用到C标准库里的函数,altera_avalon_seg7_×××是我们自己定义的,不算数。

FPGA设计与应用实验指导书实验一Quartus II开发软件入门一、实验目的1. 熟悉Quartus II 开发软件的基本使用方法2. 掌握用VHDL语言设计组合逻辑电路的方法二、实验内容1. 运用Quartus II 开发软件,完成工程创建、代码编写、程序调试、编译仿真等基本操作。

2. 用VHDL语言设计实现一个3-8译码器,并进行功能仿真验证。

三、实验步骤1.Quartus II 开发软件基本操作(1)创建工程在File菜单下选择New Project Wizard…如图1-1所示。

图1-1 创建工程示意图弹出创建工程选框,选择工程的工作路径,输入工程名称。

如图1-2所示。

注意工程名称的格式要求,同时工程名称默认和顶层实体名称相同,不允许修改。

图1-2 创建工程名称可选择添加已有的程序文件,如图1-3所示。

这里不添加,直接下一步。

图1-3 添加文件选框选择芯片系列和芯片型号,如图1-4所示。

实验中使用的是Altera公司的Cyclone II系列FPGA 芯片,型号为EP2C35F672C6。

如果不进行硬件下载,可直接下一步。

图1-4 芯片参数选框EDA外部工具选框如图1-5所示。

一般选择默认值,直接下一步。

图1-5 EDA外部工具选框完成工程设置后的工程信息如图1-6所示。

图1-6 工程信息选框至此完成工程的创建。

(2)新建VHDL文件在File菜单下选择New选项,如图7所示。

图1-7新建文件示意图点击新建菜单后给出新建文件选框如图1-8所示。

选择VHDL File项创建VHDL文件。

图1-8 新建VHDL文件选框确定后弹出新建VHDL文件编辑窗口如图1-9所示。

可在窗口中编写程序内容并保存,注意文件名称与工程实体名称必须一致。

图1-9 VHDL文件编辑窗口至此完成VHDL文件的创建和VHDL程序的编写。

(3) 程序编译程序编写完成后,选择Processing菜单下的编译工具(Compiler Tool)菜单,如图1-10所示,调出编译工具。

DE2 教学开发板感谢您使用 Altera DE 教学开发板。

这块板子的着眼于为在数字逻辑,计算机组织和FPGA 方面的学习提供一个理想的工具。

它在硬件和CAD 工具上应用先进的技术为学生和专业人员展示了一个宽广的主题。

该板具有多种特点,非常适合各大学课程在实验室环境下的一系列设计项目和非常复杂尖端的数字系统的开发和应用。

Altera 公司为DE2 板提供了一套支持文件,例如学习指导,现成的教学实验练习和丰富的插图说明。

DE2 的特点DE2 板是以CycloneII 2C35FPGA为特点的672 针引脚的包装。

板上所有重要的部件都与板上的芯片相连,使用户能够控制板上各种的操作。

DE2 板包括了很多开关(兼有拨动开关和按键),发光二极管和七段数码管。

在更多进一步的实验中还用到了SRAM,SDRAM,Flash以及16×2的字符液晶。

需要进行处理器和I/O接口试验时,可以简单的用Altera NiosII处理器和象RS-232和PS/2标准接口。

进行涉及音频和视频的实验时,也有标准MIC、line-in、line-out接口(24位音频解编码器),video-in(TV Decoder)和VGA(10-bit DAC),这些特点都能够被用来制作CD质量的音频应用程序和专业的视频图象。

为了能够设计更强大的项目,DE2 还提供了USB2.0 接口(包括主、从USB),10/100M自适应以太网,红外(IRDA)接口,以及SD卡接口。

最后,可以通过两排扩展I/O口与其它用户自定义的板子相连。

支持材料软件拥有DE2开发板的特征的QUARTUS II网络版的CAD系统,以及NiosII嵌入式处理器,也为学生和师提供了该板的一些帮助文件,如使用说明和应用实例。

传统的FPGA 教学开发板的制造商提供了大量的的硬件和软件CAD工具支持,但极少提供直接面向教学目的的帮助文件。

但Altera 公司的DE2 板别树一帜,除了DE2 板的硬件和软件外,Aletra 公司也为一些典型的逻辑设计课程和计算机组织提供了全套的能够在实验室条件下实现的实验练习。