VHDL管脚分配

- 格式:docx

- 大小:11.28 KB

- 文档页数:2

Vivado管脚分配方式1. 简介Vivado是Xilinx公司开发的一款集成化开发环境(IDE),用于设计、验证和实现FPGA(现场可编程门阵列)和SoC(片上系统)的硬件。

在使用Vivado进行FPGA设计时,管脚分配是一个非常重要的环节。

本文将详细介绍Vivado中的管脚分配方式,包括手动分配和自动分配两种方式。

2. 手动分配手动分配是一种通过用户手动指定管脚与设计中的信号进行连接的方式。

在Vivado中,可以通过以下步骤进行手动分配:2.1 打开约束文件在Vivado项目中,约束文件(constraint file)用于指定管脚分配和时序约束等信息。

首先,需要在Vivado中打开约束文件,可以使用Vivado自带的编辑器或者其他文本编辑器打开。

2.2 定义管脚在约束文件中,可以使用set_property命令来定义管脚。

例如,下面的代码定义了一个输入管脚input_pin和一个输出管脚output_pin:set_property PACKAGE_PIN P5 [get_ports input_pin]set_property PACKAGE_PIN P6 [get_ports output_pin]其中,PACKAGE_PIN表示管脚的物理位置,get_ports用于获取设计中的信号。

2.3 连接信号在定义了管脚之后,可以使用set_property命令将管脚与设计中的信号进行连接。

例如,下面的代码将输入管脚input_pin与设计中的信号input_signal进行连接:set_property IOSTANDARD LVCMOS33 [get_ports input_pin]set_property IOBUF_DELAY "IFD" [get_pins input_signal]其中,IOSTANDARD用于指定管脚的电平标准,IOBUF_DELAY用于设置输入缓冲的延迟。

摘要随着微电子技术的发展,现场可编程逻辑门阵列FPGA(Field Programmable Gate Array)可以实现数字电路系统设计的功能。

尤其现场可编程逻辑门阵列FPGA具有集成度高的优点,受到工程界高度的重视。

I2C 总线以接口简单,成本底,可扩展性好在数字系统中得到了广泛的应用。

硬件描述语言是数字系统高层设计的核心,是实现数字系统设计新方法的关键技术之一。

本课题正是利用VHDL语言在FPGA上实现I2C总线控制器的功能。

首先研究了I2C总线的规范,又简要介绍了QuartusⅡ设计环境以及FPGA 的设计流程。

在此基础上,重点介绍了I2C控制器的总体设计方案,以及在QuartusⅡ平台上的时序仿真。

关键词Quartus II;I2C总线控制器;现场可编程逻辑门阵列;时序仿真- I -AbstractWith the development of micro electric and EDA(electronic design automation)technology, FPGA(field programmable gates array) can realize the function of digital circuit system design .FPGA have the merit of filed programmability and High integration rate ,therefore is highly recognized for engineering.I2C bus is widely applied in the digital system as simple interface ,expedient use ,low cost and good expansibility .VHDL is considered as a core of digital system design and a key technique of implement digital system.The design realizes the function of I2C bus interface on the FPGA .At first the thesis deeply research I2C bus specification ,then briefly introduce the Quartus II design environment and the design method ,as well as FPGA design flow .In this foundation,I2C bus controller design scheme and the timing simulation under Quartus II is particularly introduced.Key words Quartus II;I2C bus controller ;FPGA ;timing simulation- II -目录摘要 (I)Abstract .................................................................................................................. I I 第1章绪论.. (5)1.1 课题背景 (5)1.2 I2C总线的产生及发展 (6)1.3 FPGA的现状与展望 (6)1.4 相关工作 (6)第2章 I2C总线技术的研究 (8)2.1 I2C总线的概念 (8)2.2 I2C总线的传输 (9)2.2.1 数据的有效性 (9)2.2.2 I2C总线数据传送的开始和停止条件 (9)2.2.3 I2C总线传输过程中的应答信号 (10)2.2.4 I2C总线数据传送的重复开始条件 (11)2.2.5 I2C总线的传输过程中的字节格式 (11)2.2.6 I2C总线的器件子地址 (11)2.2.7 I2C总线传输信号的时序 (12)2.3 本章小结 (14)第3章 VHDL语言的基础知识 (15)3.1 VHDL语言的概述 (15)3.2 VHDL语言的特点 (15)3.3 VHDL语言的程序结构 (16)3.3.1 VHDL程序的库 (16)3.3.2 包集合 (16)3.3.3 实体说明 (17)3.3.4 构造体 (18)3.3.5 配置 (18)3.4 本章小结 (18)第4章设计工具和设计方法 (19)4.1 设计工具 (19)- III -4.2 基于FPGA的数字电路的设计流程 (20)4.3 本章小结 (21)第5章 I2C总线的功能设计 (23)5.1 I2C总线完成的功能 (23)5.2 用VHDL语言实现写操作时的串行转并行 (24)5.3 用VHDL语言实现顺序读操作时的并行转串行 (24)5.4 I2C总线控制器的顶层设计 (25)5.5 本章小结 (26)第6章 I2C总线的硬件时序仿真 (27)6.1 器件的选择 (27)6.2 硬件仿真 (28)6.2.1 用VHDL语言实现写字节周期 (29)6.2.1 用VHDL语言实现顺序读字节周期 (30)6.2.3 用VHDL语言实现选择性读字节周期 (30)6.3 本章小结 (31)结论 (32)致谢 (33)参考文献 (34)- IV -第1章绪论1.1 课题背景近年来,随着社会的发展,电子产品越来越多的进入人们的生活和工作中,成为了我们生活中必不可少的一部分,随着计算机的普及,以及电子设备之间相互沟通的更加频繁,为了更方便的实现器件与器件之间的通信,研发人员从消费者电子、电讯和工业电子中许多看上去不相关的设计中寻找到了他们的相似之处,例如几乎每个系统都包括:(1)一些智能控制,通常是一个单片的微控制器。

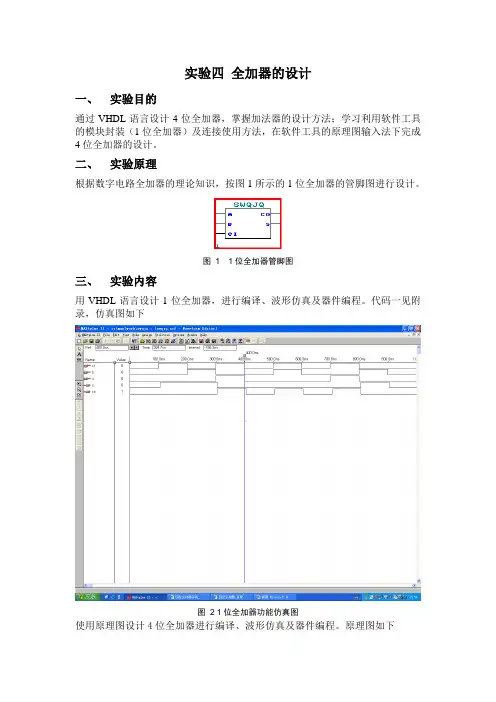

实验四全加器的设计一、实验目的通过VHDL语言设计4位全加器,掌握加法器的设计方法;学习利用软件工具的模块封装(1位全加器)及连接使用方法,在软件工具的原理图输入法下完成4位全加器的设计。

二、实验原理根据数字电路全加器的理论知识,按图1所示的1位全加器的管脚图进行设计。

图 1 1位全加器管脚图三、实验内容用VHDL语言设计1位全加器,进行编译、波形仿真及器件编程。

代码一见附录,仿真图如下图 2 1位全加器功能仿真图使用原理图设计4位全加器进行编译、波形仿真及器件编程。

原理图如下仿真图如下用VHDL语言设计4位全加器,进行编译、波形仿真及器件编程,代码二见附录,仿真图如下图 5 4位全加器功能仿真图附录代码一、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity swqjq isport (a,b:in std_logic;ci:in std_logic;co:out std_logic;s:out std_logic);end swqjq;architecture zhang of swqjq isbeginprocess (a,b,ci)beginif(a='0'and b='0'and ci='0') thens<='0';co<='0';elsif(a='1'and b='0'and ci='0') thens<='1';co<='0';elsif(a='0'and b='1'and ci='0') thens<='1';co<='0';elsif(a='1'and b='1'and ci='0') thens<='0';co<='1';elsif(a='0'and b='0'and ci='1') thens<='1';co<='0';elsif(a='0'and b='1'and ci='1') thens<='0';co<='1';elsif(a='1'and b='0'and ci='1') thens<='0';co<='1';elses<='1';co<='1';end if;end process;end zhang;代码二、library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport ( ci:in std_logic;a,b:in std_logic_vector(3 downto 0);s:out std_logic_vector(3 downto 0);co:out std_logic);end adder4b;architecture zhang of adder4b issignal sint:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0); beginaa<='0'&a(3 downto 0);bb<='0'&b(3 downto 0);sint<=aa+bb+ci;s(3 downto 0)<=sint(3 downto 0);co<=sint(4);end zhang;。

第二种:建立TCL文件进行管脚分配。

这种方法比较灵活,是比较常用的。

这种方法具有分配灵活,方便快捷,可重用性等多方面优点。

方法如下:选择Projects菜单项,并选择Generate tcl file for project选项,系统会为你自动生成相应文件,然后你只要向其中添加你的分配内容就可以了。

还有一种方法就是直接用new ,新建一个TCL文件即可,具体不再细讲。

下面是我分配的内容一部分,可供大家参考。

set_global_assignment -name FAMILY Cycloneset_global_assignment -name DEVICE EP1C3T144C8set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:14:58 JANUARY 06, 2009"set_global_assignment -name LAST_QUARTUS_VERSION 8.0set_global_assignment -nameUSE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_ideda_palaceset_global_assignment -name DEVICE_FILTER_PACKAGE "ANY QFP" set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region"set_global_assignment -name LL_MEMBER_STATE LOCKED-section_id "Root Region"set_global_assignment -name DEVICE_FILTER_PIN_COUNT 144 set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8 set_global_assignment -name FITTER_EFFORT "STANDARD FIT" set_global_assignment -name BDF_FILE topDesign.bdfset_global_assignment -name QIP_FILE nios.qipset_global_assignment -name QIP_FILE altpll0.qipset_global_assignment -name USE_CONFIGURATION_DEVICE ON set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL"set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Topset_global_assignment -name PARTITION_COLOR 14622752-section_id Topset_location_assignment PIN_72 -to addr[7]set_location_assignment PIN_69 -to addr[6]set_location_assignment PIN_70 -to addr[5]set_location_assignment PIN_67 -to addr[4]set_location_assignment PIN_68 -to addr[3]set_location_assignment PIN_42 -to addr[2]set_location_assignment PIN_39 -to addr[1]set_location_assignment PIN_40 -to addr[0]set_location_assignment PIN_48 -to data[15]set_location_assignment PIN_47 -to data[14]set_location_assignment PIN_50 -to data[13]set_location_assignment PIN_49 -to data[12]set_location_assignment PIN_56 -to data[11]set_location_assignment PIN_55 -to data[10]set_location_assignment PIN_58 -to data[9]set_location_assignment PIN_57 -to data[8]set_location_assignment PIN_61 -to data[7]set_location_assignment PIN_62 -to data[6]set_location_assignment PIN_59 -to data[5]set_location_assignment PIN_60 -to data[4]set_location_assignment PIN_53 -to data[3]set_location_assignment PIN_54 -to data[2]set_location_assignment PIN_51 -to data[1]set_location_assignment PIN_52 -to data[0]set_location_assignment PIN_16 -to clkset_location_assignment PIN_38 -to csset_location_assignment PIN_141 -to led[3]set_location_assignment PIN_142 -to led[2]set_location_assignment PIN_143 -to led[1]set_location_assignment PIN_144 -to led[0]set_location_assignment PIN_33 -to reset_nset_location_assignment PIN_41 -to rdset_location_assignment PIN_71 -to wrset_location_assignment PIN_105 -to mosiset_location_assignment PIN_107 -to sclkset_location_assignment PIN_106 -to ssset_location_assignment PIN_73 -to motor[0]set_location_assignment PIN_74 -to motor[1]set_location_assignment PIN_75 -to motor[2]set_location_assignment PIN_76 -to motor[3]set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top# Commit assignmentsexport_assignmentsFPGA 点滴(2008-09-30 09:44:45)转载标签:杂谈以此记录心得以及重要的知识点。

湖北民族学院信息工程学院实验报告(电气、电子类专业用)班级: 09 姓名:周鹏学号:030940908 实验成绩:实验地点: EDA实验室课程名称:数字系统分析与设计实验类型:设计型实验题目:实验一简单的QUARTUSII实例设计,基于VHDL格雷码编码器的设计实验仪器:HH-SOC-EP3C40EDA/SOPC实验开发平台,PC机。

一、实验目的1、通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

2、初步了解QUARTUSII原理图输入设计的全过程。

3、掌握组合逻辑电路的静态测试方法。

4、了解格雷码变换的原理。

5、进一步熟悉QUARTUSII软件的使用方法和VHDL输入的全过程。

6、进一步掌握实验系统的使用。

二、实验原理、原理图及电路图3-8译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

其真值表如表1-1所示输入输出A B C D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0表1-1 三-八译码器真值表译码器不需要像编码器那样用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目:4B5B编码器学生姓名:指导老师:一、实验内容4B/5B编码是百兆以太网中线路层编码类型之一,该试验需要实现用5bit的二进制数来表示4bit二进制数。

二、实验要求1、功能性要求:能够实现4B5B编码,即输入4bit数据时能输出正确的5bit编码结果.2、算法要求:利用卡诺图对编码真值表进行化简,得出其逻辑表达式,并基于此进行硬件设计.3、设计性要求:使用代码及原理图两种设计方式来进行设计.采用基本门结构化描述。

能够编写Test Bench文件,并利用Modelsim进行仿真。

三、实验原理及设计思路1、实验原理:在IEEE 802。

9a等时以太网标准中的4B:5B编码方案,因其效率高和容易实现而被采用。

这种编码的特点是将欲发送的数据流每4bit作为一个组,然后按照4B/5B编码规则将其转换成相应5bit码。

5bit码共有32种组合,但只采用其中的16种对应4bit码的16种,其他的16种或者未用或者用作控制码,以表示帧的开始和结束、光纤线路的状态(静止、空闲、暂停)等.4B5B编码表如下:2、设计思路:(1)整体思路:对已知的编码真值表,首先利用卡诺图对其进行化简,得出其逻辑表达式,再用基本门结构将其实现。

(2)卡诺图与表达式:设输入的4位编码为:ABCD,输出的5位编码为:VWXYZ,则分别画出其卡诺图并得出表达式如下:1.V:V=A+B'D’+B’C2。

W:W=B+A’C’X=C+A'B’D'4.Y:Y=A’B+AB'+C’D’+AC’Z=D(3)基本门结构设计:由上述表达式可见,用到的基本门有:非门、2输入与门、3输入与门、2输入或门、3输入或门、4输入或门,用not、and、or将其一一表示出即可.四、程序设计1、顶层模块:library IEEE;use IEEE。

《FPGA系统设计与开发》课程设计报告题目:七人表决器专业:电子信息工程专业学号:姓名:指导老师:一、实验目的1、熟悉V HDL 的编程。

2、熟悉七人表决器的工作原理。

3、进一步了解实验系统的硬件结构。

二、实验原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个拨动开关来表示七个人,分别用7个LED等来反应每个人的决定,当对应的拨动开关输入为‘1’时,表示此人同意,LED灯点亮;否则若拨动开关输入为‘0’,则表示此人反对,LED灯不亮。

表决的结果也用一个LED表示,若表决的结果为同意,则L ED 被点亮;否则,如果表决的结果为反对,则L ED 不会被点亮。

同时,数码管上显示通过的票数。

三、实验内容本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

拨动开关模块中的K1~K7表示七个人,当拨动开关输入为‘1’时,表示对应的人投同意票,对应的LED灯亮;否则当拨动开关输入为‘0’时,表示对应的人投反对票,对应的LED灯不亮;LED 模块中 LED1 表示七人表决的结果,当 LED1 点亮时,表示此行为通过表决;否则当 LED1 熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

四、实验步骤1、打开Q UARTUSII 软件,新建一个工程。

2、建完工程之后,再新建一个V HDL File,打开V HDL 编辑器对话框。

3、按照实验原理和自己的想法,在V HDL 编辑窗口编写V HDL 程序。

4、编写完V HDL 程序后,保存起来,并建立工程。

5、 对自己编写的 V HDL 程序进行编译并仿真,对程序的错误进行修改。

6、 编译仿真无误后,依照拨动开关、LED 、数码管与 FPGA 的管脚连接表或参照附录进行管脚分配。

管脚分配的原理以管脚分配的原理为标题,本文将详细介绍管脚分配的原理及其应用。

一、管脚分配的概念及作用在电子设备中,管脚(Pin)是指连接芯片和其他组件的接口,用于传输信号和电源。

管脚分配是指将芯片上的不同功能信号连接到不同的管脚上,以实现芯片的正常工作。

管脚分配的准确性和合理性是电子设备设计中至关重要的一环。

管脚分配的原理基于芯片内部不同功能信号的特性和需求,通过设计电路板的布局和连接方式,将这些信号正确地引出并连接到相应的管脚上。

在进行管脚分配时,需要考虑以下几个方面:1. 信号的类型:不同的信号类型需要连接到不同的管脚上。

例如,电源信号需要连接到电源管脚上,数据信号需要连接到数据管脚上。

2. 信号的频率和带宽:高频信号和宽带信号对信号传输的要求更高,需要采用较短的线路和较低的阻抗,以减小信号的损耗和干扰。

3. 信号的电压和电流:不同的信号可能需要不同的电压和电流进行传输和驱动。

因此,在进行管脚分配时,需要根据信号的特性选择合适的管脚和连接方式。

4. 信号的引脚布局:芯片上的引脚布局不同,可能会影响管脚分配的布局和方式。

在进行管脚分配时,需要考虑芯片上的引脚排列和布局,以便更好地进行信号的传输和连接。

三、管脚分配的应用管脚分配在电子设备设计中起到至关重要的作用,它直接影响着设备的性能和功能。

以下是几个常见的应用场景:1. 微控制器:在微控制器设计中,管脚分配用于连接各种输入输出设备,如按键、LED灯、LCD屏幕等。

通过合理的管脚分配,可以实现微控制器与外部设备的正常通信和控制。

2. FPGA:在FPGA(Field Programmable Gate Array)设计中,管脚分配用于连接逻辑门和其他组件,实现特定的功能和逻辑运算。

合理的管脚分配可以提高FPGA的运算速度和资源利用率。

3. 集成电路:在集成电路设计中,管脚分配用于连接芯片内部的各种功能模块,如存储器、处理器、输入输出接口等。

通过合理的管脚分配,可以实现芯片各功能模块之间的正常通信和协作。

专用集成电路实验报告13050Z011305024237X德文实验一开发平台软件安装与认知实验实验内容1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

源程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Unment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive ponents.--library UNISIM;--use UNISIM.Vponents.all;entity ls74138 isPort ( g1 : in std_logic;g2 : in std_logic;inp : in std_logic_vector(2 downto 0);y : out std_logic_vector(7 downto 0));end ls74138;architecture Behavioral of ls74138 isbeginprocess(g1,g2,inp)beginif((g1 and g2)='1') thencase inp iswhen "000"=>y<="00000001";when "001"=>y<="00000010";when "010"=>y<="00000100";when "011"=>y<="00001000";when "100"=>y<="00010000";when "101"=>y<="00100000";when "110"=>y<="01000000";when "111"=>y<="10000000";when others=>y<="00000000";end case;elsey<="00000000";end if;end process;end Behavioral;波形文件:生成元器件及连接电路思考:有程序可以看出,定义了三个输入端,一个输出端。

电子课程设计——简易洗衣机控制器设计学院:班级:姓名:学号:指导老师:2013年12月目录第一部分:设计任务与要求 (1)第二部分:总体框图 (1)第三部分:选择器件 (2)第四部分:功能模块 (3)4.1时间预置编码寄存模块(settime) (3)4.2减法计数器模块(counter) (4)4.3数码管显示模块(showtime) (7)4.4时序电路模块(analyse) (9)4.5译码器模块(move)………………………………………1 1 第五部分:总体设计电路图 (13)5.1总体(顶层)设计电路图 (13)5.2顶层文件仿真 (13)5.3管脚分配图 (14)5.4硬件实验效果图 (14)第六部分:课程设计心得体会 (15)简易洗衣机控制器设计一、设计任务与要求设计一个洗衣机洗涤程序控制器,控制洗衣机的电动机按下图所示的规律运转:时间到 用两位数码管预置洗涤时间(分钟数),洗涤过程在送入预置时间后开始运转,洗涤中按倒计时方式对洗涤过程作计时显示,用LED 表示电动机的正、反转,如果定时时间到,则停机并发出音响信号。

二、总体框图RUN REV PAUSEtime_over clkK5 startK6 load K1 K2 K3 K4 各个部分的具体功能描述如下:(一)预设时间和编码电路(settime ):接受用户通过按钮预置的时间信息,编码成八位之后转给减法计数器。

(二)减法计数器电路(counter ):接收编码之后的预置时间信息,向电机运转控制电路传递运行信号,并将预置时间信息和剩余时间信息发给数码管显示电路进行实时显示。

(三)数码管显示电路(showtime ):接收减法计数器电路传来的时间信息,进行实时译码显示。

(四)电机运转时序控制电路(analyse ):接收运行起止信号,安排电机运行状态并编码输出。

(五)译码器(move ):接收电机运行状态信号,译码后实时控制电机的正传、反转和暂停。

实验一用VHDL 设计四人抢答器一、实验目的1.熟悉四人抢答器的工作原理。

2.加深对VHDL语言的理解。

3.掌握EDA开发的基本流程。

二、实验设备1.PC机一台;2.Altera Blaster下载缆线一台;3.THGSC-2实验箱一台。

三、实验原理抢答器在各类竞赛性质的场合得到了广泛的应用,它的出现,消除了原来由于人眼的误差而未能正确判断最先抢答的人的情况。

抢答器的原理比较简单,首先必须设置一个抢答允许标志位,目的就是为了允许或者禁止抢答者按按钮;如果抢答允许位有效,那么第一个抢答者按下的按钮就将其清楚,同时记录按钮的序号,也就是对应的按按钮的人,这样做的目的是为了禁止后面再有人按下按钮的情况。

总的说来,抢答器的实现就是在抢答允许位有效后,第一个按下按钮的人将其清除以禁止再有按钮按下,同时记录清楚抢答允许位的按钮的序号并显示出来,这就是抢答器的实现原理。

四、实验内容本实验的任务是设计一个四人抢答器,用按键模块的SW5 来作抢答允许按钮,用SW1~SW4 来表示1~4 号抢答者,同时用LED 模块的D4~D7 分别表示于抢答者对应的位子。

具体要求为:按下SW5 一次,允许一次抢答,这时SW1~SW4 中第一个按下的按键将抢答允许位清除,同时将对应的LED 点亮,用来表示对应的按键抢答成功。

数码管显示对应抢答成功者的号码。

此实验中数码管、LED、按键开关与FPGA 的连接电路和管脚连接在附录中都做了详细说明。

五、实验步骤1.打开QUARTUSII 软件,新建一个工程。

2.建完工程之后,再新建一个VHDL File,打开VHDL 编辑器对话框。

3.按照实验原理和自己的想法,在VHDL 编辑窗口编写VHDL 程序,用户可参照光盘中提供的示例程序。

4.编写完VHDL 程序后,保存起来。

方法同实验一。

5.对自己编写的VHDL 程序进行编译并仿真,对程序的错误进行修改。

6.编译仿真无误后,依照附录进行管脚分配。

实验五电压表实验1.设计过程:按照“建立项目文件”--“新建VHDL源文件”--“配置管脚”--“编译下载”--“芯片测试”的顺序。

原理图:1.FPGA的系统时钟来自于小脚丫FPGA开发板配置的24MHz时钟晶振,连接FPGA的C1引脚。

2.实验借助FPGA底板自带的ADC模块,具体信息如下:ADC模块的功能时实现模拟信号转换数字信号,主要包含P1(测试点)、Radj1(10K的可调电位器)和U3(8位串行模数转换器ADC081S)。

在不外接其他信号的情况下,旋转电位计,ADC081S的输入电压在0到3.3V之间变化,通过模数转换实现ADC的采样,原理图连接如图所示:3.实验思路如下:1.根据ADC模块的时序图,完成将ADC模块和FPGA引脚连接起来。

时序图如下:2. 根据程序的框图把完整的程序写出来,显示模块和译码模块利用以前写过的进行例化使用。

以下是程序的框图:VHDL 汇编语言如下: 2.总代码: library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;entity dianyabiao is port( clk: in std_logic;--定义输入和输出 sda: in std_logic; sclk: buffer std_logic; cs: out std_logic; sdata: out std_logic; sck: out std_logic; rck: out std_logic );end dianyabiao;architecture one of dianyabiao is component led_573 --例化port( rst: in std_logic; clk_t_in : in std_logic; sdata: out std_logic; H: in std_logic; ledcode1,ledcode2,ledcode3,ledcode4: in std_logic_vector(6 downto 0); dot: in std_logic_vector(3 downto 0);sda sck cssck: out std_logic;rck: out std_logic);end component;component seg7coderport(data_in: in integer range 0 to 15;seg7_out: out std_logic_vector(6 downto 0));end component;signal ad_phase: integer range 0 to 19;signal clk_t_in: std_logic;signal ad_clk: std_logic;signal ad_out:std_logic_vector(7 downto 0);signal ad:std_logic_vector(7 downto 0);signal data_in1:integer range 0 to 15;signal data_in2:integer range 0 to 15;signal seg1,seg2: std_logic_vector(6 downto 0); --七段码beginu1:seg7coderport map(data_in => data_in1,seg7_out => seg1);u2:seg7coderport map(data_in => data_in2,seg7_out => seg2);u3:led_573port map(rst=>'1',clk_t_in => clk,H => '1',dot => "0000",ledcode1 => seg1,ledcode2 => seg2,ledcode3 =>"1111110",ledcode4 =>"1111110",sdata => sdata,sck => sck,rck => rck);--得到分频时钟,50-20000khz的分频process(clk)variable divcnt: integer range 0 to 1000;beginif clk'event and clk='1' thenif divcnt=1000 thendivcnt:=0;clk_t_in<=not clk_t_in;elsedivcnt:=divcnt+1;clk_t_in<=clk_t_in;end if;end if;end process;--ad模快process(clk_t_in)-- ad_clk<=clk_t_in;beginif clk_t_in'event and clk_t_in = '1' thensclk<=not sclk;if sclk='1' thenif ad_phase = 19 thenad_phase<=0;elsead_phase<=ad_phase+1;end if;end if;if sclk='0' and ad_phase>16 then --保证cs的值cs<='1';elsecs<='0';end if;if ad_phase=3 and sclk='0' then --值的输出ad(7)<=sda;end if;if ad_phase=4 and sclk='0' thenad(6)<=sda;end if;if ad_phase=5 and sclk='0' thenad(5)<=sda;end if;if ad_phase=6 and sclk='0' thenad(4)<=sda;end if;if ad_phase=7 and sclk='0' thenad(3)<=sda;end if;if ad_phase=8 and sclk='0' thenad(2)<=sda;end if;if ad_phase=9 and sclk='0' thenad(1)<=sda;end if;if ad_phase=10 and sclk='0' thenad(0)<=sda;end if;if ad_phase=11 and sclk='0' thenad_out<=ad;end if;end if;end process;process(ad_out) --完成将ad_out的八位输出转化成两位16进制的数begincase ad_out(3 downto 0) is--when "0000"=>data_in1<=0;when "0001"=>data_in1<=1;when "0010"=>data_in1<=2;when "0011"=>data_in1<=3;when "0100"=>data_in1<=4;when "0101"=>data_in1<=5;when "0110"=>data_in1<=6;when "0111"=>data_in1<=7; when "1000"=>data_in1<=8; when "1001"=>data_in1<=9; when "1010"=>data_in1<=10; when "1011"=>data_in1<=11; when "1100"=>data_in1<=12; when "1101"=>data_in1<=13; when "1110"=>data_in1<=14; when "1111"=>data_in1<=15; end case;case ad_out(7 downto 4) is when "0000"=>data_in2<=0; when "0001"=>data_in2<=1; when "0010"=>data_in2<=2; when "0011"=>data_in2<=3; when "0100"=>data_in2<=4; when "0101"=>data_in2<=5; when "0110"=>data_in2<=6; when "0111"=>data_in2<=7; when "1000"=>data_in2<=8; when "1001"=>data_in2<=9; when "1010"=>data_in2<=10; when "1011"=>data_in2<=11; when "1100"=>data_in2<=12; when "1101"=>data_in2<=13; when "1110"=>data_in2<=14; when "1111"=>data_in2<=15; end case;end process;end architecture;3.管脚分配:4.实验现象:旋转电压旋钮,电压从00变化到FF,现象如下面所示:。