读时

使SA两侧 虚单元 的信号差

一侧的 相同则 位线电

平始终

为VR

VR=1/2(Vs1+Vs0),若使Vs1、Vs0分别为VDD和GND则VR选为1/2VDD

BL1 BL2 BL3 BL4

位线的布置 SA的布置

开式位线 Open bitlines 折叠位线 Folded bitlines

BL1 BL2 BL3 BL4

电位下降。

在两侧位线上形成电位差

读‘1’>0 读‘0’<0 为提高速度并不等一侧位线下降为 低电平,而是只要位线间建立一定 的信号差就送读出放大器,放大输 出。

需要灵敏放大器,不用再生

SRAM写操作

SRAM写0

写操作时,选中单元WL为高,M5,M6导通。位线BL,!BL准备好 待写入的信号。写1,BL=1=VDD,写0, BL=0。 BL、!BL通过M6、M5对Q、!Q强迫充放电,与单元内原先存储的 状态无关。 写操作结束后,双稳单元将信息保存。

第十章 存储器设计

第一节 简介 第二节 动态随机存储器 DRAM 第三节 静态随机存储器 SRAM 第四节 只读存储器ROM 第五节 非易失存储器 NVM

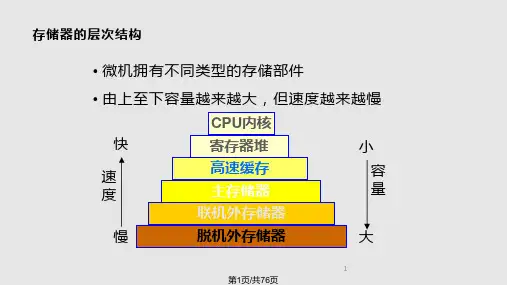

第一节 简介

一、存储器的分类 二、存储器的总体结构 三、存储器的时序

一、存储器的分类

随机存取存储器 RAM Random Access Memory

SA越灵敏,可分辩的信号差越 小,抗干扰能力越差,各种干 扰引起的信号差也会被放大- 避免干扰

要求SA中的器件对称,否则灵 敏度下降,器件参数对称

VBL>V!BL

VBL最后稳定在( VDD)SAP

V!BL最后稳定在 (GND)SAN

VBL<V!BL