基本RS触发器

- 格式:doc

- 大小:112.00 KB

- 文档页数:3

RS 触发器及其应用触发器(flip flop)是构成时序逻辑电路的基本单元,能记忆、存储一位二进制信息,触发器也称双稳态触发器,它有两种稳定输出工作状态,即分别输出1和输出0的状态。

在无输入信号作用时,这种状态是稳定的;而当输入信号到来并满足一定逻辑关系时,输出端的状态将迅速变化,能从一种稳定状态转换到另一种稳定状态。

测试如下电路,调整S1开关状态,观察LED1和LED2的变化,并建立真值表。

图8.1测试电路(multisim)【信息单】 一、基本RS 触发器1.“与非”门构成的基本触发器基本的RS 触发器又称为置0置1触发器。

它是各种触发器中结构最简单的一种,通常作为构成各种功能触发器的最基本单元,所以也称为基本触发器。

⑴电路结构基本的RS 触发器由两个与非门的输入端与输出端交叉连接而成。

电路结构如图8.3(a )所示,逻辑符号如图8.3(b )所示。

图中Q 、Q 是基本RS 触发器两个输出端;S 、R 是两个输入端,S 、R 上的“非”号或R 、S 上的小圆圈都表示输入信号只在低电平时有效。

Q 端状态通常定义为触发器的输出状态。

当0=Q 、Q =1,称触发器为0状态,当1=Q 、Q =0,称触发器为1状态。

Q 、Q 状态相反。

Q G 1G 2QS RQQ(a )电路结构 (b )逻辑符号 图8.3 与非门构成的基本RS 触发器⑵逻辑功能S =1、R =0时,Q =1,反馈到G 1门使0=Q ,即不论触发器原态是0态还是1态,电路的输出一定为0态,R 为置0端。

S =0、R =1时,Q =1,反馈到G 2门使Q =0,即不论触发器原态是0态还是1态,电路的输出一定为1态,S 为置1端。

S =1、R =1时,设电路原来状态为0=Q 、Q =1,在S =1、R =1作用下,电路的输出仍是0=Q 、Q =1与原态相同,即触发器的状态保持不变。

S =0、R =0时,Q =1、Q =1,破坏了输出信号互补的原则,而随后S =1、R =1时,输出状态可能是1也可能是0,出现了不定状态,这意味着当输入条件同时消失后,触发器状态不定,这在触发器工作时是不允许出现的,也就是要禁止S 、R 同时为0的输入状态出现。

RS触发器基本RS 触发器:电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R、S和两个输出端Q、Q。

工作原理基本RS触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R=1、S=0时,则Q=0,Q=1,触发器置1。

2.当R=0、S=1时,则Q=1,Q=0,触发器置0。

如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q 有两种互补的稳定状态。

一般规定触发器Q端的状态作为触发器的状态。

通常称触发器处于某种状态,实际是指它的Q端的状态。

Q=1、Q=0时,称触发器处于1态,反之触发器处于0态。

S=0,R=1使触发器置1,或称置位。

因置位的决定条件是S=0,故称S 端为置1端。

R=0,S=1时,使触发器置0,或称复位。

同理,称R端为置0端或复位端。

若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变0,S端的电平由0变1。

这里所加的输入信号(低电平)称为触发信号,由它们导致的转换过程称为翻转。

由于这里的触发信号是电平,因此这种触发器称为电平控制触发器。

从功能方面看,它只能在S和R的作用下置0和置1,所以又称为置0置1触发器,或称为置位复位触发器。

其逻辑符号如图7.2.1(b)所示。

由于置0或置1都是触发信号低电平有效,因此,S端和R 端都画有小圆圈。

3.当R=S=1时,触发器状态保持不变。

触发器保持状态时,输入端都加非有效电平(高电平),需要触发翻转时,要求在某一输入端加一负脉冲,例如在S端加负脉冲使触发器置1,该脉冲信号回到高电平后,触发器仍维持1状态不变,相当于把S端某一时刻的电平信号存储起来,这体现了触发器具有记忆功能。

4.当R=S=0时,触发器状态不确定在此条件下,两个与非门的输出端Q和Q全为1,在两个输入信号都同时撤去(回到1)后,由于两个与非门的延迟时间无法确定,触发器的状态不能确定是1还是0,因此称这种情况为不定状态,这种情况应当避免。

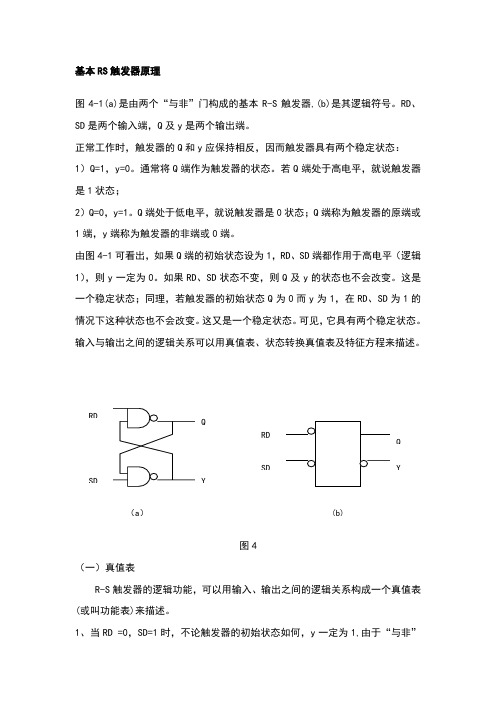

基本RS 触发器原理图4-1(a)是由两个“与非”门构成的基本R-S 触发器,(b)是其逻辑符号。

RD 、SD 是两个输入端,Q 及y 是两个输出端。

正常工作时,触发器的Q 和y 应保持相反,因而触发器具有两个稳定状态:1)Q=1,y=0。

通常将Q 端作为触发器的状态。

若Q 端处于高电平,就说触发器是1状态;2)Q=0,y=1。

Q 端处于低电平,就说触发器是0状态;Q 端称为触发器的原端或1端,y 端称为触发器的非端或0端。

由图4-1可看出,如果Q 端的初始状态设为1,RD 、SD 端都作用于高电平(逻辑1),则y 一定为0。

如果RD 、SD 状态不变,则Q 及y 的状态也不会改变。

这是一个稳定状态;同理,若触发器的初始状态Q 为0而y 为1,在RD 、SD 为1的情况下这种状态也不会改变。

这又是一个稳定状态。

可见,它具有两个稳定状态。

输入与输出之间的逻辑关系可以用真值表、状态转换真值表及特征方程来描述。

图4(一)真值表R-S 触发器的逻辑功能,可以用输入、输出之间的逻辑关系构成一个真值表(或叫功能表)来描述。

1、当RD =0,SD=1时,不论触发器的初始状态如何,y 一定为1,由于“与非”门2的输入全是1,Q 端应为0。

称触发器为0状态,RD 为置0端。

2、当RD =1,SD=0时,不论触发器的初始状态如何,Q 一定为1,从而使y 为0。

称触发器为1状态,SD 置1端。

3、当RD =1,SD =1时,如前所述,Q 及y 状态保持原状态不变。

4、当RD =0,SD =0时,不论触发器的初始状态如何,Q=y=1,若RD 、SD 同时由0变成1,在两个门的性能完全一致的情况下, Q 及y 哪一个为1,哪一个为0是不定的,在应用时不允许RD 和SD 同时为0。

综合以上四种情况,可建立R-S 触发器的真值表于表1。

应注意的是表中RD = SD =0的一行中Q 及y 状态是指RD 、SD 同时变为1后所处的状态是不定的,用Ф表示。

基本RS触发器实验第5章基本RS触发器5.同步触发器(同步RS触发器)⽬的与要求:1 掌握时序电路的定义、分类、触发器的特点。

2 掌握基本RS触发器的电路结构、⼯作原理、逻辑功能。

3 掌握同步RS触发器的⼯作原理、逻辑功能。

4 掌握触发器逻辑功能的表⽰⽅法。

5 掌握时序电路的⼀些基本概念。

重点与难点:1 基本概念要正确建⽴。

难点:现态、次态、不定状态的正确理解。

2 基本RS触发器的逻辑功能、触发⽅式。

5.1概述⼀、触发器的概念复习:组合电路的定义?构成其电路的门电路有何特点?组合电路与时序电路的区别?门电路:在某⼀时刻的输出信号完全取决于该时刻的输⼊信号,没有记忆作⽤。

触发器:具有记忆功能的基本逻辑电路,能存储⼆进制信息(数字信息)。

触发器有三个基本特性:(1)有两个稳态,可分别表⽰⼆进制数码0和1,⽆外触发时可维持稳态;(2)外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆⼆进制信息,常⽤作⼆进制存储单元。

(3)有两个互补输出端,分别⽤Q和Q⼆、触发器的逻辑功能描述:特性表、激励表(⼜称驱动表)、特性⽅程、状态转换图和波形图(⼜称时序图)三、触发器的分类:根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和触发器等。

触发⽅式不同:电平触发器、边沿触发器和主从触发器等。

电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器等。

5.2 触发器的基本形式5.2.1 基本RS触发器⼀、由与⾮门组成的基本RS触发器1.电路结构电路组成:两个与⾮门输⼊和输出交叉耦合(反馈延时)。

逻辑图如图(a)所⽰。

逻辑符号如图(b)所⽰。

与⾮门组成的基本RS触发器的特性表⼆、由或⾮门组成的基本RS触发器电路构成:两个或⾮门的输⼊和输出交叉耦合⽽成,如下图所⽰。

逻辑符号:图(b)所⽰。

⼯作原理在与⾮门实现的基本RS触发器的基础上稍作变化。

或⾮门组成的基本RS触发器的特性表5.2.2 同步触发器基本RS触发器的触发⽅式:端的输⼊信号直接控制。

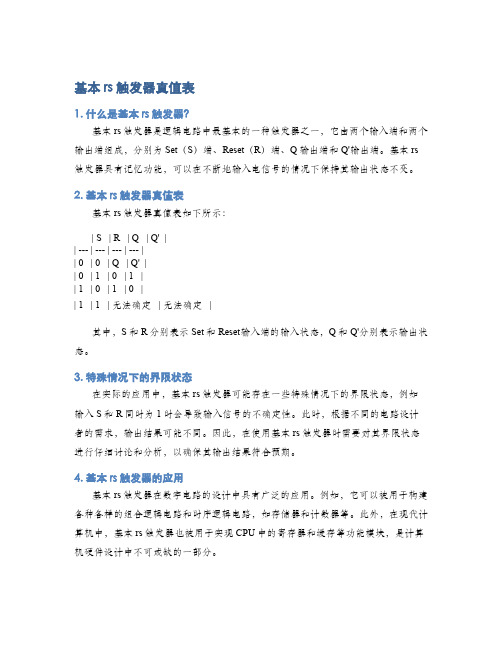

基本rs触发器真值表1. 什么是基本rs触发器?基本rs触发器是逻辑电路中最基本的一种触发器之一,它由两个输入端和两个输出端组成,分别为Set(S)端、Reset(R)端、Q输出端和Q'输出端。

基本rs 触发器具有记忆功能,可以在不断地输入电信号的情况下保持其输出状态不变。

2. 基本rs触发器真值表基本rs触发器真值表如下所示:| S | R | Q | Q' || --- | --- | --- | --- || 0 | 0 | Q | Q' || 0 | 1 | 0 | 1 || 1 | 0 | 1 | 0 || 1 | 1 | 无法确定 | 无法确定 |其中,S和R分别表示Set和Reset输入端的输入状态,Q和Q'分别表示输出状态。

3. 特殊情况下的界限状态在实际的应用中,基本rs触发器可能存在一些特殊情况下的界限状态,例如输入S和R同时为1时会导致输入信号的不确定性。

此时,根据不同的电路设计者的需求,输出结果可能不同。

因此,在使用基本rs触发器时需要对其界限状态进行仔细讨论和分析,以确保其输出结果符合预期。

4. 基本rs触发器的应用基本rs触发器在数字电路的设计中具有广泛的应用。

例如,它可以被用于构建各种各样的组合逻辑电路和时序逻辑电路,如存储器和计数器等。

此外,在现代计算机中,基本rs触发器也被用于实现CPU中的寄存器和缓存等功能模块,是计算机硬件设计中不可或缺的一部分。

5. 总结基本rs触发器作为最基本的逻辑电路之一,具有广泛的应用和重要的意义。

虽然其在理论和实践中存在一些特殊情况下的界限状态,但通过仔细的讨论和分析,设计者可以确保其输出结果达到预期。

基本rs触发器的特征方程

基本RS触发器是一种基本的数字电路元件,由两个反向并联的

门组成。

当S(设置)输入为高电平(1)时,Q输出为高电平(1),而Q'输出为低电平(0)。

当R(复位)输入为高电平(1)时,Q

输出为低电平(0),而Q'输出为高电平(1)。

换句话说,当S输

入为1时,触发器被置位,Q输出为1;当R输入为1时,触发器被

复位,Q输出为0。

特征方程描述了触发器的动态行为,它是一个关

于触发器输入和输出的方程。

对于基本RS触发器,其特征方程可以表示为:

Q(t+1) = S + Q'(t)。

Q'(t+1) = R + Q(t)。

其中,Q(t)和Q'(t)分别表示时刻t的Q和Q'输出状态,Q(t+1)和Q'(t+1)分别表示时刻t+1的Q和Q'输出状态,S表示设置输入,R表示复位输入。

特征方程描述了当前时刻的输出状态如何受到当

前时刻的输入和上一个时刻的输出状态的影响。

从特征方程可以看出,基本RS触发器的输出取决于当前的输入和上一个时刻的输出状态,这使得特征方程成为分析和设计数字电路时非常重要的工具。

特征方程的形式可以帮助工程师理解触发器的行为,并且可以用于分析触发器在数字系统中的稳定性和性能。