8基本RS触发器解析

- 格式:ppt

- 大小:689.50 KB

- 文档页数:48

基本rs触发器的逻辑功能、构成、逻辑状态表、逻辑符号————————————————————————————————作者:————————————————————————————————日期:基本rs触发器的逻辑功能、构成、逻辑状态表、逻辑符号将两个与非门的输出端、输入端相互交叉连接,就构成了基本R-S触发器,如下图所示。

正常工作时输出端Q和的逻辑状态相反。

通常用Q端的状态来表示触发器的状态,当Q=0时称触发器为0态或复位状态,Q=1时称触发器为1态或置位状态。

下面分四种情况来讨论触发器的逻辑功能。

(1)RD=1,SD=1。

设触发器处于0态,即Q=0,=1。

根据触发器的逻辑电路图,此时Q=0反馈到门G2的输入端,从而保证了=1;而=1反馈到门G1的输入端,与SD=1共同作用,又保证了Q=0。

因此触发器仍保持了原来的0态。

设触发器处于1态,即Q=1、=0。

=0反馈到门G1的输入端,从而保证了Q=1;而Q=1反馈到门G2的输入端,与RD=1共同作用,又保证了=0。

因此触发器仍保持了原来的1态。

可见,无论原状态为0还是为1,当RD和SD均为高电平时,触发器具有保持原状态的功能,也说明触发器具有记忆0或1的功能。

正因如此,触发器可以用来存放一位二进制数。

(2)RD=0,SD=1。

当RD =0时,无论触发器原来的状态如何,都有=1;这时门G1的两输入端都为1,则有Q=0,所以触发器置为0态。

触发器置0后,无论RD变为1或仍为0,只要SD保持高电平(SD =1),触发器保持0态。

也即无论原状态如何,只要SD保持高电平,RD端加负脉冲或低电平,都能使触发器置0,因而RD端称为置0端或复位端。

(3)RD=1,SD=0。

因SD=0,无论的状态如何,都有Q=1;所以,触发器被置为1态。

一旦触发器被置为1态之后,只要保持RD =1不变,即使SD由0跳变为1,触发器仍保持1态。

SD端称为置1端或置位端。

(4)RD=0,SD=0。

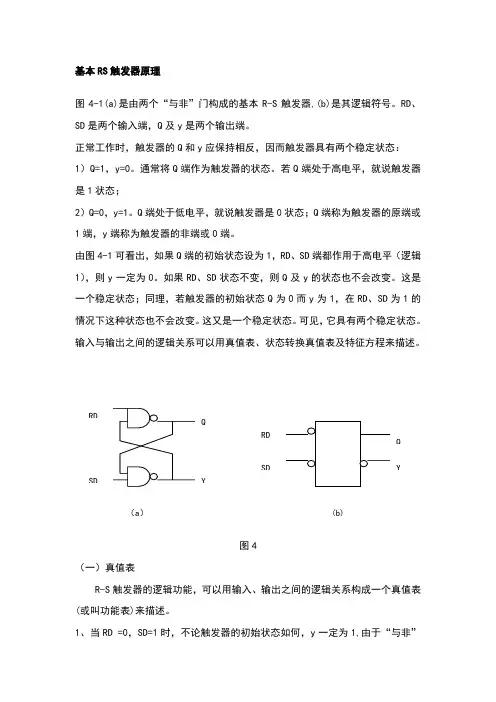

基本RS 触发器原理图4-1(a)是由两个“与非”门构成的基本R-S 触发器,(b)是其逻辑符号。

RD 、SD 是两个输入端,Q 及y 是两个输出端。

正常工作时,触发器的Q 和y 应保持相反,因而触发器具有两个稳定状态:1)Q=1,y=0。

通常将Q 端作为触发器的状态。

若Q 端处于高电平,就说触发器是1状态;2)Q=0,y=1。

Q 端处于低电平,就说触发器是0状态;Q 端称为触发器的原端或1端,y 端称为触发器的非端或0端。

由图4-1可看出,如果Q 端的初始状态设为1,RD 、SD 端都作用于高电平(逻辑1),则y 一定为0。

如果RD 、SD 状态不变,则Q 及y 的状态也不会改变。

这是一个稳定状态;同理,若触发器的初始状态Q 为0而y 为1,在RD 、SD 为1的情况下这种状态也不会改变。

这又是一个稳定状态。

可见,它具有两个稳定状态。

输入与输出之间的逻辑关系可以用真值表、状态转换真值表及特征方程来描述。

图4(一)真值表R-S 触发器的逻辑功能,可以用输入、输出之间的逻辑关系构成一个真值表(或叫功能表)来描述。

1、当RD =0,SD=1时,不论触发器的初始状态如何,y 一定为1,由于“与非”门2的输入全是1,Q 端应为0。

称触发器为0状态,RD 为置0端。

2、当RD =1,SD=0时,不论触发器的初始状态如何,Q 一定为1,从而使y 为0。

称触发器为1状态,SD 置1端。

3、当RD =1,SD =1时,如前所述,Q 及y 状态保持原状态不变。

4、当RD =0,SD =0时,不论触发器的初始状态如何,Q=y=1,若RD 、SD 同时由0变成1,在两个门的性能完全一致的情况下, Q 及y 哪一个为1,哪一个为0是不定的,在应用时不允许RD 和SD 同时为0。

综合以上四种情况,可建立R-S 触发器的真值表于表1。

应注意的是表中RD = SD =0的一行中Q 及y 状态是指RD 、SD 同时变为1后所处的状态是不定的,用Ф表示。

基本rs触发器的逻辑功能、构成、逻辑状态表、逻辑符号————————————————————————————————作者:————————————————————————————————日期:基本rs触发器的逻辑功能、构成、逻辑状态表、逻辑符号将两个与非门的输出端、输入端相互交叉连接,就构成了基本R-S触发器,如下图所示。

正常工作时输出端Q和的逻辑状态相反。

通常用Q端的状态来表示触发器的状态,当Q=0时称触发器为0态或复位状态,Q=1时称触发器为1态或置位状态。

下面分四种情况来讨论触发器的逻辑功能。

(1)RD=1,SD=1。

设触发器处于0态,即Q=0,=1。

根据触发器的逻辑电路图,此时Q=0反馈到门G2的输入端,从而保证了=1;而=1反馈到门G1的输入端,与SD=1共同作用,又保证了Q=0。

因此触发器仍保持了原来的0态。

设触发器处于1态,即Q=1、=0。

=0反馈到门G1的输入端,从而保证了Q=1;而Q=1反馈到门G2的输入端,与RD=1共同作用,又保证了=0。

因此触发器仍保持了原来的1态。

可见,无论原状态为0还是为1,当RD和SD均为高电平时,触发器具有保持原状态的功能,也说明触发器具有记忆0或1的功能。

正因如此,触发器可以用来存放一位二进制数。

(2)RD=0,SD=1。

当RD =0时,无论触发器原来的状态如何,都有=1;这时门G1的两输入端都为1,则有Q=0,所以触发器置为0态。

触发器置0后,无论RD变为1或仍为0,只要SD保持高电平(SD =1),触发器保持0态。

也即无论原状态如何,只要SD保持高电平,RD端加负脉冲或低电平,都能使触发器置0,因而RD端称为置0端或复位端。

(3)RD=1,SD=0。

因SD=0,无论的状态如何,都有Q=1;所以,触发器被置为1态。

一旦触发器被置为1态之后,只要保持RD =1不变,即使SD由0跳变为1,触发器仍保持1态。

SD端称为置1端或置位端。

(4)RD=0,SD=0。

基本触发器的设计预备知识:RS触发器是一种基本的触发器一触发器1触发器的概念触发器:具有记忆功能的基本逻辑电路,能存储二进制信息(数字信息)。

触发器有二个基本特性:( 1 )有两个稳态,可分别表示二进制数码 0 和 1 ,无外触发时可维持稳态;触发器的两个稳定状态①Q=1,通常将Q端作为触发器的状态。

若Q端处于高电平,就说触发器是1状态;②Q=0,Q端处于低电平,就说触发器是0状态;Q端称为触发器的原端或1端,端称为触发器的非端或0端。

( 2 )外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆二进制信息,常用作二进制存储单元。

(3 )触发器的分类:根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和触发器等。

触发方式不同:电平触发器、边沿触发器和主从触发器等。

电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器。

二、RS触发器的知识1 基本RS触发器原理图2-1是由两个“与非”门构成的基本R-S触发器。

RD、SD是两个输入端,Q及Qn是两个输出端。

图2-1 RS触发器2 稳定状态正常工作时,触发器的Q 和Qn 应保持相反,因而触发器具有两个稳定状态:① Q=1,Qn=0。

通常将Q 端作为触发器的状态。

若Q 端处于高电平,就说触发器是1状态; ② Q=0,Qn=1。

Q 端处于低电平,就说触发器是0状态;Q 端称为触发器的原端或1端,Qn 端称为触发器的非端或0端。

3 真值表R-S 触发器的逻辑功能,可以用输入、输出之间的逻辑关系构成一个真值表(或叫功能表)来描述。

① 当RD=0,SD=1时,不论触发器的初始状态如何,Qn 为1,由于“与非”门2的输入全是1,Q 端应为0。

称触发器为状态,R D 为置0端② 当RD =1,SD =0时,不论触发器的初始状态如何,Q 为1,从而使Qn 为0。

称触发器为1状态,SD 置1端。

1.实验目的1)使用EWB软件模拟基本RS触发器,本实验选用或非门实现基本RS触发器,完成仿真调试,电路分析;2)进一步分析并掌握RS触发器的工作原理;3)基本RS触发器(又称R-S锁存器)是各种触发电路中结构形式最简单的一种,它又是许多复杂电路结构触发器的一个组成部分。

2.实验内容1)利用EWB电子实验室软件多媒体教程,学习如何使用EWB模拟出基本RS触发器;2)自己使用EWB模拟RS触发器,以此完成元器件的选取,电路连接,仿真调试以及电路分析;3)进一步分析RS触发器的功能,分析其工作原理。

3.实验步骤和实验结果1)选取元器件:地,“V CC”直流电源,开关2个,彩色指示器2个以及或非门两个。

2)根据电子多媒体教程连接电路:3)仿真调试:R = 1, S = 1, 触发器两端为低电平R = 1, S = 0, 触发器置1R = 0, S = 1, 触发器置0R = 0, S = 0, 触发器保持原状态4)结果分析:该实验使用的是或非门构造的RS触发器,所以Q___所对应的为R___+___Q___,而Q所对应为S+Q___,所以由分析可得该模拟电路中RS高电平有效。

而该触发器中S为置位端,而R 为复位端或指令端。

由上图仿真调试结构可得RS不同的取值下,输出信号的五种不同结果。

4.分析与讨论1)本RS基本触发器电路与书上所给逻辑电路图有所不同,即Q与Q——的位置互相对调,所以在输出上结果也相应的有所不同,如当R=0,S=0,情况下,触发器Q与Q——端口保持原状态而不是低电平;2)3)由真值表可得其特性方程为:Q n+1=R+S—Q nRS=04)基本RS触发器因为电平受直接控制,所以抗干扰能力弱,并且RS间有约束,所以可以采用同步触发器改善电路。