实验五 D触发器 功能测试及其应用

- 格式:ppt

- 大小:187.50 KB

- 文档页数:12

触发器实验报告引言:触发器是数字电路中常见的基本组件之一,它能够存储和转换电信号,广泛应用于各种电子设备和系统中。

本实验旨在通过实际操作,深入理解触发器的工作原理和应用。

实验原理:触发器是一种双稳态电路,能够固定保存输入信号的状态。

常见的触发器包括RS触发器、D触发器、JK触发器等。

本实验将以D触发器为例进行演示。

实验步骤:1. 准备实验器材:D触发器芯片、电源、示波器以及适配器等。

2. 连接电路:将D触发器芯片插入适配器,并按照实验电路图连接相关引脚。

3. 提供输入信号:通过开关或信号源向D触发器提供输入信号。

4. 观察输出信号:使用示波器监测D触发器的输出信号,并记录相关数据。

5. 测量实验数据:改变输入信号的频率和幅值,测量触发器的输出变化,并记录数据。

6. 分析实验结果:根据观察到的数据,分析D触发器的工作原理和特性。

实验结果与分析:通过实验观察和实际数据记录,我们可以得出以下结论:1. D触发器具有边沿触发和电平触发两种模式。

在边沿触发模式下,触发器仅在输入信号上升沿(或下降沿)时才进行状态转换;而在电平触发模式下,输入信号处于高电平(或低电平)时触发器状态保持不变。

2. D触发器的输出状态受到输入信号和时钟信号的控制。

输入信号为逻辑高电平时,若时钟信号为上升沿触发,则输出信号将与上一时钟周期的输入信号一致;若时钟信号为下降沿触发,则输出信号将与上一时钟周期的输入信号相反。

3. 改变输入信号的频率和幅值,我们发现触发器的输出信号频率和幅值也发生了相应的变化。

当输入信号频率较低时,触发器能够稳定存储和输出输入信号;而当输入信号频率较高时,触发器可能无法及时反应输入信号的状态变化,导致输出信号不准确。

实验应用:触发器作为数字电路中的重要组件,在现代电子技术中有着广泛的应用:1. 存储器芯片中广泛使用的触发器技术,使得计算机能够对数据进行有效地存储和读取。

2. 触发器在时序电路中的应用,能够实现时钟同步、状态变化检测等功能。

实验五移存器功能测试及应用一、实验目的1、熟悉移位寄存器(移存器)的电路结构和工作原理。

2、掌握D触发器74HC(LS)74及集成移位寄存器74HC(LS)194的逻辑功能和使用方法。

二、实验设备和器件1、数字逻辑电路实验板1块2、74HC(LS)74(双D触发器)2片3、74HC(LS)194(4位双向通用移位寄存器)2片三、实验原理移位寄存器是具有移位功能的寄存器,其中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

移位寄存器存取信息的方式分为:串入串出、串入并出、并入串出、并入并出四种形式。

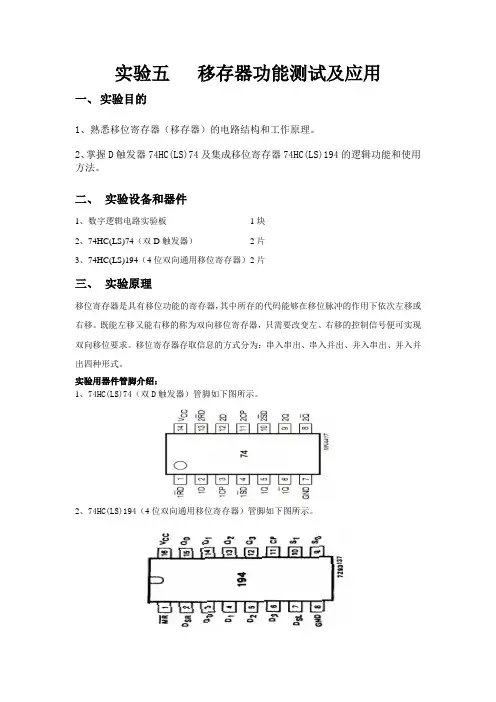

实验用器件管脚介绍:1、74HC(LS)74(双D触发器)管脚如下图所示。

2、74HC(LS)194(4位双向通用移位寄存器)管脚如下图所示。

四、实验内容与步骤1、利用两块74HC(LS)74(四个D触发器)构成一个单向的移位寄存器(基本命题)参照用两块74HC(LS)74(四个D触发器)构成一个单向移位寄存器的实验电路图连接电路,Q输出依次接LED指示灯,加电后在移位输入端加入不同信号观察LED指示灯变化。

1.1电路图1.2实验结果LED灯依次变亮,每次间隔一个CP。

2、测试74HC(LS)194的功能(基本命题)例如,Q输出依次接LED指示灯,改变S1、S0的值配合其它输入观察LED的变化。

2.1电路图2.2实验结果:置数:LED显示状态与置数端相同。

左移:LED从下往上(QD到QA)依次变亮,每次间隔一个CP右移:LED从上往下(QA到QD)依次变亮,每次间隔一个CP3、用两片74HC(LS)194做出模16的扭环计数器(扩展命题)将两片的Q输出依次都接到LED指示灯上,加电并加CP观察LED的变化。

现象一般为八盏灯先依次变暗再依次变亮如此循环。

3.1电路图3.2计数器拓展当进行M=2n 偶数计数时,可采用扭环型,D1=Q n ̅̅̅̅,将Q n 和高电平与非后反馈至第一片的输入端。

触发器实验报告一、实验目的本次实验的主要目的是深入了解和掌握触发器的工作原理、功能特点以及其在数字电路中的应用。

通过实际操作和观察,提高对触发器逻辑功能的理解和运用能力,为进一步学习数字电路的相关知识打下坚实的基础。

二、实验设备与器材1、数字电路实验箱2、双踪示波器3、集成电路芯片:74LS74(D 触发器)、74LS112(JK 触发器)4、若干导线三、实验原理(一)D 触发器D 触发器是一种在时钟脉冲上升沿或下降沿触发的触发器,其逻辑功能为:当 D 端输入为 1 时,在时钟脉冲的作用下,输出 Q 变为 1;当 D 端输入为 0 时,在时钟脉冲的作用下,输出 Q 变为 0。

其逻辑表达式为:Q(n+1) = D。

(二)JK 触发器JK 触发器也是一种在时钟脉冲上升沿或下降沿触发的触发器,具有置 0、置 1、保持和翻转四种功能。

当 J=1、K=0 时,在时钟脉冲作用下,输出 Q 置 1;当 J=0、K=1 时,在时钟脉冲作用下,输出 Q 置 0;当 J=K=0 时,输出保持不变;当 J=K=1 时,输出翻转。

其逻辑表达式为:Q(n+1) = JQ' + K'Q。

四、实验内容与步骤(一)D 触发器实验1、按照实验电路图,在数字电路实验箱上正确连接 74LS74 芯片和其他相关元件。

2、将 D 端分别接高电平(1)和低电平(0),用示波器观察时钟脉冲和输出 Q 的波形,记录实验结果。

3、改变时钟脉冲的频率,观察输出 Q 的变化,分析时钟频率对触发器工作的影响。

(二)JK 触发器实验1、依照实验电路图,在实验箱上连接 74LS112 芯片及相关元件。

2、分别设置 J、K 的不同输入组合,如 J=0、K=0;J=1、K=0;J=0、K=1;J=1、K=1,用示波器观察时钟脉冲和输出 Q 的波形,并做好记录。

3、调整时钟脉冲的占空比,观察输出 Q 的变化,探讨占空比对触发器工作的影响。

五、实验数据与结果分析(一)D 触发器1、当 D 端接高电平时,在时钟脉冲上升沿,输出 Q 变为高电平;当 D 端接低电平时,在时钟脉冲上升沿,输出 Q 变为低电平。

数字电⼦技术实验五触发器及其应⽤(学⽣实验报告)实验三触发器及其应⽤1.实验⽬的(1) 掌握基本RS、JK、D和T触发器的逻辑功能(2) 掌握集成触发器的逻辑功能及使⽤⽅法(3) 熟悉触发器之间相互转换的⽅法2.实验设备与器件(1) +5V直流电源(2) 双踪⽰波器(3) 连续脉冲源(4) 单次脉冲源(5) 逻辑电平开关(6) 逻辑电平显⽰器(7) 74LS112(或CC4027);74LS00(或CC4011);74LS74(或CC4013)3.实验原理触发器具有 2 个稳定状态,⽤以表⽰逻辑状态“1”和“0”,在⼀定的外界信号作⽤下,可以从⼀个稳定状态翻转到另⼀个稳定状态,它是⼀个具有记忆功能的⼆进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

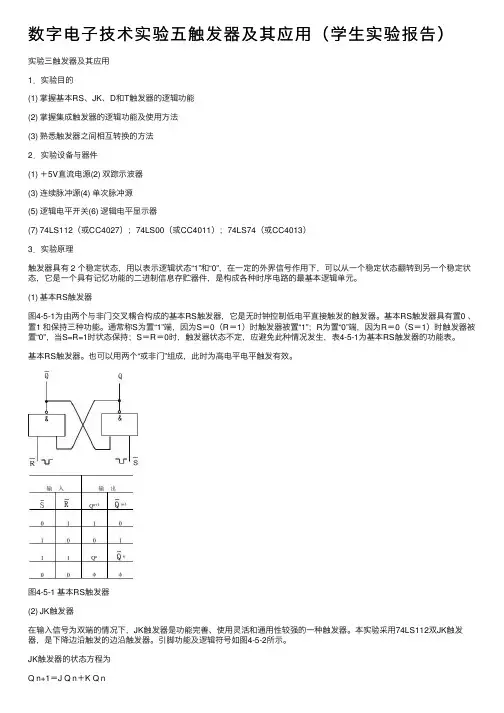

(1) 基本RS触发器图4-5-1为由两个与⾮门交叉耦合构成的基本RS触发器,它是⽆时钟控制低电平直接触发的触发器。

基本RS触发器具有置0 、置1 和保持三种功能。

通常称S为置“1”端,因为S=0(R=1)时触发器被置“1”;R为置“0”端,因为R=0(S=1)时触发器被置“0”,当S=R=1时状态保持;S=R=0时,触发器状态不定,应避免此种情况发⽣,表4-5-1为基本RS触发器的功能表。

基本RS触发器。

也可以⽤两个“或⾮门”组成,此时为⾼电平电平触发有效。

图4-5-1 基本RS触发器(2) JK触发器在输⼊信号为双端的情况下,JK触发器是功能完善、使⽤灵活和通⽤性较强的⼀种触发器。

本实验采⽤74LS112双JK触发器,是下降边沿触发的边沿触发器。

引脚功能及逻辑符号如图4-5-2所⽰。

JK触发器的状态⽅程为Q n+1=J Q n+K Q nJ和K是数据输⼊端,是触发器状态更新的依据,若J、K有两个或两个以上输⼊端时,组成“与”的关系。

Q与Q为两个互补输出端。

通常把 Q=0、Q=1的状态定为触发器0 状态;⽽把Q=1,Q=0定为 1 状态。

图4-5-2 74LS112双JK触发器引脚排列及逻辑符号下降沿触发JK触发器的功能如表4-5-2注:×— 任意态↓— ⾼到低电平跳变↑— 低到⾼电平跳变Q n (Q n )— 现态 Q n+1(Q n+1)— 次态φ— 不定态JK 触发器常被⽤作缓冲存储器,移位寄存器和计数器。

触发器实验报告一、实验目的本次实验的主要目的是深入了解触发器的工作原理和功能,通过实际操作和观察,掌握触发器在数字电路中的应用,以及如何利用触发器实现特定的逻辑功能。

二、实验原理触发器是一种具有存储功能的基本逻辑单元,能够在时钟信号的控制下,根据输入信号的变化改变其输出状态,并保持该状态直到下一个时钟脉冲的到来。

常见的触发器类型包括 D 触发器、JK 触发器、SR 触发器等。

D 触发器是在时钟脉冲上升沿或下降沿时,将输入数据(D 端)传输到输出端(Q 端)。

JK 触发器则根据输入的 J、K 信号和时钟脉冲来决定输出状态的翻转。

SR 触发器则由置位(S)和复位(R)信号控制输出状态。

三、实验设备与材料1、数字电路实验箱2、 74LS74(D 触发器)芯片、74LS112(JK 触发器)芯片、74LS279(SR 触发器)芯片3、示波器4、逻辑笔5、杜邦线若干四、实验内容与步骤1、 D 触发器实验按照实验箱的引脚说明,将 74LS74 芯片正确插入插座。

连接时钟信号源,将其频率设置为适当的值。

将 D 输入端分别接高电平和低电平,用逻辑笔观察 Q 和 Q'输出端的状态变化,并记录在表格中。

使用示波器观察时钟信号和 Q 输出端的波形,分析其关系。

2、 JK 触发器实验插入 74LS112 芯片,按照引脚连接电路。

设置不同的 J、K 输入组合,观察并记录 Q 输出端的状态变化。

同样使用示波器观察相关波形。

3、 SR 触发器实验安装 74LS279 芯片,连接电路。

改变 S、R 输入端的电平,观察 Q 输出端的状态。

五、实验数据记录与分析1、 D 触发器实验数据| D 输入| Q 输出(上升沿)| Q 输出(下降沿)|||||| 0 | 0 | 0 || 1 | 1 | 1 |从数据可以看出,在时钟上升沿或下降沿时,D 触发器能够准确地将 D 输入端的电平传输到 Q 输出端。

2、 JK 触发器实验数据| J | K | Q 输出(上升沿)| Q 输出(下降沿)||||||| 0 | 0 |保持|保持|| 0 | 1 | 0 | 0 || 1 | 0 | 1 | 1 || 1 | 1 |翻转|翻转|分析可知,JK 触发器的输出状态根据 J、K 输入和时钟脉冲的组合进行相应的变化。

实验五--------触发器及应用实验五触发器及应用院系:信息科学与技术学院 专业:电子信息工程姓名:刘晓旭学号:2011117147 一:实验目的1. 掌握RS ,D,JK 触发器的电路结构及其逻辑功能。

2. 学习各种触发器功能的测试及应用方法。

3.掌握触发器的应用。

二:实验器材74LS00四2输入与非门 74LS20二4输入与非门 74LS74双D 正沿触发器 74LS76双JK 触发器蜂鸣器,三极管,电阻若干,示波器,函数信号发生器,稳压电源三:实验内容1. 单次脉冲发生器按照图5.7(a )所示电路接线即构成单次脉冲发生器。

工作时,每按一次按键就从Q 端输出工作脉冲。

波形如图5.7(b )所示。

脉冲宽度T 0取决于开关按下的时间,用双踪示波器同时观察 Q,Q 波形。

图1波形如图(2)图22.测试D 触发器的逻辑功能将D 触发器74LS74的S D ,R D 和D 分别接逻辑开关,CP 接单次脉冲。

Q,Q 接发光二极管,按D 触发器的逻辑功能进行测试,记录测试结果。

按照图示连接电路图3当1D 接高电平时,给电路一个单次脉冲,Q 总是处于高电平; 当1D 接低电平时,给电路一个单次脉冲,Q 总是处于低电平。

满足D 触发器的特性表(1):表13.测试JK 触发器的逻辑功能。

JK 触发器74LS76按图所示的电路连线,用函数发生器输出0~5V 方波信号作图示图4波形如图5:图54,触发器的相互转换 (1) JK 触发器转换成T 触发器,按图(a ),(b)所示连接电路,组成T ,T ’触发器,记录测试结果:图6特性图如表2表2当T=1时,每来一个脉冲信号,,状态就反转一次,而T=0时,cp 信号到达后,它的波形不变波形如图7所示:图7T ’触发器的电路如图8所示:图8波形如图9所示:图9(2) 按照图5.5将D 触发器转换成T 触发器,验证其功能。

电路如图图10波形如图11所示:特性如表2所示。

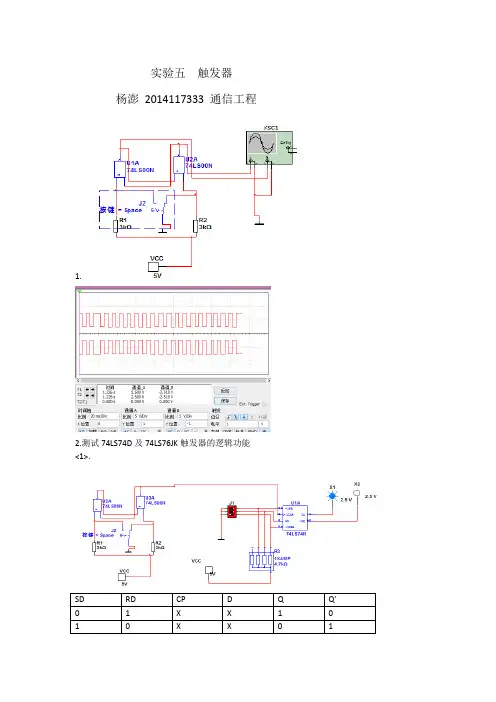

实验五触发器

杨澎2014117333 通信工程

1.

2.测试74LS74D及74LS76JK触发器的逻辑功能

<1>.

SD RD CP D Q Q’

0 1 X X 1 0

1 0 X X 0 1

1 1 ↑ 1 1 0

1 1 ↑0 0 1

1 1 ↓X 保持保持0 0 X X 非法非法

<2>.

.

Cp波形:

Q1,Q2的波形:

3.搭建四人抢答器

要工作,必须给CLK一个上升沿电平,(CLK)高电平时才能使它正常工作.它的内部是由四个门电路组成,D1输入为高电平时,Q1输出为高电平,Q'1为低电平,D2,D3,D4,也是一样如此.,抢答开始,当没有人抢答时,Q1,Q2,Q3,Q4都为低电平,Q'1,Q'2,Q'3,Q'4都为高电平;假如最先抢答的人是二号选手,相应的开关B按下,D2就为高电平,Q2也转换为高电平了,使得三极管Q2导通,数码管点亮显示出二号,表示二号最先抢答;同时二极管D2导通,三极管导通使灯亮,也同时使三极管的基极为高电平,导致三极管截止,从而停止工作.而使得74LS75保持现有的状态;这时第二个人按下开关时也不会改变74LS75的输出状态.直至主持人按下开关时,重新抢答开始.。

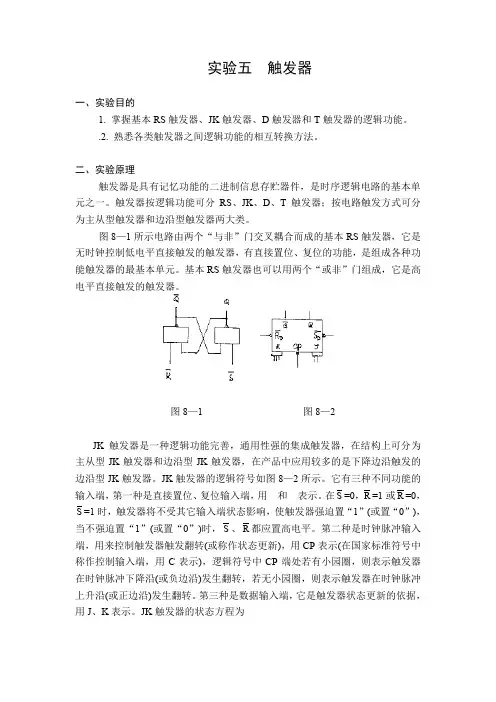

实验五触发器一、实验目的1. 掌握基本RS触发器、JK触发器、D触发器和T触发器的逻辑功能。

.2. 熟悉各类触发器之间逻辑功能的相互转换方法。

二、实验原理触发器是具有记忆功能的二进制信息存贮器件,是时序逻辑电路的基本单元之一。

触发器按逻辑功能可分RS、JK、D、T触发器;按电路触发方式可分为主从型触发器和边沿型触发器两大类。

图8—1所示电路由两个“与非”门交叉耦合而成的基本RS触发器,它是无时钟控制低电平直接触发的触发器,有直接置位、复位的功能,是组成各种功能触发器的最基本单元。

基本RS触发器也可以用两个“或非”门组成,它是高电平直接触发的触发器。

图8—1 图8—2JK触发器是一种逻辑功能完善,通用性强的集成触发器,在结构上可分为主从型JK触发器和边沿型JK触发器,在产品中应用较多的是下降边沿触发的边沿型JK触发器。

JK触发器的逻辑符号如图8—2所示。

它有三种不同功能的输入端,第一种是直接置位、复位输入端,用和表示。

在S=0,R=1或R=0,S=1时,触发器将不受其它输入端状态影响,使触发器强迫置“1”(或置“0”),当不强迫置“1”(或置“0”)时,S、R都应置高电平。

第二种是时钟脉冲输入端,用来控制触发器触发翻转(或称作状态更新),用CP表示(在国家标准符号中称作控制输入端,用C表示),逻辑符号中CP端处若有小园圈,则表示触发器在时钟脉冲下降沿(或负边沿)发生翻转,若无小园圈,则表示触发器在时钟脉冲上升沿(或正边沿)发生翻转。

第三种是数据输入端,它是触发器状态更新的依据,用J、K表示。

JK触发器的状态方程为本实验采用74LS112型双JK 触发器,是下降边沿触发的边沿触发器,引脚排列如图8—3所示。

表8—1为其功能表。

图8—3 图8—4D 触发器是另一种使用广泛的触发器,它的基本结构多为维阻型。

D 触发器的逻辑符号如图8—4所示。

D 触发器是在CP 脉冲上升沿触发翻转,触发器的状态取决于CP 脉冲到来之前D 端的状态,状态方程为Q n+1 =D注: × −− 任意态; ↓ −− 高到低电平跳变 注: ↑ −− 低到高电平跳变 Q n (Q n ) −− 现态; −− 次态 ϕ −− 不定态本实验采用74LS74型双D 触发器, 是上升边沿触发的边沿触发器, 引脚排列如图8—5所示。

触发器实验报告一、实验目的本次实验的主要目的是深入理解触发器的工作原理和功能,通过实际操作和观察,掌握触发器在数字电路中的应用,以及其对信号的存储和转换作用。

二、实验原理触发器是一种具有记忆功能的基本逻辑单元,能够在时钟脉冲的作用下存储二进制数据。

常见的触发器类型包括 D 触发器、JK 触发器和SR 触发器等。

D 触发器在时钟脉冲的上升沿(或下降沿)将输入的数据传送到输出端。

JK 触发器则根据输入的J、K 信号和时钟脉冲来改变输出状态。

SR 触发器则由置位(S)和复位(R)信号控制输出。

三、实验设备与材料1、数字电路实验箱2、示波器3、集成电路芯片(如 74LS74、74LS112 等)4、导线若干四、实验步骤1、 D 触发器实验将 74LS74 芯片插入实验箱的插槽中。

按照芯片引脚图连接电路,将 D 输入端连接到逻辑电平开关,时钟输入端连接到脉冲信号源,输出端 Q 和 Q'连接到发光二极管。

改变D 输入端的电平,观察在时钟脉冲作用下输出端的状态变化。

2、 JK 触发器实验插入 74LS112 芯片。

连接电路,将 J、K 输入端连接到逻辑电平开关,时钟输入端连接到脉冲信号源,输出端连接到发光二极管。

改变 J、K 输入端的电平组合,观察在时钟脉冲作用下输出端的状态变化。

3、 SR 触发器实验选取合适的 SR 触发器芯片,如 74LS279。

按照引脚图连接电路,将 S、R 输入端连接到逻辑电平开关,输出端连接到发光二极管。

改变 S、R 输入端的电平,观察输出端的状态变化。

五、实验结果与分析1、 D 触发器当 D 输入端为高电平时,在时钟脉冲的上升沿,输出端 Q 变为高电平,Q'变为低电平;当D 输入端为低电平时,在时钟脉冲的上升沿,输出端 Q 变为低电平,Q'变为高电平。

这表明 D 触发器能够在时钟脉冲的控制下,将输入的数据准确地传输到输出端。

2、 JK 触发器当 J=1,K=0 时,在时钟脉冲的作用下,输出端 Q 置位为高电平;当 J=0,K=1 时,输出端 Q 复位为低电平;当 J=K=0 时,输出端保持原状态不变;当 J=K=1 时,输出端在时钟脉冲作用下翻转。

实验3.9 D 触发器及应用一、实验目的:1.了解边沿D 触发器的逻辑功能和特点。

2.掌握D 触发器的异步置0和异步置1端的作用。

3.了解用D 触发器组成智力抢答器的工作原理。

二、实验准备:和JK 触发器一样,D 触发器也属主、从触发器,为了实现异步置位、复位功能,D 触发器也设置了异步置位D S 和异步复位D R 端。

和JK 触发器不同的是,D触发器的异步置位D S 和异步复位D R 端是高电平有效,且当CP 信号来到时,上升沿触发。

它的特性表如表3.9.1所示。

表3.9.1:图3.9.1是利用CMOS 传输门构成的一种典型边沿D 触发器内部电路。

从图3.9.1中可以看到,反相器1G 、2G 和传输门1TG 、2TG 组成了主触发器,反相器3G 、4G 和传输门3TG 、4TG 组成了从触发器。

1TG 和3TG 分别为主触发器和从触发器的输入控制门。

当CP = 0、CP =1时,1TG 导通、2TG 截止,D 端的输入信号送人主触发器中,使Q '=D 。

但这时主触发器尚未形成反馈连接,不能自行保持,Q '跟随D 端的状态变化。

同时,由于3TG 截止、4TG 导通,所以从触发器维持原状态不变,而且它与主触发器之间的联系被3TG 所切断。

图3.9.1当CP 的上升沿到达时(即CP 跳变为1、CP 跳变为0),1TG 截止、2TG 导通。

由于门1G 的输入电容存储效应,1G 输入端的电压不会立刻消失,于是Q '在1TG 切断前的状态被保存下来。

同时,由于3TG 导通、4TG 截止,主触发器的状态通过3TG和3G 送到了输出端,使=QQ '=D (CP 上升沿到达时D 的状态)。

可见,这种触发器的动作特点是输出端状态的转换发生在CP 的上升沿,而且触发器所保存下来的状态仅仅取决于CP 上升沿到达时的输入状态。

因为触发器输出端状态的转换发生在CP 的上升沿,所以这是一个上升沿触发边沿触发器。

实验八D触发器及其应用一、实验目的1.熟悉基本D触发器的功能测试;2.了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点;3.熟悉触发器的实际应用;4.了解并掌握Multisim仿真软件的使用。

二、实验设备数字实验电路箱,74LS74,导线若干,Multisim数电仿真软件。

74LS74引脚图74LS74逻辑图三、实验原理D触发器在时钟脉冲CP的前沿(正跳变0到1)发生翻转,触发器的次态取决于脉冲上升沿到来之前D端的状态,即=D。

因此,它具有置0、置1两种功能。

由于CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

和分别是决定触发器初始状态的直接置0、置1端。

当不需要强迫置0、置1时,和端都应置高电平(如接+5V电源)。

74LS74、74LS175等均为上升沿触发的边沿触发器。

触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生器等。

四、实验内容1.测试D触发器的逻辑功能;2.构成异步分频器,构成2分频和4分频;3.构成同步分频器,构成2分频和4分频。

五、实验设计及实验仿真1.测试D 触发器的逻辑功能:(1)将74LS74的D S D R 端分别加低电平,观察并记录Q 端的状态;(2)令D S D R 端为高电平,D 端分别接高、低电平,用单脉冲做CP ,观察记录当CP 为0,上升,1,下降时Q 段状态的变化;(3)当D S D R 为高电平,CP=0(或CP=1),改变D 端状态,观察Q 端的状态是否变化;(4)得到74LS74D 触发器的功能测试表:2.构成计时分频器,构成2分频和4分频:仿真如图所示: 得到实验结果图如图所示:3.构成同步分频器,构成2分频和4分频:仿真如图所示:得到实验结果图如图所示:六、实验思考实验结束后,我们对下述电路进行了验证:完成两位竞赛抢答电路,观察抢答电路的工作情况,分析工作原理。

经过试验可得以下真值表:当主控1Rd=2Rd=0时,1D和2D置1置0都不会亮。

d触发器实验报告D 触发器实验报告一、实验目的本次实验的主要目的是深入理解 D 触发器的工作原理,掌握其逻辑功能和特性,并通过实际操作和测试,学会使用相关仪器设备进行电路搭建和性能分析。

二、实验原理1、 D 触发器的定义与逻辑符号D 触发器是一种具有存储功能的数字电路元件,它能够在时钟脉冲的上升沿或下降沿将输入的数据(D 端)锁存到输出端(Q 端)。

其逻辑符号通常包括数据输入端(D)、时钟输入端(CLK)、输出端(Q 和\(\overline{Q}\))以及置位端(SET)和复位端(RESET)。

2、工作原理当时钟脉冲为低电平时,D 触发器保持原来的状态不变。

当时钟脉冲上升沿到来时,如果 D 端为高电平,则 Q 端输出高电平;如果 D 端为低电平,则 Q 端输出低电平。

3、特性方程\(Q^{n + 1} = D\)(在时钟上升沿时)三、实验仪器与设备1、数字电路实验箱提供电源、逻辑电平输入和输出接口,以及各种数字芯片的插槽。

2、示波器用于观察时钟脉冲和输出信号的波形,以分析电路的工作情况。

3、数字万用表用于测量电路中的电压、电流等参数,检查电路的连接是否正常。

4、 74LS74 双 D 触发器芯片本次实验所使用的核心芯片,具有两个独立的 D 触发器。

四、实验内容及步骤1、电路搭建按照实验原理图,在数字电路实验箱上插入 74LS74 芯片,并使用导线将其与电源、地、时钟脉冲源以及逻辑电平输入和输出端连接起来。

确保电路连接正确无误,避免短路和断路现象。

2、功能测试(1)将 D 端分别接高电平和低电平,观察在时钟脉冲上升沿作用下,Q 端输出的变化情况。

(2)使用示波器同时观察时钟脉冲和 Q 端输出的波形,验证 D 触发器的工作特性。

3、置位和复位功能测试(1)通过置位端(SET)和复位端(RESET)将 D 触发器强制置为高电平或低电平,观察 Q 端的输出状态。

(2)在置位或复位操作后,再次改变 D 端的输入电平,观察在时钟脉冲作用下 Q 端的输出是否受到影响。

班级:08020903 姓名:罗林学号:2009301953实验四触发器及其应用一、实验目的:1)熟悉基本D触发器的功能测试。

2)了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点。

3)熟悉触发器的实际应用。

二、实验设备:1)数字电路实验箱2)函数信号发生器、数字双踪示波器3)数字万用表4)74LS00、74LS74三、实验原理:触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。

触发器具有两个稳定状态,即“0”和“1”,,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。

触发方式有电平触发和边沿触发两种。

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态取决于CP的脉冲上升沿到来之前D端的状态,即=D。

因此,它具有置0、置1两种功能。

由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

和分别是决定触发器初始状态的直接置0、置1端。

当不需要强迫置0、置1时,和端都应置高电平(如接+5V电源)。

74LS74,74LS175等均为上升沿触发的边沿触发器。

图一为74LS74的引脚图和逻辑图。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

74LS74引脚图和逻辑图四、实验内容1.用D触发器构成4分频器四分频电路图:2.设计电路实现如下波形五、实验结果四分频实验结果波形:2.实验结果波形:。

实验四项目名称:触发器及其应用一、实验目的1、了解基本RS、JK和D触发器的逻辑功能2、了解时钟对触发器的触发作用3、能用触发器设计基本的时序逻辑电路二、实验设备1、数字电路实验箱2、74LS112 74LS00 74LS74三、实验内容及步骤1、测试基本RS触发器的逻辑功能本实验是选取74LS00芯片(引脚如图4-7所示)中两个与非门交叉耦合而成,如图4-8所示。

根据图4-8连线,d S、d R端分别接在实验箱上的逻辑电平选择开关上,输出Q和Q分别接在实验箱上的LED电平指示上。

按表4-5选择输入状态,测试并记录结果。

图4-7 74LS00引脚图图4-8 基本RS触发器表4-5d S d R Q Q011110112、JK触发器(1) 测试置位端S D和复位端R D 的功能按表4-6,将74LS112芯片(引脚如图4-9所示)的R D、S D、J、K端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲下降沿触发输出端,Q、Q端分别接至实验箱的LED电平指示上。

根据表4-6,确定R D,S D、J、K端状态,按下单脉冲触发按钮,测试并记录实验结果(表中“×”表示无关项,即可置于任意状态)。

图4-9 74LS112引脚图表4-6(2) 测试JK触发器的逻辑功能按表4-7,测试JK触发器的逻辑功能。

将CP接单脉冲下降沿触发输出端,J、K、R D、S D端分别接逻辑电平选择开关,Q端接在实验箱的LED电平指示上。

利用置位端S D和复位端R D的功能,根据表4-6预置现态Q n ,然后R D 、S D 端同时置“1”,J 、K 状态按表4-7设定。

按下单脉冲触发按钮,测试并记录结果。

表4-73、D 触发器(1) 测试置位端S D 、复位端R D 的功能。

将74LS74芯片(引脚如图4-10所示)的D 、S D 、R D 端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲上升沿触发端输出端,Q 、Q 分别接在实验箱的LED 电平指示上。

试验五D触发器及其运用

试验人员:班号:学号:

一.试验目标

1.熟习D触发器的逻辑功效;

2.控制用D触发器组成分频器的办法;

3.控制简略时序逻辑电路的设计

二.试验装备

74LS00 ,74LS74,数字电路试验箱,数字双踪示波器,函数旌旗灯号产生器

三.试验内容

1.用74LS74(1片)组成二分频器.四分频器,并用示波器不雅察波形;

74LS74是双D触发器(上升沿触发的边沿D触发器),其管脚图如下:

其功效表如下:

○1组成二分频器:用一片74LS74即可组成二分频器.试验电路图如下:

○2组成四分频器:须要用到两片74LS74.试验电路图如下:

2.实现如图所示时序脉冲(用74LS74和74LS00各1片来实现)将欲实现功效列出真值表如下:

00010

经由过程不雅察上面的真值表,可以得出下面的表达式:

衔接电路图如下:

四.试验成果

1.用74LS74(1片)组成二分频器.四分频器.示波器显示波形如下:

○1二分频器:

○2四分频器:

2.实现时序脉冲.示波器显示波形如下:

五.故障消除

在做“用74LS74(1片)组成二分频器.四分频器”时,衔接上示波器后,发明通道二总显示的是相似于电容放电的波形,但表示出了二分频.重复排查询题均没有发明原因.最后换了一根衔接示波器的线,便得到了幻想的成果.

在示波器运用时想要用U盘保管电路波形,不会操纵.后来在讯问了同窗之后才知道只须要按“print”就好.

六.心得领会

经由过程此次试验,我更深刻地融会了触发器的道理和用法,还温习了示波器的用法,还学会了若何保管示波器波形.。