集成触发器(精)

- 格式:ppt

- 大小:2.09 MB

- 文档页数:53

实验三集成触发器的逻辑功能测试一实验目的1.熟悉JK触发器的基本原理及逻辑功能。

2.熟悉D触发器的基本原理及逻辑功能,并掌握其寄存器移位功能。

3.触发器应用。

二、实验仪器及器件仪器:逻辑箱,数字万用表器材:74LS74、74LS76三、实验基本原理JK触发器有J输入端和K输入端,而其R D端和S D端则具有置“0”置“1”功能,逻辑功能如下:Q当J=K=1时,CP脉冲作用下,触发器状态翻转,写成Q n+1=n当J=K=0时,CP脉冲作用下,触发器保持原状态,写成O n+1=Q n。

当J=1,K=0时,在CP脉冲作用下,触发器置“1”,写成Q n+1=1。

当J=0,K=1时,在CP脉冲作用下,触发器置“0”,写成Q n+1=0。

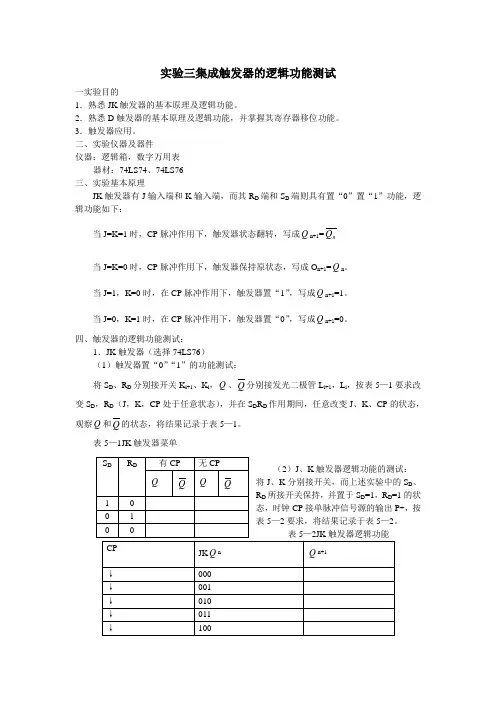

四、触发器的逻辑功能测试:1.JK触发器(选择74LS76)(1)触发器置“0”“1”的功能测试:将S D、R D分别接开关K i+1、K i,Q、Q分别接发光二极管L i+1,L i,按表5—1要求改变S D,R D(J,K,CP处于任意状态),并在S D R D作用期间,任意改变J、K、CP的状态,观察Q和Q的状态,将结果记录于表5—1。

表5—1JK触发器菜单将J、K分别接开关,而上述实验中的S D、R D所接开关保持,并置于S D=1,R D=1的状态,时钟CP接单脉冲信号源的输出P+,按表5—2要求,将结果记录于表5—2。

2.D 触发器:(选择74LS74)(1) 触发器置“0”置“1”功能的测试:将S D 、R D 分别接开关,Q 、Q 分别接发光二极管,按表5—3要求改变S D 、R D (D 及CP 处于任意状态)并在S D 、R D 作用期间,任意改变D 与CP 的状态,测试S D 、RD 的功能,并将测试结果记录于表5—3。

表5—3D 触发器S D 、R D 菜单(2) 对D 触发器逻辑功能的测试,结果记录于表5—4。

表5—触发器逻辑菜单五、触发器应用:1. 用JK 触发器(74LS76)组成三位串行累加计数器如下图。

数字逻辑与数字系统设计实验报告——D、JK触发器与广告流水灯异步时序电路VHDL语言仿真学院电子工程学院班级卓越001012班学号 00101201一.实验目的1.了解集成触发器的工作原理。

2.对Quartus II 软件使用操作有初步的了解,能用该软件进行简单的VHDL语言编程与功能仿真3、掌握VHDL设计实体的基本结构及文字规则。

二.实验仪器1.计算机一台2.万用表一块3.直流稳压电源一台4.数字电路实验板一台(含cyclone—II FPGA芯片)5.数据下载线,JTAG连接线若干三.实验内容用VHDL代码输入的方法设计以下三个电路功能,并进行全程编译,执行功能和时序仿真。

1.用VHDL语言描述D触发器功能。

2.用VHDL语言描述JK触发器功能。

3.用VHDL语言描述以下功能:用双D触发器74LS74和与非门74LS00设计一个广告流水灯同步时序电路,广告流水灯有四个灯,这四个灯始终是一暗三明且暗灯循环右移,其状态图如图5-11所示,图中¤表示灯亮,◎表示灯暗。

四.实验数据记录与处理1. D触发器1)VHDL语言library ieee;use ieee.std_logic_1164.all;entity Dflipflop isport(D,clock :in std_logic;Q :out std_logic);end Dflipflop;architecture behavior of Dflipflop isbeginProcess (clock)beginif clock'event and clock='1' thenQ<=D;end if;end process;end behavior;2)功能仿真建立波形文件,功能仿真结果如下:3)时序仿真建立波形文件,时序仿真结果如下:2.JK触发器1)VHDL语言LIBRARY ieee ;USE ieee.std_logic_1164.all ;ENTITY jkflipflop ISPORT ( Clock : IN STD_LOGIC ;J,K : IN STD_LOGIC ;Q : OUT STD_LOGIC) ;END jkflipflop ;ARCHITECTURE Behavior OF jkflipflop ISSIGNAL Q1: STD_LOGIC ;BEGINPROCESS ( Clock )BEGINIF Clock'EVENT AND Clock = '1' THENQ1 <= (J AND NOT Q1)OR(NOT K AND Q1);END IF ;Q <= Q1;END PROCESS ;END Behavior ;2)功能仿真建立波形文件,功能仿真结果如下3)时序仿真建立波形文件,时序仿真结果如下:3. 广告流水灯1)VHDL语言LIBRARY ieee ;USE ieee.std_logic_1164.all ;ENTITY fd2 ISPORT ( Clock : IN STD_LOGIC ;Q : OUT STD_LOGIC);END fd2 ;ARCHITECTURE Behavior OF fd2 ISSIGNAL D : STD_LOGIC ;BEGINPROCESS ( Clock )BEGINIF Clock'EVENT AND Clock = '1' THEND <= NOT D ;END IF ;Q <= D;END PROCESS ;END Behavior ;LIBRARY ieee ;USE ieee.std_logic_1164.all ;PACKAGE fd2_package ISCOMPONENT fd2PORT ( Clock : IN STD_LOGIC ;Q : OUT STD_LOGIC);END COMPONENT ;END fd2_package;LIBRARY ieee ;USE ieee.std_logic_1164.all ;LIBRARY work ;USE work.fd2_package.all;ENTITY fd4 ISPORT ( Clock : IN STD_LOGIC ;Q0,Q1 : OUT STD_LOGIC); END fd4 ;ARCHITECTURE Structure OF fd4 ISSIGNAL W : STD_LOGIC ;BEGINS0: fd2 PORT MAP( CLOCK, W );Q0 <= W;S1: fd2 PORT MAP( W, Q1 );END Structure ;LIBRARY ieee ;USE ieee.std_logic_1164.all ;PACKAGE fd4_package ISCOMPONENT fd4PORT ( Clock : IN STD_LOGIC ;Q0,Q1 : OUT STD_LOGIC);END COMPONENT ;END fd4_package;LIBRARY ieee ;USE ieee.std_logic_1164.all ;LIBRARY work ;USE work.fd4_package.all;ENTITY liushuideng ISPORT ( Clock : IN STD_LOGIC ;Q0,Q1 : OUT STD_LOGIC ;L : OUT STD_LOGIC_VECTOR(0 TO 3)); END liushuideng ;ARCHITECTURE Structure OF liushuideng ISSIGNAL W0,W1 : STD_LOGIC ;BEGINS0: fd4 PORT MAP( CLOCK, W0, W1 );Q0<= W0;Q1<= W1;L(0)<= (NOT W0) OR (NOT W1);L(1)<= W0 OR (NOT W1);L(2)<= (NOT W0) OR W1;L(3)<= W0 OR W1;END Structure ;2)功能仿真建立波形文件,功能仿真结果如下3)时序仿真建立波形文件,时序仿真结果如下:希望以上资料对你有所帮助,附励志名3条:1、积金遗于子孙,子孙未必能守;积书于子孙,子孙未必能读。

9.4.2 集成单稳态触发器集成单稳态触发器既有TTL 型集成电路,如74121、74122等,也有CMOS 型集成电路,如CC14528、CC4098等。

同时,根据器件工作特性的不同,集成单稳态触发器又可分为不可重复触发型和可重复触发型两类。

★ 不可重复触发型的单稳态触发器,指其输出一旦被触发,进入暂稳态期间,如果再有新的触发信号输入,也不会影响电路的工作过程,必须等暂稳态结束,电路重新进入稳态后,电路才能接受新的触发信号,出现下一次暂稳态。

★ 可重复触发型的单稳态触发器则不同,在电路暂稳态期间,如果再有新的触发信号输入,电路将被重新出发,使得输出暂稳态时间延长,以新的触发信号为起点,再维持一个脉冲宽度的时间。

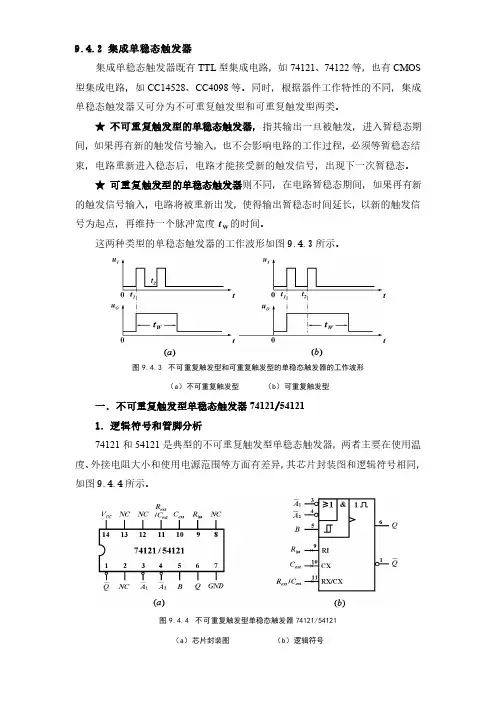

这两种类型的单稳态触发器的工作波形如图9.4.3所示。

图9.4.3 不可重复触发型和可重复触发型的单稳态触发器的工作波形(a )不可重复触发型 (b )可重复触发型一.不可重复触发型单稳态触发器74121/541211. 逻辑符号和管脚分析74121和54121是典型的不可重复触发型单稳态触发器,两者主要在使用温度、外接电阻大小和使用电源范围等方面有差异,其芯片封装图和逻辑符号相同,如图9.4.4所示。

图9.4.4 不可重复触发型单稳态触发器74121/54121(a )芯片封装图 (b )逻辑符号W t★ 由图9.4.4(a )可知:74121和54121都是DIP (双列直插)14管脚的芯片,其中,14、7管脚为电源端,2、8、12、13管脚为空管脚(标注 ),没有任何功能。

剩余8个管脚均为功能端。

★ 图9.4.4(b )为74121/54121的逻辑符号,其上标注了8个功能端的使用特点。

◆ 2个输出端状态互补,电路正常工作,出现输入激励信号时,两端同时输出暂稳态,且电平相反。

◆ 6个输入端中, 是逻辑信号输入端。

其中:是低有效的触发信号输入端,是高有效的触发信号输入端,三者经过相应逻辑运算,形成后级单稳态触发单元的输入激励信号,用表示,即(表达式中, 的含义,它是指低有效的触发信号 的非形式。

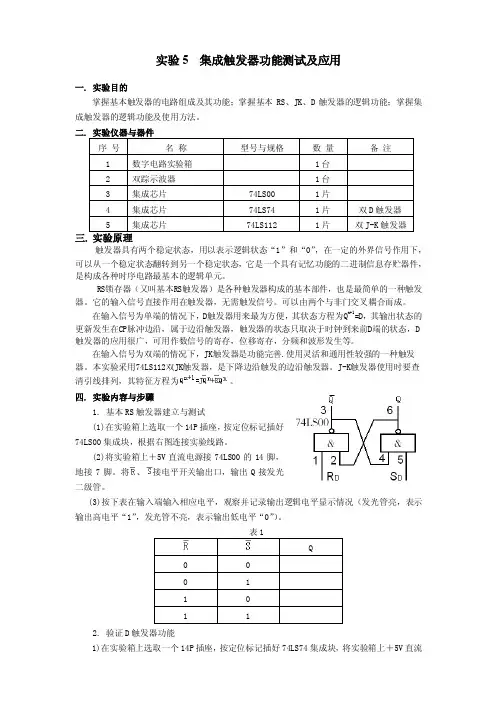

实验5 集成触发器功能测试及应用一. 实验目的掌握基本触发器的电路组成及其功能;掌握基本RS、JK、D触发器的逻辑功能;掌握集成触发器的逻辑功能及使用方法。

二三触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路最基本的逻辑单元。

RS锁存器(又叫基本RS触发器)是各种触发器构成的基本部件,也是最简单的一种触发器。

它的输入信号直接作用在触发器,无需触发信号。

可以由两个与非门交叉耦合而成。

在输入信号为单端的情况下,D触发器用来最为方便,其状态方程为Q n+1=D,其输出状态的更新发生在CP脉冲边沿,属于边沿触发器,触发器的状态只取决于时钟到来前D端的状态,D 触发器的应用很广,可用作数信号的寄存,位移寄存,分频和波形发生等。

在输入信号为双端的情况下,JK触发器是功能完善.使用灵活和通用性较强的一种触发器。

本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。

J-K触发器使用时要查清引线排列,其特征方程为。

四. 实验内容与步骤1.基本RS触发器建立与测试(1)在实验箱上选取一个14P插座,按定位标记插好74LS00集成块,根据右图连接实验线路。

(2)将实验箱上+5V直流电源接74LS00的14脚,地接7脚。

将、接电平开关输出口,输出Q接发光二级管。

(3)按下表在输入端输入相应电平,观察并记录输出逻辑电平显示情况(发光管亮,表示输出高电平“1”,发光管不亮,表示输出低电平“0”)。

2.验证D触发器功能1)在实验箱上选取一个14P插座,按定位标记插好74LS74集成块,将实验箱上+5V直流电源接74LS74的14脚,地接7脚。

将双D 触发器74LS74中的一个触发器的,和D 输入端分别接逻辑开关输出口,CP 端接单次脉冲,输出端和分别接发光二极管。

2)根据输出端状态,填表2。

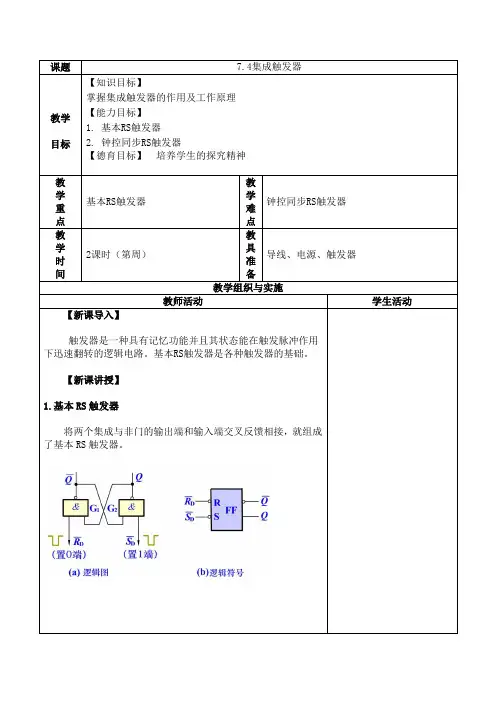

课题7.4集成触发器教学目标【知识目标】掌握集成触发器的作用及工作原理【能力目标】1. 基本RS触发器2.钟控同步RS触发器【德育目标】培养学生的探究精神教学重点基本RS触发器教学难点钟控同步RS触发器教学时间2课时(第周)教具准备导线、电源、触发器教学组织与实施教师活动学生活动【新课导入】触发器是一种具有记忆功能并且其状态能在触发脉冲作用下迅速翻转的逻辑电路。

基本RS触发器是各种触发器的基础。

【新课讲授】1.基本RS触发器将两个集成与非门的输出端和输入端交叉反馈相接,就组成了基本RS触发器。

Q 端的状态为触发器的状态工作状态:10==Q Q,时触发器处于“0”态(稳定状态);01==Q Q ,时触发器处于“1”态(稳定状态)。

基本RS 触发器的逻辑功能如下:当10D D==S R ,时,则)(10==Q Q ; 当01D D==S R ,时,则)(01==Q Q ; 当11D D==S R ,时,则Q 不变(Q 不变); 当00D D ==S R ,时,则Q 不定(Q 不定);这是不允许的2.钟控同步RS 触发器一个基本RS 触发器;两控制门(G3、G4),CP 端无小圆圈――正脉冲(CP 上升沿)触发有效。

CP =0时,G3、G4输出为1,触发器维持原态; CP =1时,触发器状态由R 、S 决定。

3.计数触发型钟控同步RS 触发器触发器的主要用途之一就是构成计数电路,完成计数功能,电路构成特点:在一个钟控同步RS 触发器基础上,将控制门G3、G4的输入端R 、S 分别与触发器的输出端Q 和Q 相连。

设触发器的初始状态为0,则0,1====Q R Q S ;当第一个计数脉冲到来(即CP = 1)时,Q 由0变1、Q 由1变0;当第一个CP 作用后,S = Q = 0、R = Q =1:当第二个CP 到来时,触发器置0。

结论,每来一个计数脉冲,触发器就翻转一次,触发器翻转的次数反映了计数脉冲的数目,实现了计数功能。

第4章集成触发器内容提要4.1 概述一、触发器的概念触发器有三个基本特性:二、触发器的两个稳定状态1状态:0状态:三、触发器的逻辑功能描述:四、触发器的分类:4.2 触发器的基本形式4.2.1 基本RS触发器一、由与非门组成的基本RS触发器1.电路结构2.逻辑功能3.特性表二、由或非门组成的基本RS触发器4.2.2 同步触发器一、同步RS触发器1.电路结构2.逻辑功能3.驱动表4.特性方程5.状态转换图第4章集成触发器内容提要触发器:具有记忆功能的基本逻辑单元。

基本RS触发器的电路结构、工作原理、逻辑功能。

各种触发器的逻辑功能、触发方式。

简单介绍触发器的应用。

4.1 概述一、触发器的概念复习:组合电路的定义?构成其电路的门电路有何特点?组合电路与时序电路的区别?门电路:在某一时刻的输出信号完全取决于该时刻的输入信号,没有记忆作用。

触发器:具有记忆功能的基本逻辑电路,能存储二进制信息(数字信息)。

触发器有三个基本特性:(1)有两个稳态,可分别表示二进制数码0和1,无外触发时可维持稳态;(2)外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆二进制信息,常用作二进制存储单元。

三、触发器的逻辑功能描述:特性表、激励表(又称驱动表)、特性方程、状态转换图和波形图(又称时序图)四、触发器的分类:根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和触发器等。

触发方式不同:电平触发器、边沿触发器和主从触发器等。

电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器等。

4.2 触发器的基本形式4.2.1 基本RS触发器一、由与非门组成的基本RS触发器1.电路结构电路组成:两个与非门输入和输出交叉耦合(反馈延时)。

如图4.2.1(a)所示。

逻辑符号:图(b)所示。

2.逻辑功能复习:与非门的逻辑功能?用DLCCAI或EWB演示基本RS触发器的逻辑功能。

ξ5-1 RS触发器(一)教学目的:1、让学生掌握基本RS触发器的工作原理及逻辑功能2、培养学生的分析能力教学重点:与非门连接后的分析教学难点:基本RS触发器电路的真值表教学方法:讲授法教学时间:一课时教学过程:一、复习:提问基本门电路与门、或门、非门的逻辑功能:二、新授:组合电路和时序电路是数字电路的两大类。

门电路是组合电路的基本单元;触发器是时序电路的基本单元。

触发器按其稳定工作状态可分为双稳定触发器,单稳定触发器,无稳态触发器(多谐振荡器)等。

双稳态触发其按其逻辑功能可分为RS触发器,JK触发器,D触发器和T触发器等;按其结构可分为主从触发器和维持阻塞型触发器等。

(一)基本RS触发器1、电路组成:基本RS触发器可由两个“与非”门交叉连接而成,如下图所示。

QG1图(a)基本RS触发器图(b)符号图(c)基本RS触发器真值表做好与组合逻辑电路的衔接触发器其实也是由门电路组成的组合逻辑门电路,因此要理解和掌握它,就要先得从组合逻辑门电路入手。

以上这个图是基本RS触发器,它其实是由2个与非门的输入端与出端交叉耦合而组成,所以对于与非门的理解明了。

与非门,其表示的意思为Y=BA ,其规律为全1出0,有0出1,只有理解了基本与非门,才可以去进一步分析基本RS触发器。

Q与Q是基本触发器的输出端,两者的逻辑状态在正常条件下能保持相反。

这种触发器有两种稳定状态:一个状态是Q=1,Q=0,称为置位状态(“1”态);另一个状态是Q=0,Q=1,称为复位状态(“0”态),相当于以Q为准来命名。

相应的输入端R、S分别称为直接置0端或复位端、直接置位端或直接置“1”端2、逻辑功能:1)S=1,R=0所谓S=1 ,就是将S端保持高电位;而R=0,就是在R端加一个负脉冲。

设触发器的初始状态为“1”态,即Q=1,Q =0。

这时“与非”门G2有一个输入端为“0”,其输出端变为“1”;而“与非”门G1的两个输入端全为“1”,其输出端Q变为“0”。

触发器逻辑功能精细化总结记忆法[摘要]触发器逻辑功能表现形式灵活,以名称、逻辑电路图标志、关联方法、连接形式总结出适合中职学生记忆的方法,以便于学生掌握与分析触发器逻辑关系知识,形成一个记忆的体系。

[关键词]触发器逻辑功能记忆法触发器是中职学生必须掌握的基础知识,描述触发器逻辑功能的方法有真值表、逻辑表达式、波形图、逻辑图等。

由于触发方式的区别,因此学生不易记忆,容易混淆逻辑关系。

笔者结合实际教学总结以下方法以便学生巧记触发器的逻辑功能。

一、触发器名称和逻辑功能关联记忆法触发器主要有两个双稳态:0态和1态。

相应输入端能使输出端Q处于0态和1态,称为置0端或置1端。

在触发器接收数据期间,置0端有效,Q输出为0,置1端有效,Q输出为1,简记为置0端有效置0,置1端有效置1。

在中职教材中只涉及RS触发器、JK触发器、D触发器。

按照01的顺序关联触发器名称可以记为“RSKJ”。

把JK触发器记忆为KJ触发器,以便符合01顺序,即RSKJ对应0101,R端、K端为置0端,S端、J端为置1端。

D触发器只记住D端置1为1,置0为0,不需要特别想办法记忆。

实际上应向学生说明除了RS触发器外,JK触发器J与K端不再称置0端与置1端,也就是这两端有效组合时还有别的功能,但笔者要求学生在心里还把它们记为置0端与置1端,这样,触发器功能记忆就方便了:“置0端有效置0,置1端有效置1;两者同时有效,RS不允许,JK翻转;两者同时无效,均保持功能。

”二、触发方式与记忆标志无论是置0端还是置1端有效与否,还得取决于控制端是否有效。

只有在控制端有效的前提下,触发器才接收数据,否则,即便是置0端、置1端都有效也不会输出数据。

所以,控制端与置0端、置1端形成了“控制与受控”的关系。

对受控端而言,有效无效表现在电平方式上,即高电平有效或者是低电平有效;对控制端而言,有效无效的表现形式有两种,一是电平触发方式,和受控端一样;二是边沿触发方式,即上升沿或下降沿有效。

电工电子实验报告集成触发器及应用一、实验目的1.掌握集成触发器的逻辑功能。

2.熟悉用触发器构成计数器的方法。

3.掌握集成触发器的基本应用。

二、主要仪器设备及软件硬件:直流稳压电源,电工电子综合实验箱,函数信号发生器,示波器,笔记本电脑软件:NI Multisim 14三、实验原理(或设计过程)1.集成触发器的种类和特点触发器是组成时序逻辑电路的基本单元,集成触发器主要有3大类,锁存触发器、D触发器和JK触发器。

(1)D锁定触发器目前常使用的D锁存触发器有四锁定触发器74LS75,功能表如下锁定触发器具有以下三个特点:①锁定触发器不会出现不定状态,输入信号只需要一个,使用方便。

②锁定触发器在CP=“0”时,状态不因输入信号发生变化。

③锁定触发器是电平触发的触发器,在CP=“1”,D端状态不允许变化。

(2)维持堵塞D触发器维持阻塞D触发器克服了空翻现象,因而维持阻塞D触发器可以用来作计数器和位移寄存器。

(3)JK触发器①主从JK触发器目前主要的主从JK触发器74LS72单JK触发器和74LS112双JK触发器.②边沿JK触发器边沿触发器不仅可以克服空翻现象,而且仅仅在时钟CP的上升沿或下降沿才对输入信号起响应。

2.集成触发器的应用触发器在构成包含时间关系的数字电路中是必不可少的,它广泛用来构成计器、寄存器、移位寄存器,还可用来构成单稳、多谐等电路。

(1)二进制计数器触发器可以构成各种计数器。

每一个触发器都接成计数状态。

对D触发器,将其D端与Q非输出端相接就构成计数状态,因D触发器是上升沿触发,所以用它们构成二进制计数器时,应将每位Q非输出端与高一位CP端相连。

如图使用TTL集成D触发器和JK触发器构成的三位二进制计数器(2)并行累加器累加器适用于多个数相加求和的一种电路。

(3)堆成脉冲至对称脉冲的奇数分频四、实验电路图五、实验内容和实验结果用74LS74设计二位二进制加法计数器状态转移表:测试结果:六、实验小结通过这次实验,我们掌握集成触发器的逻辑功能,熟悉用触发器构成计数器的方法,掌握集成触发器的基本应用。