同步二十进制计数器共30页文档

- 格式:ppt

- 大小:4.10 MB

- 文档页数:30

同步二进制计数器计数规律

哎呀呀,我是个小学生,这“同步二进制计数器计数规律”对我来说可太难懂啦!

老师在课堂上讲这个的时候,我感觉自己就像掉进了一个数字的大迷宫里。

什么是同步二进制计数器呀?它的计数规律又是啥?我瞪大眼睛,竖起耳朵,努力想要搞清楚。

我就想呀,这同步二进制计数器是不是就像我们排队跑步,一个接一个,有自己的顺序,不能乱?可这数字的队伍可比我们跑步复杂多啦!

老师说,同步二进制计数器的计数规律是按照二进制的规则来的。

二进制?那不是只有0 和1 嘛。

这就好像我们的开关,开就是1,关就是0 。

可在计数器里,它们可不是简单的开关,而是有着神奇的规律。

我看了看同桌,他也是一脸迷茫。

我忍不住问他:“你懂了吗?”他摇摇头说:“我感觉自己的脑袋都要变成浆糊啦!”可不是嘛,这也太难了!

再看看前面的学霸,人家好像听得津津有味。

我心里那个羡慕呀,我啥时候能像他一样厉害呢?

老师举了个例子,说就像上楼梯,每一步都有特定的数字变化。

我在心里想:这上楼梯谁不会呀,可这数字的楼梯怎么就这么难爬呢?

后来老师又详细地讲了讲,我好像有点明白了。

原来同步二进制计数器的计数规律就是从0 开始,一个一个地往上加,每次加1 ,数字的变化就按照二进制的规则来。

哎呀,我算是搞懂了一些,可还是觉得有点晕乎。

这知识就像一座大山,我才刚刚开始往上爬呢!不过我可不会轻易放弃,我一定要把它弄明白!

我觉得呀,学习这些难的知识就像一场冒险,虽然有时候会迷路,会遇到困难,但是只要坚持,总会找到出路,看到美丽的风景!。

实验二十进制计数器实验该实验将使用Verilog 硬件描述语言在DE2-70 开发平台上设计一个基本时序逻辑电路——1 位十进制计数器。

通过这个实验,读者可以了解使用Quartus 工具设计硬件的基本流程以及使用Quartus II 内置的工具进行仿真的基本方法和使用SignalTap II 实际观察电路运行输出情况。

SignalTap II 是Quartus 工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG 电缆将电路运行的实际输出传回Quartus 进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

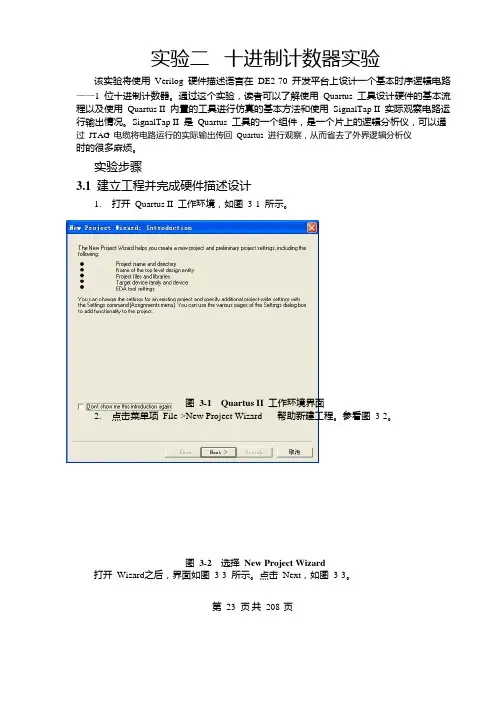

实验步骤3.1建立工程并完成硬件描述设计1. 打开Quartus II 工作环境,如图3-1 所示。

图3-1 Quartus II工作环境界面2. 点击菜单项File->New Project Wizard 帮助新建工程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界面如图3-3 所示。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界面3. 输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4 所示。

点击Next。

图3-4输入设计工程信息4. 添加设计文件。

界面如图3-5 所示。

如果用户之前已经有设计文件(比如.v 文件)。

那么再次添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑设计文件。

图3-5添加设计文件5. 选择设计所用器件。

由于本次实验使用Altera 公司提供的DE2-70 开发板,用户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

同步二进制计数器的电路1. 引言同步二进制计数器是一种常见的数字电路,用于计数和记录输入脉冲的数量。

它由多个触发器组成,通过时钟信号同步触发器的状态改变,从而实现计数功能。

本文将介绍同步二进制计数器的原理、设计方法以及应用场景。

2. 原理同步二进制计数器由多个触发器组成,其中每个触发器都有两个输入:时钟信号和清零信号。

当时钟信号上升沿到达时,触发器根据其输入状态改变输出状态。

当清零信号为高电平时,触发器将输出置为0。

在同步二进制计数器中,每个触发器都与前一个触发器相连,并且第一个触发器与外部输入信号相连。

当时钟信号上升沿到达时,第一个触发器会检测到外部输入脉冲,并将其传递给下一个触发器。

这样,在每个时钟周期内,每个触发器都会将前一个触发器的输出传递给下一个触发器。

3. 设计方法3.1 触发器选择在设计同步二进制计数器时,需要选择适当的触发器。

常见的触发器有D触发器、JK触发器和T触发器。

根据具体的需求,选择合适的触发器进行设计。

3.2 计数位数确定根据需要计数的范围,确定计数器需要多少位。

例如,如果需要计数0到15之间的数字,那么需要一个4位计数器。

3.3 连接触发器将选择好的触发器按照顺序连接起来,构成同步二进制计数器电路。

每个触发器都与前一个触发器相连,第一个触发器与外部输入信号相连。

3.4 添加清零功能为了能够在需要时将计数值清零,可以在每个触发器上添加清零信号输入,并通过逻辑门控制清零信号的传递。

4. 应用场景同步二进制计数器广泛应用于各种领域,包括但不限于以下几个方面:4.1 计时和测量同步二进制计数器可以用于计时和测量应用中。

通过连接合适数量的同步二进制计数器,可以实现高精度的时间测量和频率测量。

4.2 数据传输和通信同步二进制计数器可以用于数据传输和通信应用中。

通过将计数器的输出与其他电路相连,可以实现数据的同步传输和时序控制。

4.3 事件触发和触发控制同步二进制计数器可以用于事件触发和触发控制应用中。

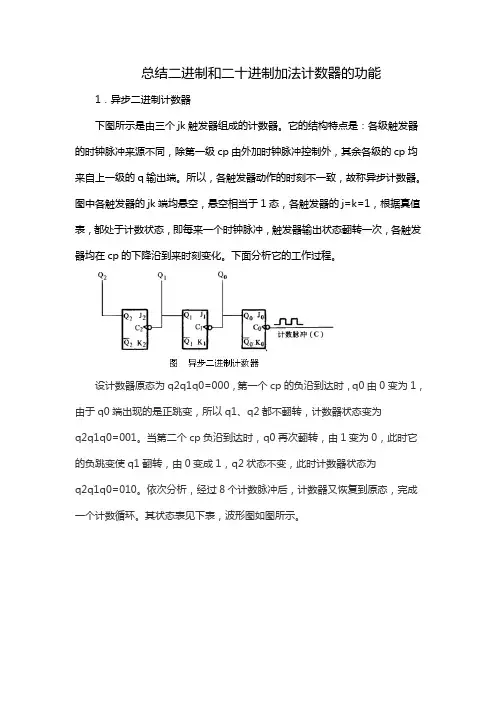

总结二进制和二十进制加法计数器的功能1.异步二进制计数器下图所示是由三个jk触发器组成的计数器。

它的结构特点是:各级触发器的时钟脉冲来源不同,除第一级cp由外加时钟脉冲控制外,其余各级的cp均来自上一级的q输出端。

所以,各触发器动作的时刻不一致,故称异步计数器。

图中各触发器的jk端均悬空,悬空相当于1态,各触发器的j=k=1,根据真值表,都处于计数状态,即每来一个时钟脉冲,触发器输出状态翻转一次,各触发器均在cp的下降沿到来时刻变化。

下面分析它的工作过程。

设计数器原态为q2q1q0=000,第一个cp的负沿到达时,q0由0变为1,由于q0端出现的是正跳变,所以q1、q2都不翻转,计数器状态变为q2q1q0=001。

当第二个cp负沿到达时,q0再次翻转,由1变为0,此时它的负跳变使q1翻转,由0变成1,q2状态不变,此时计数器状态为q2q1q0=010。

依次分析,经过8个计数脉冲后,计数器又恢复到原态,完成一个计数循环。

其状态表见下表,波形图如图所示。

从以上分析可以看出:一个触发器可以表示一位二进制数,两个触发器串联,就有四种状态(22=4),可构成四进制计数器,n个触发器串联,则可组成2n 进制计数器。

由波形图可见,q0波形的频率是cp波形频率的,q1的频率又是q0频率的…,各级输出波形的频率均为前一级的二分频,所以,q2为cp 的八分频。

计数器的计数顺序是从000到111,每经一个cp加1,所以叫加法计数器。

*如何分析n进制计数器?1. 列出各位触发器的驱动方程,时钟方程。

2. 设各位触发器的一种初始状态。

(通常设全0)3. 求输入第一个cp触发脉冲下的状态。

4. 再以刚刚得到的状态为“初始状态”,求输入第二个cp脉冲作用下的状态。

5. 如此重复做下去,几个脉冲过后,返回初始状态(通常设全0),就是几进制。

注意:对于异步计数器,要兼顾时钟方程及触发器的边沿触发方式。

2.十进制计数器下图所示为同步十进制加法计数器。

同步二进制计数器案例说明(1)同步二进制加法计数器异步二进制计数器结构简单,但由于触发器的翻转逐级进行,因而计数速度较低。

若使计数器状态转换时,将所有需要翻转的触发器同时翻转,则可以提高计数速度。

下面以同步四位二进制加法计数器为例说明其计数原理。

利用四位加法计数器的状态表(即表8.10),可以找到构成同步二进制加法计数器的方法。

由表可知,最低位触发器每输入一个计数脉冲翻转一次,其它各触发器都是在其所有低位触发器输出端Q全为1时,在下一计数脉冲触发沿到来时翻转。

若采用主从JK触发器,则可得到四个触发器JK端的逻辑表达式为:J0=K0=1J1=K1= Q0J2=K2= Q1Q0J3=K3= Q2Q1Q0以上讨论的是四位,如果位数更多,控制进位的规律可以依次类推。

第n位触发器的JK端逻辑表达式应为:J n=K n=Q n-1…Q1Q0由此得到同步四位二进制加法计数器的一种连接方式,如图8.48所示。

各触发器受同一计数脉冲CP的控制,其状态翻转与CP脉冲同步,显然它比异步计数器的计数速度高。

图8.48 同步四位二进制加法计数器(2)同步二进制减法计数器利用二进制减法计数规则,可得到构成同步二进制减法计数器的方法。

由表8.11可知:实现减法计数要求最低位触发器每输入一个计数脉冲翻转一次,其它各触发器都是在其所有低位触发器输出端Q全为0时,在下一计数脉冲触发沿到来时翻转。

因此,只要将图8.47所示的二进制加法计数器的输出由Q端改为Q端,便构成了同步四位二进制减法计数器。

(3)同步二进制可逆计数器同步二进制可逆计数器是在加法计数器和减法计数器的基础上,再设置一些控制电路而组成的,它兼有加、减两种功能。

二、十进制计数器二进制计数器结构简单,但是读数不方便,有些场合需要采用十进制计数器,以便译码显示输出。

十进制计数器通常是在四位二进制计数器的基础上经过修改得到的。

它跳过了1010~1111这六个状态,用四位二进制数的0000~1001代表十进制中的每一个数,状态表见表8.12。

![同步计数器_电工电子技术_[共2页]](https://uimg.taocdn.com/6adc303d551810a6f42486ac.webp)

《电子线路》课程设计报告一、设计目的本课程设计是脉冲数字电路的简单应用,在许多领域中计时器均得到普遍应用,诸如在体育比赛,定时报警器、交通信号灯、红绿灯,还可以用来做为各种药丸,药片,胶囊在指定时间提醒用药等等,由此可见计时器在现代社会是何其重要的。

本设计主要能完成:显示30秒计时功能;系统设置外部操作开关,控制计时器的直接清零、启动功能;在直接清零时,数码管显示器灭灯;计时器为30秒递加计时其计时间隔为1秒;计时器递加计时到零时,数码显示器不灭灯。

二、设计要求1、具有显示30秒计时功能:(1)系统设置外部操作开关,控制计时器的直接清零、启动;(2)在直接清零时,要求数码管显示器灭灯;(3)计时器为30秒递加计时,其计时间隔为1秒;(4)计时器递加计时到30时,数码显示器不能灭灯。

2、设计任务及目标:(1)根据原理图分析各单元电路的功能;(2)熟悉电路中所用到的各集成块的管脚及其功能;(3)进行电路的装接、调试,直到电路能达到规定的设计要求;(4)写出完整、详细的课程设计报告。

三、原理框图(1)总体参考方案:30秒计时器的总体参考方案框图如图2-1所示。

它包括秒脉冲发生器、计数器、译码显示电路、报警电路和辅助时序控制电路(简称控制电路)等五个模块组成。

其中计数器和控制电路是系统的主要模块。

计数器完成30秒计时功能,而控制电路完成计数器的直接清零、启动计数、译码显示电路的显示等功能。

图1 30秒计时器系统设计框图秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不太高,故电路可采用555集成电路或由TTL与非门组成的多谐振荡器构成。

译码显示电路由CD4026和共阴极七段LED显示器组成。

(2)设计方案分析设计任务,计数器和控制电路是系统的主要部分。

计数器完成30s计时功能,而控制电路具有直接控制计数器的启动计数、译码显示电路的显示。

为了满足系统的设计要求,在设计控制电路时,应正确处理各个信号之间的时序关系。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT20 ISPORT (CLK_in,clr:IN STD_LOGIC;--分频时钟信号ENA: IN STD_LOGIC;--使能端控制LED:OUT STD_LOGIC_VECTOR(13 DOWNTO 0)--控制9个SHUMAGUAN的输出信号);END CNT20 ;ARCHITECTURE BEHA VE OF CNT20 ISSIGNAL sel:STD_LOGIC_VECTOR(4 DOWNTO 0 );SIGNAL clk:STD_LOGIC;BEGINclock:process(clk_in) --输入的时钟为4Mvariable clock_buffer:std_logic; ----定义一个标准逻辑变量clock_buffervariable count_time:integer range 0 to 1999999; ---定义一个整型变量count_timebeginif clk_in'event and clk_in='1' thenif count_time=1999999 thencount_time:=0;clock_buffer:=not clock_buffer; --每计2M次数时翻转一次elsecount_time:=count_time+1;end if;end if;clk<=clock_buffer; --输出的时钟为1HZend process;PROCESS(ENA,CLK,sel,clr)BEGINif(clr='0')thensel<="00000";elseIF RISING_EDGE (CLK) THENIF ENA='1' THENIF sel="10100"THENsel<="00000";ELSEsel<=sel+'1';END IF ;END IF;END IF;END IF;CASE sel ISWHEN "00000"=>LED<="10000001000000";--0WHEN "00001"=>LED<="10000001111001";WHEN "00010"=>LED<="10000000100100";WHEN "00011"=>LED<="10000000110000";WHEN "00100"=>LED<="10000000011001";WHEN "00101"=>LED<="10000000010010";--5WHEN "00110"=>LED<="10000000000010";WHEN "00111"=>LED<="10000001111000";WHEN "01000"=>LED<="10000000000000";WHEN "01001"=>LED<="10000000010000";WHEN "01010"=>LED<="11110011000000";--10WHEN "01011"=>LED<="11110011111001";WHEN "01100"=>LED<="11110010100100";WHEN "01101"=>LED<="11110010110000"; WHEN "01110"=>LED<="11110010011001";WHEN "01111"=>LED<="11110010010010";WHEN "10001"=>LED<="11110010000010";WHEN "10010"=>LED<="11110011111000";WHEN "10011"=>LED<="11110010000000";WHEN "10100"=>LED<="11110010010000";WHEN OTHERS=>NULL;END CASE;END PROCESS;END BEHA VE;。