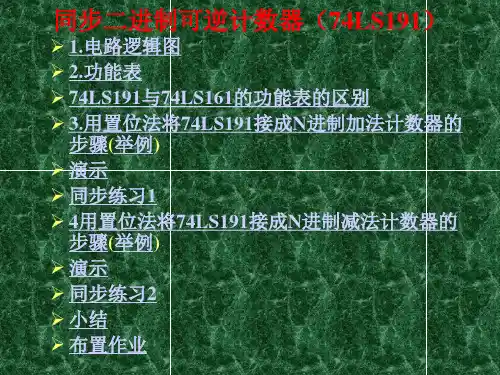

位二进制同步可逆计数器

- 格式:ppt

- 大小:415.50 KB

- 文档页数:10

74HC245详细中文资料74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245, CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -40~+85 ℃ -40~+125 ℃多路分配功能74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(L STTL)系列。

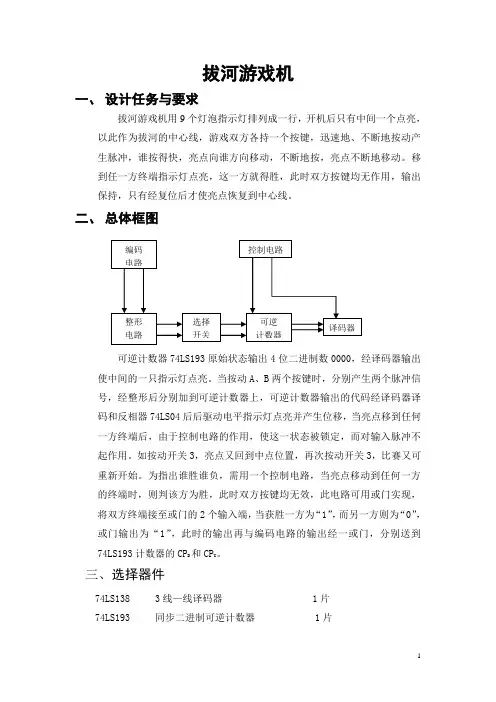

拔河游戏机一、设计任务与要求拔河游戏机用9个灯泡指示灯排列成一行,开机后只有中间一个点亮,以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产生脉冲,谁按得快,亮点向谁方向移动,不断地按,亮点不断地移动。

移到任一方终端指示灯点亮,这一方就得胜,此时双方按键均无作用,输出保持,只有经复位后才使亮点恢复到中心线。

二、总体框图可逆计数器74LS193原始状态输出4位二进制数0000,经译码器输出使中间的一只指示灯点亮。

当按动A、B两个按键时,分别产生两个脉冲信号,经整形后分别加到可逆计数器上,可逆计数器输出的代码经译码器译码和反相器74LS04后后驱动电平指示灯点亮并产生位移,当亮点移到任何一方终端后,由于控制电路的作用,使这一状态被锁定,而对输入脉冲不起作用。

如按动开关3,亮点又回到中点位置,再次按动开关3,比赛又可重新开始。

为指出谁胜谁负,需用一个控制电路,当亮点移动到任何一方的终端时,则判该方为胜,此时双方按键均无效,此电路可用或门实现,将双方终端接至或门的2个输入端,当获胜一方为“1”,而另一方则为“0”,或门输出为“1”,此时的输出再与编码电路的输出经一或门,分别送到74LS193计数器的CPD 和CPU。

三、选择器件74LS138 3线—线译码器 1片74LS193 同步二进制可逆计数器 1片74LS00 四2输入与非门 2片74LS04 六反向器 2片74LS08 四2输入与门 1片74LS32 四2输入或门 1片电阻 1 KΩ 4个100Ω1个开关单刀双掷开关 2个单刀单掷开关 1个下面详细介绍这些器件3.1 3线—8线译码器74LS138图(1)74LS138的逻辑符号图图(2) 74LS138的逻辑框图输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图(1)为3线-8线译码器74LS138的逻辑符号图,其有3个附加的控制端G1、G2A和G2B。

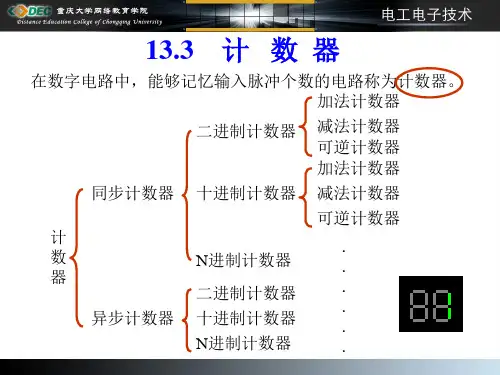

同步二进制计数器的电路1. 引言同步二进制计数器是一种常见的数字电路,用于计数和记录输入脉冲的数量。

它由多个触发器组成,通过时钟信号同步触发器的状态改变,从而实现计数功能。

本文将介绍同步二进制计数器的原理、设计方法以及应用场景。

2. 原理同步二进制计数器由多个触发器组成,其中每个触发器都有两个输入:时钟信号和清零信号。

当时钟信号上升沿到达时,触发器根据其输入状态改变输出状态。

当清零信号为高电平时,触发器将输出置为0。

在同步二进制计数器中,每个触发器都与前一个触发器相连,并且第一个触发器与外部输入信号相连。

当时钟信号上升沿到达时,第一个触发器会检测到外部输入脉冲,并将其传递给下一个触发器。

这样,在每个时钟周期内,每个触发器都会将前一个触发器的输出传递给下一个触发器。

3. 设计方法3.1 触发器选择在设计同步二进制计数器时,需要选择适当的触发器。

常见的触发器有D触发器、JK触发器和T触发器。

根据具体的需求,选择合适的触发器进行设计。

3.2 计数位数确定根据需要计数的范围,确定计数器需要多少位。

例如,如果需要计数0到15之间的数字,那么需要一个4位计数器。

3.3 连接触发器将选择好的触发器按照顺序连接起来,构成同步二进制计数器电路。

每个触发器都与前一个触发器相连,第一个触发器与外部输入信号相连。

3.4 添加清零功能为了能够在需要时将计数值清零,可以在每个触发器上添加清零信号输入,并通过逻辑门控制清零信号的传递。

4. 应用场景同步二进制计数器广泛应用于各种领域,包括但不限于以下几个方面:4.1 计时和测量同步二进制计数器可以用于计时和测量应用中。

通过连接合适数量的同步二进制计数器,可以实现高精度的时间测量和频率测量。

4.2 数据传输和通信同步二进制计数器可以用于数据传输和通信应用中。

通过将计数器的输出与其他电路相连,可以实现数据的同步传输和时序控制。

4.3 事件触发和触发控制同步二进制计数器可以用于事件触发和触发控制应用中。

基于Verilog语言的4位二进制可逆计数器的设计作者:杨柳李百伦徐杨李鹏飞殷海博葛楠来源:《电脑知识与技术》2019年第09期摘要:此次设计介绍了Verilog-HDL语言在可逆计数器的具体应用,给出了仿真波形并下载到FPGA开发板上实际进行验证。

说明了实现电子电路的自动化设计(EDA)过程和EDA 技术在现代数字系统中的重要地位及作用.关键词:Verilog-HDL;EDA;FPGA;开发板;仿真中图分类号:TP311 文献标识码:A文章编号:1009-3044(2019)09-0219-021 绪论1.1 Verilog HDL 语言1983 年, GDA公司的 Phil Moorby首先创立Verilog HDL语言。

后来phil morrby变成Verilog-XL 的主要的设计师以及(Cadence Design System)的第一合伙人。

一年后,第一个有关 Verilog-XL 的仿真器由Moobry设计,在1986年他提出的XL算法可以用于快速门仿真,又对 Verilog HDL 的发展产生深远的影响。

1.2 EDA技术的优势1)抽象的行为以及功能的描述,在各个内部线路的结构可以使用HDL对数字系统进行,从而可以进行计算机的模拟验证在电子设计各个阶段、各个层次,进而提高设计过程准确性。

既能缩短设计的周期,也能很大程度降低设计的成本。

2)EDA可以自动完成设计过程,依赖于种类库。

例如:在逻辑综合时由综合库,在逻辑仿真时有模拟库,以及在版图综合时又版图库,在测试综合时有测试库等。

3)渐渐强大的逻辑设计仿真测试技术,很大程度上提高大规模的系统电子设计自动化,是EDA中最具有电子现代化设计的技术特征的功能,对如今自动化生产做出巨大的贡献。

1.3 FPGA介绍FPGA (Field Programmable Gate Array)为现场可编程门阵列。

基于PAL、GAL、FPLD 等一些可编程器件,FPGA在此基础上进行深入发展。

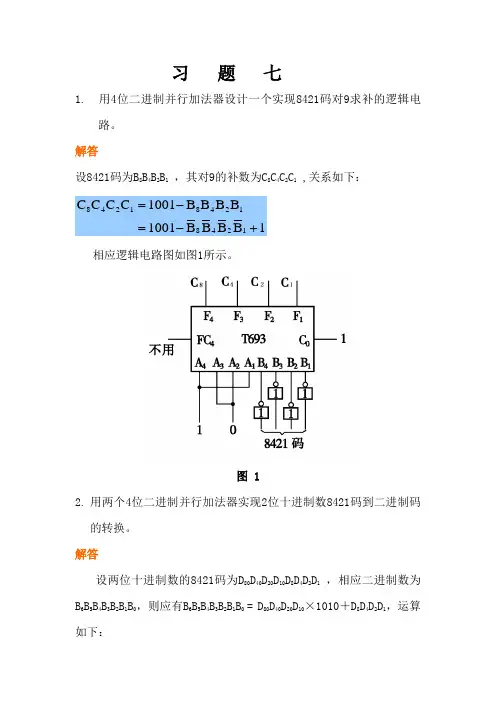

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。

单片机驱动芯片(74HC245)详细中文资料(74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列) 74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片7 4HC245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC238逻辑功能一致,只不过74HC138为反相输出。

一、功能CD74HC245 ,CD74HC238和CD74HCT245, CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -4 0~+85 ℃ -40~+125 ℃多路分配功能74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

二进制计数器的原理1.二进制异步加计数器的原理原理分析:假设各触发器均处于0态,根据电路结构特点以及D 触发器工作特性,不难得到其状态图和时序图,它们分别如图8.4.2和图8.4.3所示。

其中虚线是考虑触发器的传输延迟时间tpd后的波形。

由状态图可以清楚地看到,从初始状态000(由清零脉冲所置)开始,每输入一个计数脉冲,计数器的状态按二进制递增(加1),输入第8个计数脉冲后,计数器又回到000状态。

因此它是23进制加计数器,也称模八(M=8)加计数器。

从时序图可以清楚地看到Q0,Q1,Q2的周期分别是计数脉冲(CP)周期的2倍,4倍、8倍,也就是说Q0,Q1,Q2,分别对CP波形进行了二分频,四分频,八分频,因而计数器也可作为分频器。

需要说明的是,由图8.4.3中的虚线波形可知,在考虑各触发器的传输延迟时间tpd时,对于一个n 位的二进制异步计数器来说,从一个计数脉冲(设为上升沿起作用)到来,到n 个触发器都翻转稳定,需要经历的最长时间是ntpd ,为保证计数器的状态能正确反应计数脉冲的个数,下一个计数脉冲(上升沿)必须在ntpd 后到来,因此计数脉冲的最小周期Tmin=ntpd 。

2.二进制异步减计数器的原理原理分析:图8.4.4是3位二进制异步减计数器的逻辑图和状态图。

从初态000开始,在第一个计数脉冲作用后,触发器FF0由0翻转为1(Q0的借位信号),此上升沿使FF1也由0翻转为1(Q1的借位信号),这个上升沿又使FF2 由0翻转为1,即计数器由000变成了111状态。

在这一过程中,Q0向Q1进行了借位,Q1向Q2进行了借位。

此后,每输入1个计数脉冲,计数器的状态按二进制递减(减1)。

输入第8个计数脉冲后,计数器又回到000状态,完成一次循环。

因此,该计数器是23进制(模8)异步减计数器,它同样具有分频作用。

3.二进制同步加计数器,同步减计数器的原理二进制同步加计数器的原理分析:图8.4.5是用JK触发器(但已令J=K)组成的4位二进制(M=16)同步加计数器。