锁相环典型应用-课件·PPT

- 格式:ppt

- 大小:1.14 MB

- 文档页数:18

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

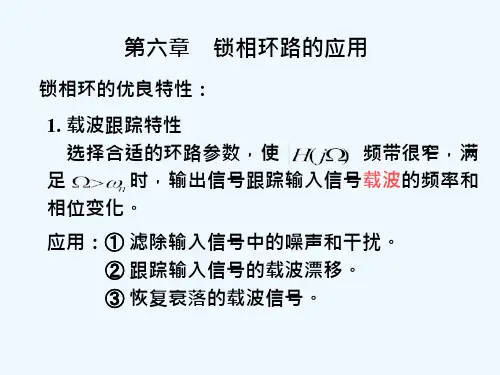

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

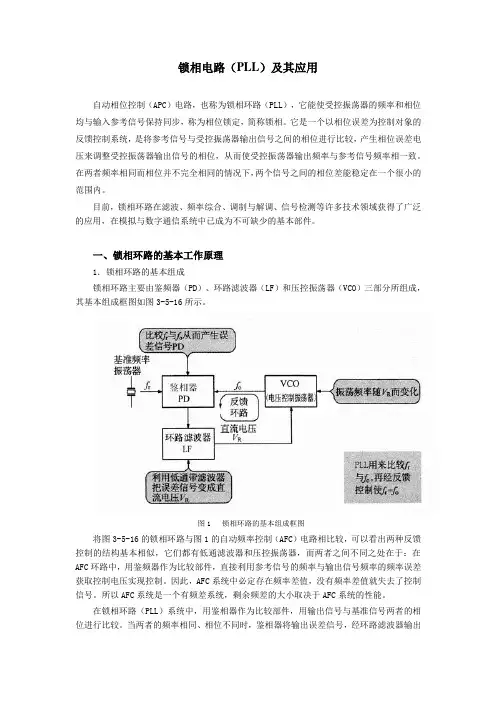

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。