锁相环PLL基本原理设计与应用

- 格式:ppt

- 大小:1.29 MB

- 文档页数:75

什么是电子电路中的锁相环及其应用电子电路中的锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用的反馈控制电路,用于将输入信号的相位与频率与参考信号的相位与频率同步,从而实现信号的稳定性和精确性。

锁相环在通信、计算机、音频处理等领域都有重要的应用。

一、锁相环的工作原理锁相环主要由相位比较器(Phase Detector)、环形数字控制振荡器(VCO)和低通滤波器(LPF)组成。

相位比较器用来比较输入信号和参考信号的相位差,输出一个宽度等于相位差的脉冲信号。

VCO根据相位比较器输出的脉冲信号的宽度和方向来调节输出频率,使其与参考信号的频率和相位同步。

LPF用来滤除VCO输出信号中的高频成分,保证输出的稳定性。

二、锁相环的应用1. 通信领域:在数字通信系统中,锁相环被广泛应用于时钟恢复、时钟生成和时钟变换等方面。

通过锁相环可以实现对时钟信号的稳定传输,提高通信系统的可靠性和容错性。

2. 音频处理:在音频设备中,锁相环被用于时钟同步和抖动消除。

通过锁相环可以实现音频数据的同步传输和精确抖动控制,提高音质和信号稳定性。

3. 数字系统:在数字系统中,锁相环可用于时钟恢复、频率合成和位钟提取等方面。

通过锁相环可以实现对时钟信号的稳定提取和精确合成,确保系统的可靠运行。

4. 频率调制与解调:在调制与解调系统中,锁相环被应用于频偏补偿和相位同步。

通过锁相环可以实现对信号频偏和相位偏移的补偿,保证调制与解调的准确性和稳定性。

5. 频谱分析:锁相环还可以应用于频谱分析仪中,通过锁相环可以实现频率分析的准确性、稳定性和精确性。

三、锁相环的特点1. 稳定性:锁相环可以通过调整VCO的输出频率来实现输入信号和参考信号的同步,从而提高信号的稳定性。

2. 精确性:锁相环可以通过精确的相位比较和频率调节,实现对信号相位和频率的精确控制,提高信号处理的准确性。

3. 自适应性:锁相环可以根据输入信号和参考信号的变化自动调节,适应不同输入条件下的信号同步要求。

模拟锁相环实验报告锁相环(PLL)是一种常见的控制系统,它可以将输入信号的频率和相位与参考信号匹配,从而实现精确的信号同步和频率锁定。

本次实验旨在通过模拟锁相环的实验,了解PLL的基本原理和实现方式,并探究其在频率合成和时钟恢复等应用中的优势和局限性。

一、实验原理1.1 PLL的基本原理PLL由相频比较器、环形控制器、振荡器和分频器等组成。

其基本原理如下:(1)将参考信号和输出信号输入相频比较器,得到误差信号;(2)将误差信号输入环形控制器,控制其输出的控制电压;(3)将控制电压输入振荡器,控制其输出的频率和相位;(4)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制。

通过不断比较和修正,PLL可以使输出信号的频率和相位与参考信号匹配,从而实现锁定。

1.2 实验器材本次实验采用的器材如下:信号发生器、示波器、多路开关、振荡器、计数器等。

1.3 实验步骤(1)将信号发生器产生的正弦波信号作为参考信号,通过示波器观测其频率和相位;(2)将信号发生器产生的方波信号作为输入信号,通过多路开关控制输入信号的频率和幅值;(3)将输入信号和参考信号输入相频比较器,得到误差信号;(4)将误差信号输入环形控制器,控制其输出的控制电压;(5)将控制电压输入振荡器,控制其输出的频率和相位;(6)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制;(7)通过计数器观测输出信号的频率和相位,调整环形控制器的参数,使输出信号与参考信号匹配。

二、实验结果在实验过程中,我们先设置参考信号的频率为1KHz,通过示波器观测其频率和相位,然后将信号发生器产生的方波信号作为输入信号,进行频率和幅值的调节,使其与参考信号匹配。

在调节的过程中,我们观测到输出信号的频率和相位逐渐趋近于参考信号的频率和相位,最终实现了同步锁定。

然后,我们进一步测试了PLL在频率合成和时钟恢复等应用中的性能。

我们将输入信号的频率和幅值进行变化,观测输出信号的变化情况。

标题:MATLAB中的PLL锁相环原理一、介绍PLL锁相环的概念PLL(Phase-Locked Loop)锁相环是一种常用的控制系统,广泛应用于通信系统、数字信号处理和电力系统等领域。

它通过比较输入信号与本地参考信号的相位差,实现对输入信号的精确跟踪和同步。

在MATLAB中,我们可以通过编写代码来模拟PLL锁相环,并深入理解其工作原理。

二、PLL锁相环的基本结构PLL锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器等组成。

它的基本结构如下:1. 相位比较器:用于比较输入信号和本地参考信号的相位差,并产生控制电压。

2. 低通滤波器:将相位比较器输出的控制电压进行滤波,去除高频噪声,得到稳定的调节电压。

3. VCO:根据低通滤波器输出的调节电压,调节其输出频率,实现对输入信号的跟踪。

4. 分频器:将VCO输出的信号进行分频,得到本地参考信号,用于与输入信号进行比较。

三、PLL锁相环的工作原理PLL锁相环的工作过程可以分为锁定和跟踪两个阶段。

1. 锁定阶段:在初始时刻,输入信号的频率与VCO的输出频率不同步。

相位比较器会检测到二者之间存在相位差,产生相应的控制电压,通过低通滤波器传递给VCO。

VCO根据控制电压,调节其输出频率,使其逐渐与输入信号频率同步,最终达到锁定状态。

2. 跟踪阶段:一旦锁定完成,PLL锁相环会持续监测输入信号的频率变化,并调节VCO的输出频率,确保其始终与输入信号同步。

低通滤波器起到平稳调节的作用,使得VCO的输出频率能够迅速跟随输入信号的变化。

四、MATLAB中的PLL锁相环模拟在MATLAB中,我们可以利用Simulink工具箱来建立PLL锁相环的模型,并进行仿真分析。

我们需要使用Simulink中的基本模块,如正弦波源、相位比较器、低通滤波器、VCO和分频器等,按照PLL锁相环的基本结构进行搭建。

1. 步骤一:建立模型我们在Simulink中建立PLL锁相环的模型,将各个基本模块按照PLL 锁相环的基本结构进行连接,确保输入信号能够经过相位比较器、低通滤波器和VCO等模块,最终输出同步的信号。

锁相环实验报告锁相环实验报告一、实验目的本次实验的目的是了解锁相环(PLL)的原理和应用,掌握PLL电路的设计和调试方法,以及了解PLL在通信系统中的应用。

二、实验原理1. PLL原理锁相环是一种基于反馈控制的电路,由比例积分环节、相位检测器、低通滤波器和振荡器等组成。

其基本原理是将输入信号与参考信号进行比较,并通过反馈调整振荡频率,使得输入信号与参考信号同步。

2. PLL应用PLL广泛应用于通信系统中,如频率合成器、时钟恢复器、数字调制解调器等。

三、实验设备和材料1. 实验仪器:示波器、函数发生器等。

2. 实验元件:电阻、电容等。

四、实验步骤1. 搭建PLL电路并连接到示波器上。

2. 调节函数发生器输出正弦波作为参考信号,并将其输入到PLL电路中。

同时,在函数发生器上设置另一个正弦波作为输入信号,并将其连接到PLL电路中。

3. 调节PLL参数,包括比例积分系数和低通滤波器截止频率等,使得输入信号与参考信号同步。

4. 观察示波器上的输出波形,记录下PLL参数的取值。

五、实验结果与分析1. 实验结果通过调节PLL参数,成功实现了输入信号与参考信号的同步,并在示波器上观察到了稳定的输出波形。

记录下了PLL参数的取值,如比例积分系数和低通滤波器截止频率等。

2. 实验分析通过本次实验,我们深入了解了锁相环的原理和应用,并掌握了PLL电路的设计和调试方法。

同时,我们也了解到PLL在通信系统中的重要作用,如时钟恢复、数字调制解调等。

六、实验结论本次实验成功地实现了输入信号与参考信号的同步,并掌握了PLL电路的设计和调试方法。

同时也加深对于PLL在通信系统中应用的认识。

七、实验注意事项1. 在搭建电路时应注意接线正确性。

2. 在调节PLL参数时应注意逐步调整,避免过度调整导致系统失控。

3. 在观察示波器输出波形时应注意放大倍数和时间基准设置。

锁相环实验报告锁相环实验报告引言:锁相环(Phase-Locked Loop,简称PLL)是一种常见的电子系统控制技术,广泛应用于通信、测量、信号处理等领域。

本实验旨在通过设计和搭建一个基本的锁相环电路,深入理解锁相环的原理和应用。

一、实验目的本实验的主要目的是通过搭建锁相环电路,实现对输入信号的频率、相位的跟踪和稳定。

具体目标包括:1. 理解锁相环的基本原理和工作方式;2. 学会设计和搭建基本的锁相环电路;3. 通过实验验证锁相环的频率和相位跟踪性能。

二、实验原理1. 锁相环的基本原理锁相环是一种反馈控制系统,由相位比较器、低通滤波器、电压控制振荡器(Voltage Controlled Oscillator,简称VCO)和分频器组成。

其基本原理如下:(1)相位比较器:将输入信号和VCO输出信号进行相位比较,输出相位误差信号;(2)低通滤波器:对相位误差信号进行滤波,得到控制量;(3)VCO:根据控制量调整输出频率,使其与输入信号保持相位同步;(4)分频器:将VCO输出信号分频后反馈给相位比较器,形成闭环控制。

2. 锁相环的应用锁相环广泛应用于频率合成、时钟恢复、频率/相位调制解调等领域。

例如,在通信系统中,锁相环常用于时钟恢复电路,保证数据传输的稳定性和可靠性。

三、实验内容与步骤1. 实验器材与元件准备(1)信号发生器:产生待测频率的正弦信号;(2)锁相环芯片:如CD4046、PLL565等;(3)电阻、电容等元件:用于搭建锁相环电路;(4)示波器:用于观测和分析实验结果。

2. 搭建锁相环电路根据锁相环的基本原理和实验要求,设计和搭建一个简单的锁相环电路。

电路中包括相位比较器、低通滤波器、VCO和分频器等模块,并连接好电源和地线。

3. 实验操作步骤(1)将信号发生器的输出信号接入锁相环电路的输入端;(2)调节信号发生器的频率,观察锁相环的跟踪效果;(3)通过示波器观察锁相环输出信号的频率和相位稳定性。

pll锁相环的公式PLL锁相环是一种广泛应用于通信、计算机、控制等领域的电子设备,它的作用是将输入信号的频率锁定到参考信号频率上。

在PLL锁相环的设计中,计算PLL锁相环的公式是非常重要的,因为它能够推导出PLL锁相环的相关参数,从而影响其性能和稳定性。

本文将详细介绍PLL 锁相环的公式及其应用。

一、 PLL锁相环基本原理PLL锁相环是一种基于反馈的电子电路,可以将不同频率的信号锁定在一个稳定的参考信号上。

PL锁相环由三部分组成:比较器、低通滤波器和可变频率振荡器(VCO)。

比较器将输入信号和参考信号进行比较,输出的误差信号经过低通滤波器滤波后控制VCO的频率,以使得VCO的输出频率与参考信号的频率同步。

二、PLL锁相环的公式在PLL锁相环中,有以下基本参数:1. 相位差(Phase difference),用$\Delta\phi$ 表示。

它表示输入信号和参考信号的相位差,即两个信号的相位差。

2. 频率差(Frequency difference),用 $\Delta f$ 表示。

它表示输入信号和参考信号的频率差,即两个信号的频率之差。

3. 循环误差(Loop error),用 $\delta$ 表示。

它表示输出信号的相位与参考信号的相位差。

根据上述参数,PLL锁相环的公式如下:$$\delta = K_v\Delta f$$其中$K_v$是VCO的增益,即输出频率随输入电压的变化率。

它通常用Hz/Volts或MHz/Volts表示。

需要注意的是,上述公式中的单位应该保持一致。

例如,如果频率单位是kHz,那么增益单位应该是kHz/Volts。

三、PLL锁相环的应用PLL锁相环在通信、计算机、控制等领域都有广泛的应用。

例如:1. 频率合成器:通过PLL锁相环将输入信号锁定到参考信号的频率上,然后使用倍频器或分频器将输出信号的频率调整到所需要的频率,从而实现频率合成。

2. 时钟恢复:在数据传输中,使用PLL锁相环将接收到的数据中的时钟与本地时钟进行同步,以便正确接收数据。

数字锁相环原理数字锁相环(Digital Phase-Locked Loop,简称数字PLL)是一种广泛应用于通信、控制系统中的数字信号处理器。

它可以实现信号的频率和相位同步,对于数字通信系统中的时钟恢复、频率合成、信号解调等功能起着至关重要的作用。

本文将介绍数字锁相环的基本原理及其在通信系统中的应用。

数字锁相环由相位比较器、数字控制振荡器(DCO)、数字滤波器和锁定检测器组成。

其中,相位比较器用于比较输入信号和反馈信号的相位差,产生一个误差信号;数字控制振荡器根据误差信号调整输出频率;数字滤波器用于滤除噪声和抖动;锁定检测器用于检测数字锁相环是否已经锁定。

数字锁相环的工作原理可以简单描述为,首先,输入信号经过频率除法器和相位频率检测器,产生一个误差信号;然后,误差信号经过数字滤波器滤除噪声,再经过数字控制振荡器产生输出信号;最后,输出信号经过反馈回到相位比较器,形成闭环控制。

在闭环控制下,数字锁相环可以实现输入信号和输出信号的频率和相位同步。

数字锁相环在通信系统中有着广泛的应用。

在数字调制解调中,数字锁相环可以实现信号的时钟恢复和频率合成,保证接收端对发送端信号的准确解调;在频率合成器中,数字锁相环可以实现高稳定性的频率合成,满足通信系统对频率精度的要求;在通信系统中,数字锁相环还可以用于时钟同步和信号重构等功能。

总之,数字锁相环作为一种重要的数字信号处理器,在通信系统中有着广泛的应用。

它通过闭环控制实现输入信号和输出信号的频率和相位同步,保证了通信系统的稳定性和可靠性。

随着通信技术的不断发展,数字锁相环的应用范围将会更加广泛,对于提高通信系统的性能起着至关重要的作用。

通过本文的介绍,相信读者对数字锁相环的原理及其在通信系统中的应用有了更深入的了解。

数字锁相环作为一种重要的数字信号处理器,其原理简单而又实用,对于提高通信系统的性能有着重要的意义。

希望本文能对读者有所帮助,谢谢阅读!。

锁相环放大器的原理及应用锁相环放大器(Phase-locked loop amplifier,简称PLL放大器)是一种电子放大器,利用锁相环的原理,对输入信号进行放大,同时保持输出信号与输入信号的相位关系稳定。

锁相环放大器的原理主要包括三个基本模块:相位比较器、低通滤波器和VCO(Voltage-Controlled Oscillator)。

1. 相位比较器(Phase Comparator):相位比较器用于比较输入信号和反馈信号的相位差,并产生一个误差信号。

常见的相位比较器有乘法型相位比较器和加法型相位比较器。

2. 低通滤波器(Low Pass Filter):低通滤波器用于滤除相位比较器输出信号中的高频噪声,只保留误差信号的直流分量,同时具有一定的延迟作用。

3. VCO(Voltage-Controlled Oscillator):VCO是一个可通过电压控制频率的振荡器。

它的频率由输入的控制电压决定,通常与输入信号的频率相等,但相位可能会有一定的偏差。

通过调整VCO的控制电压,可以改变输出信号的相位与输入信号的相位之间的差距。

锁相环放大器的应用非常广泛。

以下是一些常见的应用场景:1. 时钟恢复:锁相环放大器经常用于从数字信号中恢复时钟信号。

通过将输入信号和本地时钟信号进行相位比较,可以产生一个误差信号,并通过调整VCO的频率,将输出信号的相位与输入信号的相位进行同步,从而恢复出准确的时钟信号。

2. 数据通信:锁相环放大器广泛应用于高速数据通信系统中。

通过对接收到的数据信号与本地时钟信号进行相位比较,并调整VCO的频率,可以保证接收到的数据信号与本地时钟信号的相位同步,从而实现可靠的数据传输。

3. 降噪增益:锁相环放大器可以用于降低输入信号中的噪声,并放大信号的幅度。

通过对输入信号和反馈信号进行相位比较,并通过调整VCO的频率,可以实现对信号的放大,并同时抑制输入信号中的噪声。

总之,锁相环放大器通过利用反馈控制的方式,可以实现对输入信号的放大,并保持输出信号与输入信号的相位关系稳定。

fpga 内部的锁相环FPGA内部的锁相环锁相环(Phase-Locked Loop,简称PLL)是一种常用的电子电路,用于产生稳定的频率和相位。

在FPGA(Field-Programmable Gate Array)内部,锁相环被广泛应用于时钟管理、数据通信和信号处理等方面。

本文将着重介绍FPGA内部的锁相环原理及其应用。

一、锁相环的基本原理锁相环由相位比较器、低通滤波器、电压控制振荡器(Voltage-Controlled Oscillator,简称VCO)和分频器等组成。

其基本原理是通过不断调整VCO的频率,使得VCO输出的信号与输入信号的相位差保持稳定。

具体工作过程如下:1. 相位比较器:将输入信号与VCO输出信号进行相位比较,产生误差信号。

2. 低通滤波器:对误差信号进行滤波,去除高频噪声,得到平滑的控制电压。

3. VCO:根据控制电压的大小改变输出频率,使得输出信号的相位与输入信号保持一致。

4. 分频器:将VCO输出信号进行分频,得到反馈信号与输入信号频率相同的参考信号。

通过不断调整VCO的频率,使得反馈信号与输入信号的相位差趋近于零,即实现了锁相。

二、FPGA内部的锁相环应用FPGA内部的锁相环主要用于时钟管理和数据通信方面,具有以下几个重要应用:1. 时钟管理:FPGA内部通常包含多个时钟域,不同模块需要使用不同的时钟频率。

锁相环可以提供稳定的时钟信号,并通过分频器将时钟信号分频为不同频率的时钟域,满足不同模块的时序要求。

2. 时钟重整:在数据通信中,接收端的时钟与发送端的时钟可能存在相位差和频率偏差。

锁相环可以通过跟踪接收到的数据信号,自动调整本地时钟的相位和频率,实现时钟重整,保证数据的准确传输。

3. 时钟生成:FPGA内部的PLL还可以用于产生非常高的频率时钟信号。

通过合理配置PLL的分频器和倍频器,可以生成所需的高频时钟信号,满足高速数据处理和通信的需求。

4. 时钟分频:FPGA内部的PLL还可以用于时钟分频,将高频时钟信号分频为所需的低频时钟信号。

锁相环的相位噪声传递函数锁相环(PLL)是一种常用的电路,用于将输入信号的相位与参考信号的相位保持一致。

相位噪声传递函数是描述锁相环中相位噪声传递的数学模型。

本文将介绍锁相环的基本原理和相位噪声传递函数,并探讨其在通信系统中的应用。

一、锁相环的基本原理锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)和分频器组成。

其基本原理是通过不断调节VCO的频率,使其输出信号的相位与参考信号的相位保持一致。

具体实现过程如下:1. 相位比较器:将输入信号和参考信号进行相位比较,产生一个误差信号。

2. 低通滤波器:对误差信号进行滤波,得到一个平滑的控制电压。

3. VCO:根据控制电压改变输出信号的频率,同时也改变其相位。

4. 分频器:将VCO的输出信号进行分频,得到参考信号。

通过不断的反馈调节,锁相环能够使VCO的输出信号与参考信号的相位保持一致,从而实现相位同步。

二、相位噪声传递函数的定义相位噪声传递函数是衡量锁相环中相位噪声传递特性的一种数学模型。

它描述了输入到输出的相位噪声传递情况,通常用频率响应函数的形式表示。

具体而言,相位噪声传递函数可以表示为:H(f) = K / (1 + jf/fc)其中,H(f)表示相位噪声传递函数,K表示增益,f表示频率,fc 表示截止频率。

三、相位噪声传递函数的分析相位噪声传递函数可以用于分析锁相环中相位噪声的特性。

从函数的形式可以看出,当频率接近截止频率时,相位噪声传递函数的值较小,说明锁相环对低频相位噪声具有较好的抑制能力。

而当频率远离截止频率时,相位噪声传递函数的值逐渐增大,说明锁相环对高频相位噪声的抑制能力较弱。

四、锁相环在通信系统中的应用锁相环在通信系统中有着广泛的应用。

其中,最常见的应用是时钟恢复和频率合成。

1. 时钟恢复:在数字通信系统中,接收端需要从接收到的信号中恢复出发送端的时钟信号。

锁相环可以通过将接收到的信号与本地时钟进行比较,并通过调节VCO的频率来实现时钟的恢复。

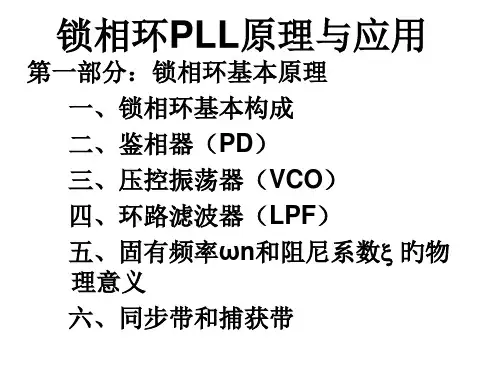

锁相环PLL原理与应用锁相环(Phase-Locked Loop, PLL)是一种常用的控制系统,广泛应用于电子和通信领域。

它可以用于频率合成、时钟恢复以及相位同步等应用中。

本文将对PLL的原理和常见的应用进行详细介绍。

PLL的原理:首先,参考信号经过相位比较器与VCO的输出信号进行比较。

相位比较器的输出为一个控制电压,表示两个信号之间的相位差。

这个控制电压经过低通滤波器进行滤波处理,得到一个平滑的控制电压,该电压用于调节VCO的频率。

VCO产生的频率与输入的控制电压成正比,通过调节控制电压,可以改变VCO的输出频率。

通过反馈控制的方式,当VCO的频率与参考信号接近时,相位比较器的输出误差会减小,最终收敛到零,实现了锁相环的目标。

在PLL中,分频器的作用是将VCO的高频输出信号分频得到一个相位稳定的低频信号,用作相位比较器的参考信号。

通过适当选择分频比,可以实现对VCO输出频率的精确控制。

PLL的应用:1.频率合成器:PLL经常被用于频率合成器的设计。

通过选择适当的参考频率和分频比,可以实现对输出频率的精确控制。

例如,在通信系统中,PLL被用于合成不同的载波频率用于不同用户之间的信号传输。

2.时钟恢复:在数字通信中,接收端需要从接收到的数据中恢复时钟信号。

PLL可以通过将接收到的数据作为参考信号,并控制VCO的频率,使得输出的时钟信号与发送端时钟同步。

3.数字时钟锁定:在数字系统中,不同的模块可能具有不同的时钟源,为了实现数据的正确和稳定传输,需要将不同的时钟源进行同步。

PLL可以用于将这些时钟同步,并控制其频率和相位,以便实现正确的数据传输。

4.相位同步:在通信系统中,要求不同的发送端和接收端之间的信号具有相同的相位特性,以便实现正确的信号传输。

PLL可以用于将这些信号进行相位同步,确保信号的准确传输。

在实际应用中,PLL还可用于频率测量、频率锁定等领域。

它的具体应用取决于实际需求。

在总结,锁相环是一种基于反馈控制的系统,通过将参考信号的相位与振荡器的输出信号进行比较,以实现对输出信号的频率和相位的稳定控制。

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。