如起始相差小于零,则相差与频差的符号与图1.2.2相 反。

2: △ω0>0, θe(0)=0

由式(1.2.8)得:

e(t) K o(1eK)te(0)eK·t···(1.2.8)

e (t )

0

K

(1 e Kt )

(1.2.11)

d e(t )

dt

0 e Kt

(1.2.12)

根据上两式,可画出相差和频差的变化曲线如 图1.2.3(a)、(b)所示。

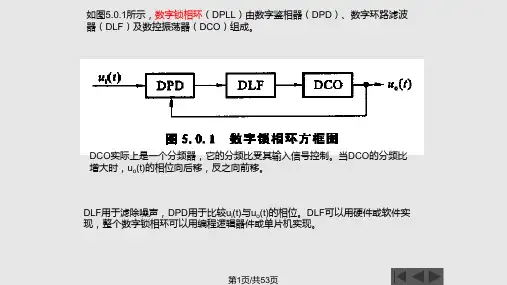

3. 数字锁相环(DPLL)

全部器件都是数字电路。所有的信号都是二进制 或多进制数字信号。

1.3 锁相环的工作状态

锁相环的输入信号不同,环路参数不同,其工作状态也 不同。本节直接给出不同输入信号下的环路工作状 态,而不作详细的数学分析。

输入信号可以是晶体振荡器,也可以来自接收机 的前置放大器,是一个调角(调频或调相)信号。 1.3.1 锁定状态

1.2 锁相环的构成及工作原理

1.2.1 锁相环的构成

无论多么复杂的锁相环都包含鉴相器(PD—Phase Detector) 、环路滤波器(LF—Loop Filter) 、以及压控 振荡器(VCO—Voltage Controlled Oscillator)这三个基

本部件。由这三个基本部件组成的锁相环如图1.1所 示,我们称为基本锁相环。

式中p为微分算子,F(p)为LF的传输算子。

VCO是一个电压/频率变换装置,它的频率ωv(t)随 uc(t)变化,一般把它们看作线性关系 ωv(t)=ω0+Kouc(t)…(1.2.3)

式中KO为VCO的控制灵敏度,简称为压控灵敏度,单 位是rad/(s·v)或Hz/v。 ω0为VCO的固有振荡频率, 即控制电压为0时的振荡频率。