锁相环原理整理ppt

- 格式:ppt

- 大小:857.01 KB

- 文档页数:26

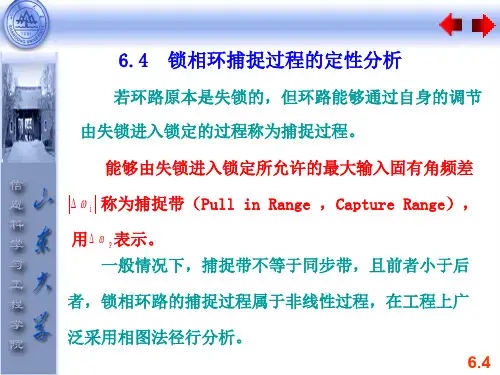

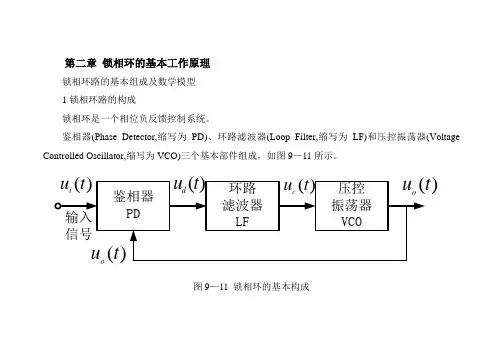

第二章锁相环的基本工作原理锁相环路的基本组成及数学模型1锁相环路的构成锁相环是一个相位负反馈控制系统。

鉴相器(Phase Detector,缩写为PD)、环路滤波器(Loop Filter,缩写为LF)和压控振荡器(Voltage Controlled Oscillator,缩写为VCO)三个基本部件组成,如图9—11所示。

)工作机理:PLL 环路利用输入与输出信号的相位误差()e t θ产生误差电压,通过环路滤波器滤除其中的高频成分与噪声,得到控制电压()c u t 去控制压控振荡器,使()e t θ朝缩小固有频差的方向变化,最终()e t θ稳定在某一很小的常数(称剩余相差),输入、输出信号频率相等i V ωω=,则环路被锁定了,即()e e t θθ∞=。

说明:图9—11为简图,省略了分频器。

PLL 电路中几个重要的频率。

鉴相器的两个输入信号;其一,晶体振荡器提供的参考输入信号 ()sin()i im i i u t V t ωθ=+; 其二,VCO 的输出电压信号。

开环时VCO 的自由振荡频率o ω,其输出电压为 ()cos()o om o o u t V t ωθ=+。

闭环时VCO 的频率受()c u t 控制,瞬时频率从oV ωω→,相应的输出()cos()o om V o u t V t ωθ=+。

为了研究的方便(请看课本P2),通常假设i u 和o u 的初始相位为零,i u 和o u 的相位均以o t ω作为参考,则1()sin[()]sin[()]i im o i o im o u t V t t V t t ωωωωθ=+-=+ (9.4.1)2()cos[()]cos[()]o om o V o om o u t V t t V t t ωωωωθ=+-=+ (9.4.2)式中,1()()i o t t θωω=-,为输入相位。

环路的固有频差 1()o i o d t dt θωωω∆=-=,其值等于输入参考信号频率与VCO 自由振荡频率之差。