4位串行进位加法器Max+plus II仿真

- 格式:docx

- 大小:159.97 KB

- 文档页数:3

四位全加器的VHDL实现通信0704 王学申0120703490117一、设计要求:采用QuartusII或Max+PlusII集成开发环境,利用VHDL硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

二、设计分析加法器是数字系统中的基本逻辑器件。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

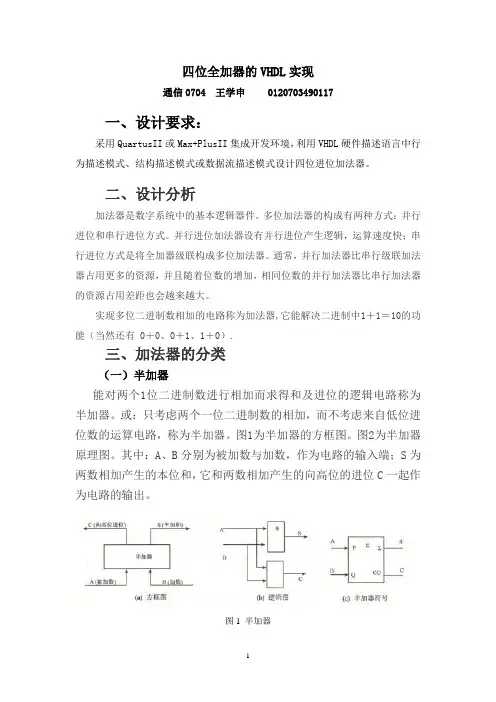

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).三、加法器的分类(一)半加器能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

图1为半加器的方框图。

图2为半加器原理图。

其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

图1 半加器图2 半加器原理图根据二进制数相加的原则,得到半加器的真值表如表1所列。

信号输入信号输出A B S C0 0 0 00 1 1 01 0 1 01 1 0 1表1 半加器的真值表由真值表可分别写出和数S,进位数C的逻辑函数表达式为:(1) C=AB (2)由此可见,式(1)是一个异或逻辑关系,可用一个异或门来实现;式(2)可用一个与门实现。

仿真结果如图3所示:图3 半加器仿真图(二)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

图4为全加器的方框图。

图5全加器原理图。

被加数A i、加数B i从低位向本位进位C i-1作为电路的输入,全加和S i与向高位的进位C i作为电路的输出。

能实现全加运算功能的电路称为全加电路。

新建Graphic Editor file,这个文件用来画电路图。

1点击2点击在画布上双击或右键第一项,会弹出器件放置对话框,以2端输入的与门为例名称为and2,(还有and3,and4,or2,nand2,not等,对于74LSXXX等器件,名称应改为74XXX,即去掉字母)双击输入器件名称用同样的方法,输入器件input和output,这主要是用来设置仿真波形的输入输出端口。

下图已经完成。

保存一下,设置文件名双击然后选择菜单file-->project-->set project to current file,如下图下面进行编译,否则在下面的仿真波形文件中无法找到输入输出端口,在菜单项中选择MAX-plus II Compiler出现下面对话框,Start吧,应该没有什么问题,如果有应检查电路连线,有时会貌似连上的。

下图已经成功了下面应建立波形文件,用于设置输入数字信号选择上如下最好先保存一下在菜单项中选择Node Enter Nodes from SNF,点击后,出现如下对话框,点击list选择观测的端口(我全选了),然后点击如下点击之出现在电路图中设置的输入输出端口点击出现如下界面,设置输入端口下面是设置b 为周期信号过程,选择b ,点击如下对于a ,任选一段,设为1,如下,然后保存一下输入文本清零置一设为未知态设为高阻态反转当前信号设为周期信号用数字设置信号 用数字设置信号,仅对组信号有效点击 初始值周期选择菜单项MAX+plus II Simulator, 弹出如下对话框,Start成功了C为输出结果将a和b组合的方法,同时选择a和b ,点击右键选择Enter Group…,然后弹出对话框,起个名子,OK进制选择效果如下library ieee;use std_logic.1164_all;entity name_1 isport(a,b:in bit;f:out bit);end name_1;architecture name_2 ot name_1 is beginprocess(a,b)variable tmp: bit_vector(0 to 1); begintmp:=a&b;case tmp iswhen"00"=>f<='1';when"01"=>f<='1';when"10"=>f<='1';when"11"=>f<='0';end case;end process;end name_2;。

可编程逻辑器件软件MAX+ PLUS IIMAX+ PLUS II( Multiple Array Matrix and Programmable Logic User S ystem II )是Altera公司为可编程逻辑器件PLD(Programming Logic Driver)器件应用、逻辑电路设计、仿真开发的软件平台。

MAX + PLUSⅡ运行在Windows 操作系统的软件。

它的功能全,可以使用的器件类型比较广泛。

MAX+ PLUS II 的主要技术特点如下:1) 适用范围广泛。

MAX+ PLUS II除了支持Altera系列PLD外,也支持在其它芯片上设计逻辑电路。

2) 与器件结构独立。

MAX+ PLUS II提供了与器件结构独立的设计环境和综合功能,用户可以在设计过程中不考虑具体的器件结构。

3) 通用性强。

MAX + PLUS II的软件设计环境是开放的。

它符合工业标准的EDA软件。

它提供了与EDA工具的接口。

对大多数EDA工具,接口由MAX+ PLUS II软件内部的相关框架协议自动完成。

4) 兼容性好。

MAX + PLUS II软件可与其它工业标准设计输入、综合与校验工具链接。

用户可使用Altera设计输入工具去建立逻辑设计。

使用MAX + PLUS II能够对Altera的器件进行逻辑电路设计、运行和仿真。

5) 自动化程度高。

MAX + PLUS II软件集成了设计输入、处理与校验功能。

他可以减轻设计人员的工作量,加快动态调试,缩短开发周期,取得较高的设计效率。

6) 帮助系统完善。

MAX + PLUS II软件的帮助系统功能齐全,有丰富的图表与设计实例,为设计者提供很大的方便。

下面介绍使用MAX + PLUS II软件的图形编辑器设计和仿真一位8421BCD码转换成余3 BCD码合逻辑电路,使用VDHL语言设计和仿真三位二进制加1计数器同步时序逻辑电路。

通过学习,初步掌握MAX + PLUS II软件的使用方法。

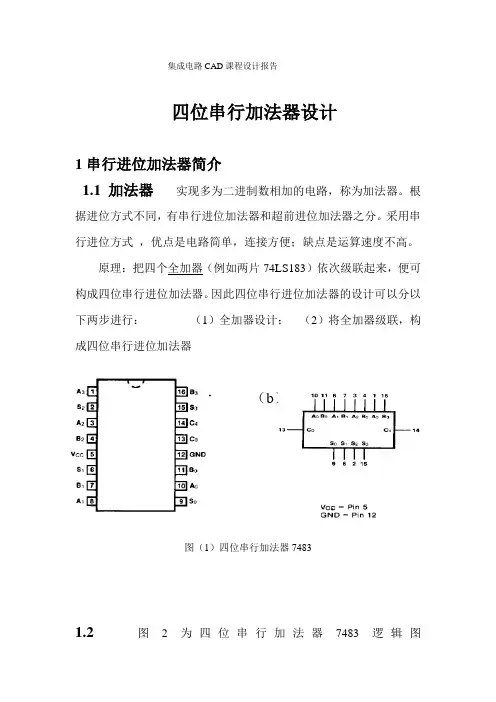

集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uAV oHmin=4.4V②输出低点平时|IoH|<=20mAV oHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF的电容负载代替10个TTL电路来计算tr、tf②输入V为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn oxN ndsn -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax0m in-⎪⎪⎭⎫⎝⎛=TT n n μμ(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 V oHmin=4.4V tr=tf① 以Ioh<=20uA时V oHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V ,V ohmin=4.4v,Vtp=0.8V ,经计算可得∆∆===⎪⎭⎫⎝⎛233034956.164m inn L W []202)()(2oh tp i dd tp i oxp p ohV V V V V V C L W I -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax 0m in-⎪⎪⎭⎫⎝⎛=T T n p μμ∆∆===⎪⎭⎫⎝⎛21532227.7pL W②tr=tp 的条件计算:CMOS 中αp=αn所以2.2 输入级设计ddtp p V V =αddtn n V V =αddp L p V k C =τ()⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡-⎪⎪⎭⎫ ⎝⎛--+--=p n n n n f arth t αααατ111.011)1.0(2p pn n pn n p f r LW L W k k t t μμττ⎪⎭⎫⎝⎛⎪⎭⎫⎝⎛===⎪⎪⎭⎫ ⎝⎛∆∆===⎪⎭⎫⎝⎛233034956.164minn L W ∆∆==⎪⎭⎫⎝⎛275931138minn L W ∆∆===⎪⎭⎫⎝⎛233034956.164minn L W输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间 V1*=ViLmax+Vihmin=1.4V∆∆===⎪⎭⎫⎝⎛223312p L W∆∆==⎪⎭⎫ ⎝⎛231.546内p L W式中βk=kn/kp,Vdd=5V ,Vtn=0.7V ,Vi*=1.4V , βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算内部反相器的负载电容: ①本级漏极的PN 结电容Cpn ②下级的栅电容Cc1 ③连线杂散电容Cs Cpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(∆∆=⎪⎭⎫⎝⎛=⎪⎭⎫ ⎝⎛2230W np R pl nl L L W μμβ∆∆==⎪⎭⎫⎝⎛22303345nlL W ∆∆==⎪⎭⎫⎝⎛231.546plL W ∆∆===⎪⎭⎫⎝⎛223312p L WCpn 和Cl :N 管 其衬底是P 型,所以 NB=2⨯1016 cm-3 设结深Xi=0.5um R □=20Ω/□对于P 管Cpn=而CC1可以由:Cc1=10Cs-Cpn 求出。

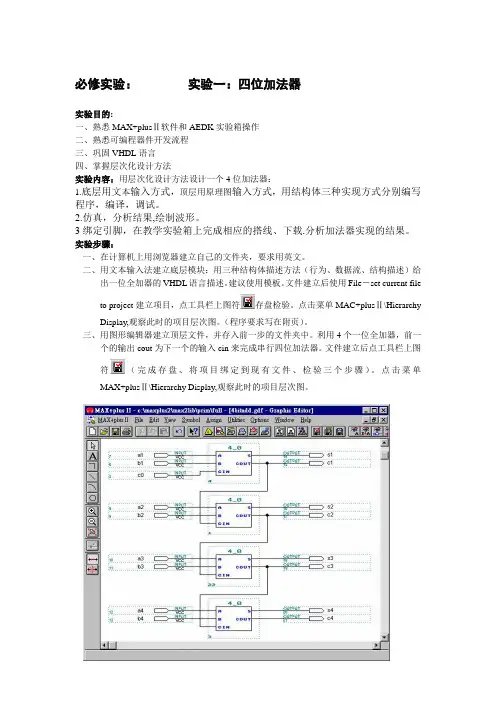

必修实验:实验一:四位加法器实验目的:一、熟悉MAX+plusⅡ软件和AEDK实验箱操作二、熟悉可编程器件开发流程三、巩固VHDL语言四、掌握层次化设计方法实验内容:用层次化设计方法设计一个4位加法器:1.底层用文本输入方式,顶层用原理图输入方式,用结构体三种实现方式分别编写程序,编译,调试。

2.仿真,分析结果,绘制波形。

3绑定引脚,在教学实验箱上完成相应的搭线、下载.分析加法器实现的结果。

实验步骤:一、在计算机上用浏览器建立自己的文件夹,要求用英文。

二、用文本输入法建立底层模块:用三种结构体描述方法(行为、数据流、结构描述)给出一位全加器的VHDL语言描述。

建议使用模板。

文件建立后使用File-set current file to project建立项目,点工具栏上图符存盘检验。

点击菜单MAC+plusⅡ\HierarchyDisplay,观察此时的项目层次图。

(程序要求写在附页)。

三、用图形编辑器建立顶层文件,并存入前一步的文件夹中。

利用4个一位全加器,前一个的输出cout为下一个的输入cin来完成串行四位加法器。

文件建立后点工具栏上图符(完成存盘、将项目绑定到现有文件、检验三个步骤)。

点击菜单MAX+plusⅡ\Hierarchy Display,观察此时的项目层次图。

四、作时序仿真,画出时序仿真波形图。

(四位数据要求以总线形式显示)五、选择器件(max epm7128s-15),绑定引脚,设置下载接口,编程下载。

以按键模拟数字(注,板上无多余按键,C0不接)开关设置S2-7,OFF L8-L1 不允许显示实验注意事项:本实验的教学录像仅供不熟练者参考,已掌握者可以放手自己操作。

不应只是跟着录像走过场,而要真正理解MAX+plusⅡ这种EDA软件的设计流程,和层次化设计中的模块划分。

实验过程大约需要3-4个小时。

如果事先设计底层全加器程序,并复习课上内容和书上有关章节,理清设计流程,可以节约时间,并且效果会更好。

使用EDA软件对四位二进制计数器进行仿真吴璋(安庆师范学院物理与电气工程学院安徽安庆246011)指导老师:郑江云摘要:本文介绍了VHDL 语言及其基本特点,讨论了VHDL 语言在EDA 中的诸多优点,并以四位二进制计数器电路的设计为例,应用 Max + Plus Ⅱ工具软件和 EDA 实验箱实现了计数器的功能,结果与设计指标之间满足一致性要求。

关键字:Max + Plus Ⅱ工具软件,电子设计自动化,计数器0 引言目前,随着电子技术的飞速发展,数字系统规模越来越大,传统的电路设计已难以适应复杂电子系统的设计要求。

从而使得电子设计自动化( EDA)技术迅速发展,成为硬件电子电路设计领域中的主要设计手段。

而VHDL语言则是EDA的关键技术之一,它采用了自顶向下的设计方法,即在整个设计流程中各设计环节逐步求精的过程。

通俗地讲,就是将设计系统自上向下地分解成各个模块,对设计的每个独立模块可以指派不同的工作小组来做,之后将做好的各个模块作为底层文件来构成顶层文件,从而完成系统硬件的整体设计。

计数器是数字电路中一种极其普通的器件,其应用范围十分广泛,可以说任何自动控制装置的核心部件都是由一个或几个计数器在起作用。

一个系统的性能好坏,在很大程度上可以从计数器设计的科学程度来体现。

在这里,笔者就图形输入法和VHDL语言输入法对四位二进制计数器进行设计和仿真。

1 图形输入法的设计仿真思路具体步骤为:第一步:进入MAX+PLUSⅡ运行环境第二步:建立项目选择File/Project/Name 显示对话框将目录directories 选择为Max2Work,,输入project Name为lizi/first,然后按OK按钮,出现是否建立子目录lizi/first的询问,再输入OK。

第三步:在file中选New,出现对话框,然后选择第一项Graphic Editor file,选OK,出现标题为Graphic Editor Untitled的窗口。

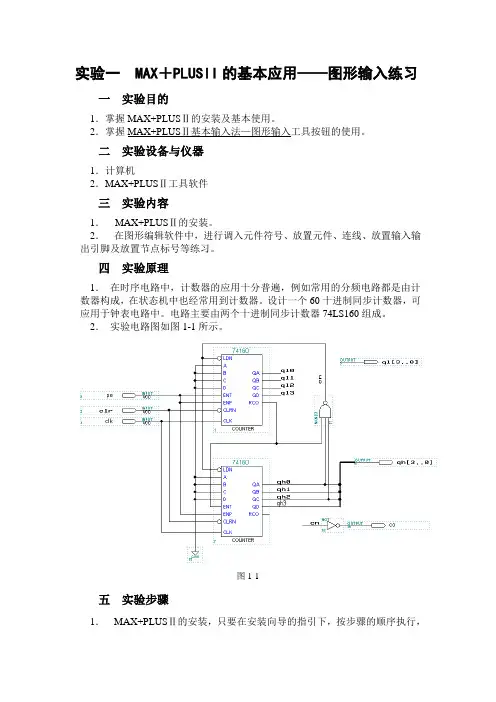

实验一 MAX+PLUSII的基本应用——图形输入练习一实验目的1.掌握MAX+PLUSⅡ的安装及基本使用。

2.掌握MAX+PLUSⅡ基本输入法—图形输入工具按钮的使用。

二实验设备与仪器1.计算机2.MAX+PLUSⅡ工具软件三实验内容1.MAX+PLUSⅡ的安装。

2.在图形编辑软件中,进行调入元件符号、放臵元件、连线、放臵输入输出引脚及放臵节点标号等练习。

四实验原理1.在时序电路中,计数器的应用十分普遍,例如常用的分频电路都是由计数器构成,在状态机中也经常用到计数器。

设计一个60十进制同步计数器,可应用于钟表电路中。

电路主要由两个十进制同步计数器74LS160组成。

2.实验电路图如图1-1所示。

图1-1五实验步骤1.MAX+PLUSⅡ的安装,只要在安装向导的指引下,按步骤的顺序执行,即可完成。

2.MAX+PLUSⅡ安装完毕后,在第一次运行时需要进行License设臵,然后才可以使用。

3.启动MAX+PLUSⅡ软件,进入MAX+PLUSⅡ管理窗口。

进行设计项目的建立。

4.在MAX+PLUSⅡ管理窗口的File菜单下选择New选项或单击按钮,然后再选择Graphic Editor file后,单击OK按钮,可建立图形输入文件。

5.从库中调入元件符号。

在图形编辑区内双击鼠标左键或单击鼠标右键,在随后弹出的菜单中选择Enter Symbol即可直接键入元件名,调出元件,也可以选择元件库。

MAX+PLUSⅡ提供了4种库文件,其功能见表1-1所示。

表1-1 图形编辑器提供的库功能6.单击连线工具栏的按钮,光标变成,‚+‛形,单击连线起始端按住鼠标左键拖动至结束端松开,连线结束。

若要删除某连线,可单击连线使其变成高亮(红色),再按,Delete键,即可删除。

7.图形编辑时,在连线复杂的地方(总线),可用节点标号来连线。

用节点标号连线不区分大小写。

8.放臵输入输出引脚。

在符号库中调入元件符号对话框中,键入,input‛或,output‛即可将输入或输出引脚添加到电路图中,新放臵的输入输出引脚需要修改引脚名称。

第三章MAX+PLUS II 使用指南世界上各大可编程逻辑器件的生产厂商都有各自的EDA开发系统,比如Lattic公司的Synario;Xilinx公司的Foudation等,本章选取美国Altera公司的MAX+PLUS II,介绍如何利用它进行PLD设计。

MAX+PLUS II 开发系统是美国Altera公司自行设计的CAE软件平台,具有易学、易掌握的特点。

MAX+PLUS II 的全称为Multiple Array Matrix and Programmable Logic User System,可安装在具有Windows 95/98或Windows NT4.0的PC机上,要求硬件至少具备16M内存、80M硬盘。

在MAX+PLUS II软件平台上利用PLD来设计系统可通过三大步骤来完成,即设计项目的输入、设计项目的验证和设计项目的处理。

为了形象、有效、快速地掌握Max+plus II 的使用方法,本章通过一四位二进制加法器的设计实例来介绍整个设计的详细过程。

实例中所用的芯片是Altera公司可编程逻辑器件EPF10K10LC84-3,读者可使用EDA 实验开发系统来演示设计的结果。

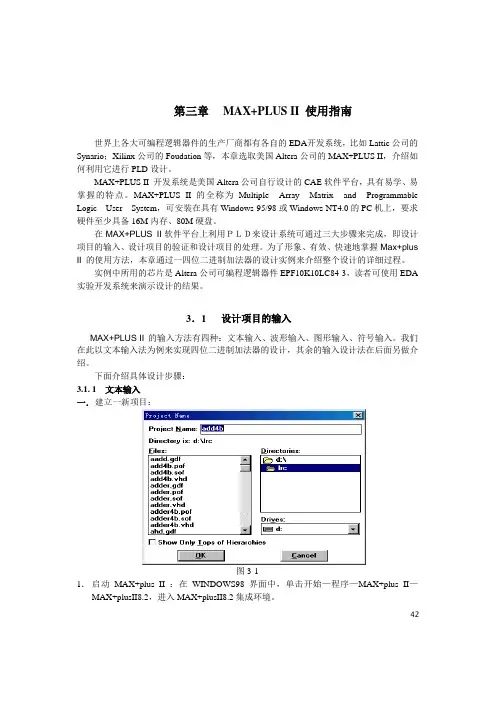

3.1 设计项目的输入MAX+PLUS II 的输入方法有四种:文本输入、波形输入、图形输入、符号输入。

我们在此以文本输入法为例来实现四位二进制加法器的设计,其余的输入设计法在后面另做介绍。

下面介绍具体设计步骤:3.1. 1 文本输入一.建立一新项目:图3-11.启动MAX+plus II :在WINDOWS98界面中,单击开始—程序—MAX+plus II—MAX+plusII8.2,进入MAX+plusII8.2集成环境。

422.选中File—Project—Name,显示对话框图3-1。

3.在Project Name框中,键入add4b(此文件名可任取,但必须与源程序中的实体名字相同)。

若想改变add4b所属目录,用户可在Directories窗口中修改。

电子设计(EDA)实验报告(4位二进制加法器)一、实验名称4位二进制加法器二、实验目的掌握输入编辑原理图文件的方法;掌握编译原理图文件的方法;掌握仿真原理图文件的方法;理解Quartus 2 器件编程的方法三、实验环境计算机与Quartus 2 工具软件四、实验原理图、源程序entity halfadd isport(a1,b1:in bit;s1,c1:out bit);end ;architecture a of halfadd isbeginprocess(a1,b1)begins1<=a1 xor b1 after 10ns;c1<=a1 and b1 after 10ns;end process;end a;entity orgate isport(a,b:in bit;o:out bit);end orgate;architecture a of orgate isbegino<=a or b;end a;entity fulladd isport(i1,i2,c_in:in bit;fs,c_out:out bit);end ;architecture a of fulladd issignal temp_s,temp_c1,temp_c2:bit; component halfaddport(a1,b1:in bit;s1,c1:out bit);end component;component orgate port(a,b:in bit;o:out bit);end component;beginu0:halfadd port map(i1,i2,temp_s,temp_c1);u1:halfadd port map(temp_s,c_in,fs,temp_c2); u2:orgate port map(temp_c1,temp_c2,c_out); end a;entity add4 isport(a,b:in bit_vector(3 downto 0);cin:in bit;fs:out bit_vector(3 downto 0);cout:out bit);end add4;architecture a of add4 issignal temp_co0,temp_co1,temp_co2:bit; component fulladd isport(i1,i2,c_in:in bit;fs,c_out:out bit);end component;beginu0:fulladd port map(a(0),b(0),cin,fs(0),temp_co0);u1:fulladd port map(a(1),b(1),temp_co0,fs(1),temp_co1);u2:fulladd port map(a(2),b(2),temp_co1,fs(2),temp_co2);u3:fulladd port map(a(3),b(3),temp_co2,fs(3),cout);end a;五、实验波形图及分析延迟12.08ns。

四位串行累加器原理仿真引言:随着科技的不断发展,计算机已经成为了人们日常生活中不可或缺的一部分。

而计算机中最基本的运算单元就是加法器。

本文将以“四位串行累加器原理仿真”为中心,详细阐述四位串行累加器的工作原理,探讨其在计算机中的应用。

一、四位串行累加器的定义与结构四位串行累加器是一种用于进行多位二进制数相加运算的电子器件。

它由四个触发器、一个模2加法器和一个时钟信号组成。

四位串行累加器能够完成两个四位二进制数的加法运算,并将结果输出。

二、四位串行累加器的工作原理四位串行累加器的工作原理如下:1.初始化:将输入端接入待相加的两个四位二进制数,将输出端设为0。

2.模2加法器:将两个输入数的最低位与输出端的值输入模2加法器中,得到一个输出结果和一个进位信号。

3.触发器:将模2加法器的输出结果输入到四个触发器中,同时将进位信号输入到最高位触发器中。

4.时钟信号:通过时钟信号控制触发器的工作,每个时钟周期,触发器将将其输入值输出到下一个触发器中。

5.输出结果:在每个时钟周期结束时,将最低位触发器的输出结果输出到输出端。

三、四位串行累加器的应用四位串行累加器在计算机的运算器中有着广泛的应用。

它能够完成多位二进制数的加法运算,是实现计算机算术运算的重要组成部分。

1.加法运算:四位串行累加器能够将两个四位二进制数相加,并输出结果。

这对于计算机进行加法运算非常重要,例如在进行浮点数运算、整数加法等方面都起到了关键作用。

2.计数器:四位串行累加器也可以被用作计数器,通过输入一个固定值来实现对计数器的增加或减少。

这在计算机的时序控制中非常常见,例如时钟频率的控制、计时器的运算等。

四、四位串行累加器原理仿真的优势与挑战1.优势:-简单有效:四位串行累加器的结构相对简单,能够实现基本的加法运算。

-低功耗:由于只有一个模2加法器和四个触发器,四位串行累加器的功耗较低。

-可扩展性:通过增加更多的位数,可以实现更大范围的二进制数相加运算。

四位串行进位加法器设计集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uA VoHmin=4.4V②输出低点平时|IoH|<=20mA VoHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF 的电容负载代替10个TTL 电路来计算tr 、tf ②输入V 为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn ox N n dsn -----⎪⎭⎫ ⎝⎛=μmax0min 2ox SiOox t C εε=(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 VoHmin=4.4Vtr=tf① 以Ioh<=20uA时VoHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V,Vohmin=4.4v,Vtp=0.8V,230max 0min -⎪⎪⎭⎫ ⎝⎛=T T n n μμ∆∆===⎪⎭⎫ ⎝⎛233034956.164min n L W []202)()(2oh tp i dd tp i ox p p oh V V V V V V C L W I -----⎪⎭⎫ ⎝⎛=μmax 0min 2ox SiO ox t C εε=230max 0min -⎪⎪⎭⎫ ⎝⎛=T T n p μμ经计算可得②tr=tp 的条件计算:CMOS 中αp=αn所以 ∆∆===⎪⎭⎫ ⎝⎛21532227.7pL W dd tp p V V =αddtn n V V =αdd p L p V k C =τ()⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡-⎪⎪⎭⎫ ⎝⎛--+--=p n n n n f arth t αααατ111.011)1.0(2p p n n p n n p f r L W L W k k t tμμττ⎪⎭⎫ ⎝⎛⎪⎭⎫ ⎝⎛===⎪⎪⎭⎫ ⎝⎛∆∆===⎪⎭⎫ ⎝⎛233034956.164min n L W ∆∆==⎪⎭⎫ ⎝⎛275931138minn L W2.2 输入级设计输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸 ∆===⎪⎭ ⎝236.164min n L ∆∆===⎪⎭⎫ ⎝⎛223312p L W∆∆==⎪⎭⎫ ⎝⎛231.546内p L W(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间V1*=ViLmax+Vihmin=1.4V式中βk=kn/kp,Vdd=5V,Vtn=0.7V,Vi*=1.4V, βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算 内部反相器的负载电容:①本级漏极的PN 结电容Cpn1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(∆∆=⎪⎭⎫ ⎝⎛=⎪⎭⎫ ⎝⎛2230W n p R plnl L L W μμβ∆∆==⎪⎭⎫ ⎝⎛22303345nl L W ∆∆==⎪⎭⎫ ⎝⎛231.546pl L W ∆∆===⎪⎭⎫ ⎝⎛223312p L W②下级的栅电容Cc1③连线杂散电容CsCpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为Cpn 和Cl :N 管 其衬底是P 型,所以 NB=2⨯1016 cm-3设结深Xi=0.5um R □=20Ω/□对于P 管Cpn= )(10726.1100.19.31085.8101005C 14482014F t A s oxF SiO Al ---⨯=⨯⨯⨯⨯⨯⨯==-εεϕεε2021021C C p jn n jp Si qN C jpn ===++2ln iB n N N q kT =ϕ318õ10862.7R 1N -⨯==cm x q j μ28/10195.2cm F C p jN -+⨯=28/101396.1cm F C N jP -+⨯=Cp n Cn p+++而CC1可以由:Cc1=10Cs-Cpn求出。

Max+Plus II 利用总结(一)Max+Plus II 是一个优秀的VHDL仿真和EPLD编程软件,它能够完成数字电路图、VHDL的仿真后优化,并将完成的POF文件下载到相应的可编程器件中。

它的编程-设置-仿真模式和OrCAD差不多,都要通过这三步。

拿电路图输入来讲,它需要第一输入电路图,选择编程器件型号,然后编译,在编译进程中能够通过观察rpt文件取得运算机对管脚的赋值,若是用户不中意能够自己赋值,方式是选择Maxplusii Floorplan Editor,再选择Layout Device View和Layout Current Assignments Floorplan,显示当前的管脚分派情形[注意那个地址需要说明的是关于每一个编辑器,MAXPLUSII都对其挪用不同的菜单组],在那个地址用户能够自己配置适合的管脚。

正确编译后就进入仿真时期,在仿真时期,第一挪用MAXPLUSII WaveForm Editor,设置仿真的时长和仿真的最小步长,然后选择需要仿真显示的管脚名称,编辑输入波形,就取得仿真结果,按Open SCF,就可观看仿真波形。

波形正确,也确实是达到特定的功能了,咱们就能够够将程序下载到EPLD中,具体方式是选择MAXPLUSII Programmer,然后配置pof文件,就通过下载电缆和编程器将程序烧写到相应的芯片中去。

所用到的功能有:Hierarchy Display:用以显示本工程(或项目)的结构,包括其文件组成等。

Graphic Editor:图形编辑器,用来输入数字电路图。

Symbol Editor:符号编辑器,用来编辑符号。

Text Editor:文本编辑器,用来编辑VHDL程序。

WaveForm Editor:波形编辑器,用来编辑仿真波形。

Floorplan Editor:管脚编辑器,用来配置芯片管脚。

Compiler:编译器,用来编译VHDL程序、电路等,具有过失功能。

VHDL与复杂数字系统设计

上机实验1:开发工具Max+plus II的使用

一、实验目的:

1、学习开发工具Max+plus II的安装;

2、掌握图形输入法设计简单逻辑电路的操作步骤。

二、实验内容:

1、利用基本元件库,采用图形输入法设计四位并行全加器电路;

三、实验过程:

1、一位全加器电路

原理简述:两个一位数相加,则令S为相加的和,而CO为向高位的进位。

2、电路原理图:

3、电路检查:

4、电路符号图:

2、4位串行进位加法器

原理简述:四位串行进位加法器就是将四个一位加法器串联,低一位的进位就是上一位的CI输入。

最低位的进位为低低电平(没有进位)。

电流原理图

电路检查:

有以上的电路图所仿真得出的波形图为:

图形与理论的结果相同。

结论:四位串行进位加法器的电路图就是以上所得的电路图。

与实际的图形相比有延时。

但总的图形是非常吻合的。