Verilog语法手册

- 格式:pptx

- 大小:91.35 KB

- 文档页数:4

verillog语法

Verilog是一种硬件描述语言,用于描述数字电路和系统。

以下是Verilog 的基本语法:

1. 注释:Verilog中的注释以“//”开头,一直延续到该行的末尾。

另外,多行注释以“/”开始,以“/”结束。

2. 数字表达方式:在Verilog中,数字的表示方式可以是十进制、八进制或二进制。

例如,8'b表示一个8位的二进制数。

3. 数据类型:Verilog中有四种数据类型,分别是wire(线网型)、reg (寄存器型)、integer(整数型)和parameter(参数型)。

其中,wire 类型用于表示物理连线,reg类型表示数据存储单元。

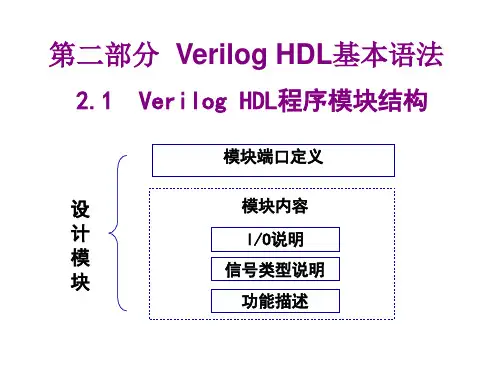

4. 模块:Verilog中的模块是电路的基本单元,由输入、输出和内部信号组成。

模块的端口用于连接外部信号,内部信号用于描述电路的行为。

5. 语句:Verilog中的语句可以分为赋值语句、控制语句和过程语句。

赋值语句用于给变量赋值,控制语句用于控制流程,过程语句用于描述电路的行为。

6. 任务和函数:Verilog中的任务和函数用于实现特定的功能。

任务和函数的使用可以减少代码的重复,提高代码的可维护性。

7. 系统任务和系统函数:系统任务和系统函数是Verilog提供的用于实现特定系统级功能的任务和函数。

例如,$display系统任务用于在仿真时显示信息。

以上是Verilog的基本语法,当然还有更多的语法和概念需要学习和掌握。

建议查阅相关的Verilog教程或书籍,以深入了解Verilog的语法和用法。

verilog module语法Verilog Module语法Verilog是一种硬件描述语言,用于设计和建模数字电路。

在Verilog中,模块(Module)是描述电路功能的基本单元。

本文将详细介绍Verilog的模块语法。

1. 模块声明在Verilog中,模块的声明以`module`关键字开头,后面跟着模块的名称,并用括号括起来,括号中是模块的输入和输出端口。

例如:```verilogmodule MyModule(input A, input B, output C);```上述代码定义了一个名为MyModule的模块,有两个输入端口A和B,一个输出端口C。

2. 端口声明在模块的括号中,可以用逗号分隔的方式声明多个端口。

每个端口可以是输入端口(input)、输出端口(output)或双向端口(inout)。

例如:```verilogmodule MyModule(input A, input [7:0] B, output [7:0] C, inout D);```上述代码中,A是一个输入端口,B是一个8位输入端口,C是一个8位输出端口,D是一个双向端口。

3. 内部信号声明在模块中,可以声明内部信号(wire或reg),用于在模块内部进行信号传输或存储。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;reg [7:0] E;// 省略其他代码endmodule```上述代码中,D是一个wire类型的内部信号,E是一个8位reg类型的内部信号。

4. 逻辑表达式在模块中,可以使用逻辑运算符和条件语句来实现电路的逻辑功能。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;assign D = A & B;always @(posedge D)C <= ~C;endmodule```上述代码中,使用`&`逻辑与运算符计算A和B的与运算结果,并将结果赋值给D。

verilog 原语例化语法Verilog是一种硬件描述语言,可以用来描述和设计数字集成电路。

Verilog原语是一组内置的底层硬件建模功能,用于描述和建模集成电路中的基本单元。

文本中将深入探讨Verilog原语例化语法。

1、例化指令的基础语法在Verilog中,使用“module”指定一个硬件模块,然后使用“endmodule”关闭该模块。

Verilog实例化使用“module” 关键字来引用硬件模块。

例化语法:module module_name (port_list);... module body ...endmodule这里,模块名称表示实例化模块的名称,接下来是端口列表,是模块是否双向、数据类型等信息,接着是模块主体。

2、例化语法示例下面是一个简单的 Verilog 原语例化示例,使用了常见的内置原语之一 AND。

module example AND_INST (output reg y, input a, b);and and_inst(y, a, b);endmodule上述例化将输入端口a和b连接到与门原语,将结果存储在输出端口y中。

3、实例化复合模块通过例化,可以将单个硬件原语连接到模块中。

模块可以嵌套,这意味着模块自身可以包含其他模块。

在这种情况下,我们需要进行复杂例化,以适应其包含的模块。

在下面的示例中,我们将实例化两个硬件模块,并将它们连接在一起,以便每个模块都处理一部分数据。

其中第一个模块处理第一位和第二位,第二个模块处理第三位和第四位。

module example(input [0:3] data_in, output [0:3]data_out);wire [1:0] a;wire [1:0] b;wire [1:0] c;wire [1:0] d;module1 m1(a, b, data_in[0], data_in[1]);module2 m2(c, d, data_in[2], data_in[3]);endmodule在上面的示例中,我们使用了 comma ',' 分隔符来分别为每个模块声明输出端口,以便在主模块中使用。

verilog基本语法

1. 模块:verilog模块用于描述感兴趣的功能系统以及设备行为,从而给出输入和输出之间的关系。

2. 变量:verilog中的变量可以定义为硬件控制的行为或信号路径。

3. 宏定义:verilog使用宏`define`来定义新的字符或文本,可用于

提高程序可读性和管理性。

4. 注释:verilog支持两种注释形式,即行注释和块注释,行注释以

`//`开头,块注释以`/*`开头,以 `*/`结尾。

5. 关键字:verilog使用了一系列关键字来指定硬件控制行为,输入、输出、时序延迟和引用等。

6. 命令:verilog提供了一系列命令来描述功能,包括`initial`,

`always`,`@`和`begin`等等。

7. 模型:verilog中的模型用于定义和控制硬件的输入和输出行为,

这些模型可以被定义为多个状态和条件的序列。

Verilog-A语法实用指南Verilog-A语法是描述模拟电路行为的一种编程语言。

它可以用于描述电路的行为和功能,是数字电路设计中常用的一种语言。

本文将从Verilog-A语法的基本特点、常用语法以及示例应用等方面展开介绍,希望可以为初学者提供一些指导和帮助。

一、Verilog-A语法的基本特点1. 语法简洁明了:Verilog-A语法采用了类似C语言的结构,采用了分号作为语句结束符,使得代码具有良好的可读性。

2. 强大的模块化功能:Verilog-A语法支持模块化的设计,可以将电路设计分为多个模块,每个模块完成不同的功能。

3. 丰富的数据类型:Verilog-A语法支持多种数据类型,包括整型、实型、布尔型等,能够适应不同的应用场景。

4. 可扩展性强:Verilog-A语法可以方便地扩展新的功能和特性,使得它在大型项目中也能够得到应用。

二、Verilog-A语法的常用语法1. 模块定义:使用module关键字定义一个模块,模块内包含输入端口、输出端口以及内部逻辑。

2. 参数定义:使用parameter关键字定义参数,可以在模块中使用这些参数。

3. 时序控制:使用initial关键字定义初始条件,使用always关键字定义条件触发的操作。

4. 信号赋值:使用assign关键字完成信号之间的赋值操作。

5. 行为描述:使用initial和always关键字描述电路的行为。

6. 分支结构:使用if...else...语句完成条件判断。

7. 循环结构:使用for和while等关键字完成循环操作。

三、Verilog-A语法的示例应用1. 模拟电路设计:Verilog-A语法可以用于模拟电路的设计和验证,包括数字电路和模拟电路。

2. 信号处理:Verilog-A语法可以用于实现信号的采集、处理和输出。

3. 控制系统:Verilog-A语法可以用于描述控制系统的行为和功能,包括PID控制、状态空间控制等。

4. 通信系统:Verilog-A语法可以用于描述通信系统的行为和功能,包括调制解调、编解码等。

Verilog语法简易教程Verilog是硬件描述语言(HDL)之一,主要用于硬件设计和仿真。

它于1984年由一家名为Gateway Design Automation的公司开发,并于1985年推出。

Verilog以其简单易学的语法和强大的功能而闻名于世。

本简易教程将向您介绍Verilog的基本语法和常用结构。

它包括模块化设计,数据类型,运算符,条件语句,循环语句和时序建模等内容。

首先,让我们先来了解Verilog中的模块化设计。

在Verilog中,设计是通过定义和连接模块来完成的。

每个模块由输入输出端口和内部逻辑组成。

以下是一个简单的Verilog模块的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```上述代码定义了一个名为adder的模块,它具有两个输入端口A和B,以及一个输出端口sum。

内部逻辑通过assign语句实现,将输入端口A和B相加,并将结果赋值给输出端口sum。

接下来,让我们了解Verilog中的数据类型和运算符。

Verilog支持多种数据类型,包括位向量(bit vector)、整数(integer)、浮点数(real)等。

其中,位向量是最常用的数据类型。

以下是两个位向量相加的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```在这个例子中,输入端口A和B都是4位的位向量,输出端口sum也是4位的位向量。

通过使用+运算符,我们可以对这两个位向量进行相加操作,并将结果赋值给输出端口sum。

除了基本的数据类型和运算符,Verilog还提供了丰富的条件和循环语句。

条件语句允许您在程序中根据一些条件执行不同的操作。

以下是一个简单的条件语句的例子:```beginif (A == B)equal = 1;elseequal = 0;endendmodule```在这个例子中,我们使用了always块来定义一个连续的行为。

Verilog的词法约定1Verilog是大小写相关的,其中的关键字全部为小写。

2空白符由空格、制表符、和换行符组成。

3单行注释以“//”开始,verilog将忽略此处到行尾的内容。

多行注释以“/*”开始,以“*/”结束。

多行注释不允许嵌套4操作符有三种:单目操作符、双目操作符和三目操作符。

5数字声明Verilog中有两种数字生命:指明位数的数字和不指明位数的数字指明位数的数字表示形式:<size>’<base format><number>Size用来指明数字位宽度,只能用十进制整数表示Base format包括十进制(’d或’D),二进制(’b或’B),八进制(‘o或’O),十六进制(‘h或’H)例如4’b1111 //4位2进制数12’h3ac //12位16进制数不指明位数的数字:如果数字说明中没有指定基数,那么默认表示为十进制数。

如果没有指定位宽,则默认的位宽度与仿真器和使用的计算机有关(最小为32位)。

‘o21 //32位八进制数X值和Z值:不确定值用X表示,高阻用Z值表示。

在八进制数中代表3位,十六进制中代表4位。

12’h12X //这是一个12位16进制数,其中低四位不确定负数:在表示位宽的数字前面增加一个减号来表示它是一个负数。

-6’d3 //一个6位的用二进制补码形式存储的十进制数3,表示负数-6’sd3 //一个6位的带符号算数运算的负数下划线符号和问号:除了第一个字符,下划线“_”可以出现在数字中的任何位置,它的作用只是提高可读性,在编译阶段会被忽略掉问号“?”是z的另一种表示,使用问号的目的在于增强casex和casez语句的可读性。

在这两条语句中,“?”表示不必关心的情况。

12’B1111_0011_1110 // 增强可读性4’b10?? //相当于4’b10zz6字符串是双引号括起来的一个字符队列。

对于字符串的限制是,它必须在一行中书写完,不可书写在多行中,也不能包含回车符。

Verilog HDL(硬件描述语言)是一种用于描述数字电路和硬件设计的语言。

它被广泛用于数字电路设计、FPGA 编程和ASIC 设计等领域。

以下是Verilog HDL的一些基本语法要点:模块声明:Verilog程序通常由一个或多个模块组成。

每个模块的声明以关键字module 开始,后面跟着模块的名称和输入/输出端口的声明。

例如:module MyModule (input wire A,input wire B,output wire Y);// 模块的行为描述endmodule端口声明:端口声明包括输入(input)、输出(output)、双向(inout)端口,以及线(wire)或寄存器(reg)类型的端口。

端口声明通常在模块的参数列表中列出。

线声明:线(wire)用于表示组合逻辑电路中的连接,它们不存储任何状态。

寄存器(reg)用于表示时序逻辑电路中的状态元素,可以存储数据。

例如:wire A, B;reg [7:0] data;组合逻辑:组合逻辑使用assign 语句来描述,它定义了如何从输入信号计算输出信号。

例如:assign Y = A & B; // Y是A和B的逻辑与结果时序逻辑:时序逻辑通常使用always 块来描述。

它表示在时钟信号的边沿或电平触发时执行的操作。

例如:always @(posedge clk) beginif (reset) begindata <= 8'h00;end else begindata <= data + 1;endend条件语句:Verilog使用if、else if 和else 来描述条件分支。

例如:if (condition1) begin// 条件1成立时的操作end else if (condition2) begin// 条件2成立时的操作end else begin// 以上条件都不成立时的操作end模块实例化:你可以在其他模块内部实例化已定义的模块,并连接其输入和输出。

verilog语法Verilog一种用于描述电子电路行为的高级硬件描述语言,其灵活的结构、强大的功能和对模块的建模特性,使其在仿真和硬件实现中得到广泛的应用。

Verilog法通常分为两个组成部分:结构语法和功能语法。

一、结构语法Verilog构语法描述了一个电路的框架,提供一种定义、声明及规定关系的有效方法。

Verilog构语法主要由模块、实例、参数、端口、变量、语句和模式组成。

1.模块Verilog块定义了一个电路系统的单元,是一种抽象的概念,用来把一个电路系统分割成各个模块,彼此之间通过端口相连,其中的每一个模块都可以包含有变量、模式、端口以及子模块等元素。

模块又可以分为模块模板(moduletemplate)、仿真模块(simmodule)和电路模块(circuitmodule)。

2.实例每个模块都能被实例化,实例化是指把一个模块变成一个独立的实体,可以通过连接实例间的端口进行连接,形成一个更大的电路系统。

3.参数参数是一种把多个实例统一起来的有效方式,它是一个确定的值,在实例化时用来替换模块的变量。

4.端口端口是模块和实例的接口,是模块实例的输入和输出的点。

5.变量变量是一种值的容器,可以用来存储和更新模块里的数据,包括数字、逻辑类型和指针等。

6.语句Verilog句是实现逻辑功能的主要组成部分。

它是由一条或多条以分号分隔的语句组成,用来执行某种功能或描述模块的行为。

7.模式模式是 Verilog言建模中最重要的部分,用以定义系统模块的行为,模式可以是数字、逻辑或者状态等,可以描述模块的行为以及改变模块的状态等。

二、功能语法功能语法是 Verilog另一个重要组成部分,其主要指令有descriptionaction 两类。

description令用于定义模块的功能,也可以用来实现电路行为。

action令可以控制语句执行顺序以及定义多个模块之间的关系,可以将模块与外部连接及各个模块之间的交互实现。