verilog语法教程

- 格式:pdf

- 大小:2.33 MB

- 文档页数:63

verilog 基本语法Verilog基本语法Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

它具有强大的建模能力,能够描述复杂的数字系统,并用于逻辑设计和硬件验证。

本文将介绍Verilog的基本语法,以帮助读者对这种语言有一个基本的了解。

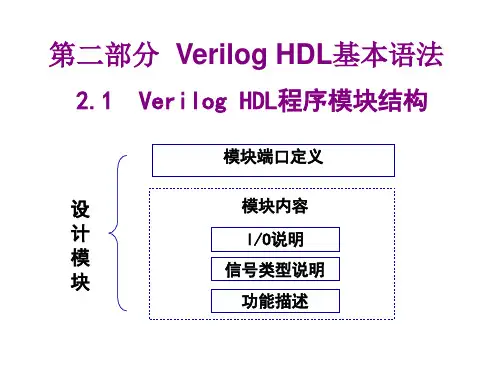

1. 模块声明在Verilog中,所有的设计都是通过模块来实现的。

模块是Verilog 的基本组织单位,类似于其他编程语言中的函数或类。

模块声明由关键字module开头,后面跟着模块的名称和输入输出端口的定义。

例如:module my_module(input a, b, output c);// 模块的主体endmodule2. 端口声明在模块声明中,使用关键字input和output来声明输入和输出端口。

输入端口用于接收信号,输出端口用于输出信号。

端口可以是单个的信号,也可以是信号的数组。

例如:input a, b; // 单个输入端口output c; // 单个输出端口input [7:0] d; // 输入信号的数组3. 信号声明在Verilog中,使用关键字wire、reg、integer等来声明信号。

wire用于声明连续的信号,reg用于声明时序的信号,integer用于声明整数变量。

例如:wire a, b; // 连续信号reg [7:0] c; // 时序信号,有8位integer d; // 整数变量4. 时钟和复位在数字电路中,时钟和复位信号是非常重要的。

在Verilog中,可以使用关键字input来声明时钟和复位信号,并在模块的输入端口中定义。

例如:input clk; // 时钟信号input rst; // 复位信号5. 运算符Verilog支持各种运算符,包括算术运算符、逻辑运算符、位运算符等。

算术运算符用于执行加减乘除等操作,逻辑运算符用于执行与或非等逻辑操作,位运算符用于执行位操作。

例如:a =b + c; // 加法运算d = ~(a & b); // 与运算和非运算6. 控制结构在Verilog中,可以使用if语句、case语句等控制结构来实现条件判断和多路选择。

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

目录•Verilog概述•Verilog基础语法•组合逻辑电路设计•时序逻辑电路设计•数字系统设计方法学•华为Verilog编程规范与技巧Verilog概述1 2 3Verilog语言诞生,最初用于模拟电子系统的行为。

1980年代初期Verilog逐渐发展成为硬件描述语言(HDL),用于描述数字电路和系统的结构和行为。

1980年代中期Verilog不断完善和发展,成为电子设计自动化(EDA)领域的重要标准之一,广泛应用于集成电路设计、FPGA开发等领域。

1990年代至今Verilog历史与发展集成电路设计Verilog可用于描述数字集成电路的逻辑功能、时序关系和电路结构,是IC设计领域的重要工具。

FPGA开发Verilog可用于FPGA的逻辑设计和编程,实现复杂的数字系统和算法。

ASIC设计Verilog可用于ASIC设计的各个阶段,包括逻辑设计、综合、布局布线等。

系统级建模与仿真Verilog可用于构建系统级模型,进行系统仿真和性能分析。

Verilog应用领域01Verilog 是一种硬件描述语言(HDL ),用于描述数字电路和系统的结构和行为。

02与其他硬件描述语言(如VHDL )相比,Verilog具有更接近C 语言的语法风格,易于学习和使用。

Verilog 支持多种抽象层次的描述,包括行为级、寄存器传输级(RTL )、门级和开关级,方便设计师在不同设计阶段使用。

Verilog 与硬件描述语言关系02Verilog基础语法标识符与关键字标识符用于标识变量、模块、函数等程序实体的名称,由字母、数字和下划线组成,首字符必须是字母或下划线。

关键字Verilog语言中的保留字,用于定义语言结构和控制语句,如`module`、`input`、`output`、`if`、`else`等。

数据类型与运算符数据类型包括整型(`integer`)、实型(`real`)、时间型(`time`)以及用户自定义类型等。

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

硬件描述语言和数字系统设计第3章 VerilogVerilogVerilog 基本语法主讲教师:郑朝霞华中科技大学电子系郑朝霞华中科技大学电子系郑朝霞23.1 3.1 Verilog Verilog Verilog HDLHDL 基本模块说明3.2 3.2 Verilog Verilog Verilog HDLHDL 中的词汇约定3.3 3.3 Verilog Verilog Verilog HDLHDL 数据类型3.4 3.4 Verilog Verilog Verilog HDLHDL 运算符主要内容主要内容::华中科技大学电子系郑朝霞33.1 Verilog Verilog HDLHDL 基本模块说明�module 能够表示:�物理块,如IC 或ASIC 单元�逻辑块,如一个CPU 设计的ALU 部分�整个系统�每一个模块的描述从关键词module 开始,有一个名称(如SN74LS74,DFF ,ALU 等等),由关键词endmodule 结束。

module 是层次化设计的基本构件逻辑描述放在module 内部Verilog 模块(module)结构基本要素Verilog知识点:3.1.1 端口信息输入//输出说明3.1.23.1.2 输入3.1.3 逻辑功能描述华中科技大学电子系郑朝霞43.1.1端口信息2,端口等价于硬件的引脚(pin)1,端口在模块名字后的括号中列出3,端口可以说明为input,output及inout �模块通过端口与外部通信华中科技大学电子系郑朝霞5华中科技大学电子系郑朝霞6Verilog 模块的结构由在module 和endmodule 关键词之间的四个主要部分组成:- 1- 1.. 端口信息: module combination(a, b, c, d ); - 2- 2- 2. . 输入/输出说明 : input a, b, c ;input a, b, c ; output d ;output d ; -//-//-//输入/输出端口信号类型声明,缺省为wire 型 : - 3- 3- 3. . 内部信号: wire x; wire x; - 4- 4- 4. . 功能定义: assign d = a | x ; assign d = a | x ; assign x = ( b & ~c ); endmodule3.1.2 端口说明华中科技大学电子系郑朝霞73.1.3 逻辑功能描述module mux2to1 (out, a, b, mux2to1 (out, a, b, sel sel sel);); input a, b, input a, b, sel sel sel;; output out;wire out;assign out=( assign out=(sel)?b:a sel)?b:a sel)?b:a;;endmodule两路选择器的RTL 级描述1:华中科技大学电子系郑朝霞8两路选择器的RTL 级描述2:module mux2to1 (out, a, b, mux2to1 (out, a, b, sel sel sel);); input a, b, input a, b, sel sel sel;; output out;reg reg reg out;out;always @( always @( sel sel sel or a or b)or a or b) if (! if (! sel sel sel) out = a;) out = a; else out = b;endmodule实例化(module instances):�1. 端口信息�2. 输入/输出说明�3. 逻辑功能描述(实例化实现功能描述)华中科技大学电子系郑朝霞9华中科技大学电子系郑朝霞10module mux2to1 (out, a, b, mux2to1 (out, a, b, sl sl sl);); input a, b, input a, b, sl sl sl;; output out;not u1 ( u1 (nsl nsl nsl, , , sl sl sl );); and u2 ( u2 (sela sela sela, a, , a, , a, nsl nsl nsl);); and u3 ( u3 (selb selb selb, b, , b, , b, sl sl sl);); or u4 (out, u4 (out, sela sela sela, , , selb selb selb););endmodule两路选择器的门级描述-实例化:华中科技大学电子系郑朝霞11�请在下面的空格中填入适当的符号使其成为右图的Verilog 模块 : module block1(a, b, module block1(a, b, ——, , ——, , —— ); input input ——, , ——, , ——; —————— d, d, d, —— ; assign d = a | ( b & ~c) ; assign e = ( b & ~c ); _______练习:编写Verilog Verilog HDLHDL 模块a b cd e华中科技大学电子系郑朝霞12module moduleblock1(a, b, c , d , e ); input input a , b , c ;o utput d, e ; assign d = a | ( b & ~c) ;assign d = a | ( b & ~c) ; assign e = ( b & ~c );assign e = ( b & ~c ); ee ndmodule 练习答案:编写Verilog Verilog HDL HDL 模块a b cde华中科技大学电子系郑朝霞133.2 3.2 Verilog Verilog Verilog HDLHDL 中的词汇约定知识点:�3.2.1 术语及定义�3.2.2 空白符和注释�3.2.3 3.2.3 VerilogVerilog 采用的四值逻辑系统�3.2.4 整数常量和实数常量�3.2.5 字符串�3.2.6 标识符�3.2.7 系统任务及函数�3.2.8 编译指导 �3.2.9 文本包含�3.2.10 文本替换3.2.1 术语及定义1.空白符:空格、tabs及换行2.标志符(Identifier):Verilog中对象(如模块或信号)的名字3.LSB:最低有效位(Lease significant bit)4.MSB:最高有效位(Most significant bit)华中科技大学电子系郑朝霞14华中科技大学电子系郑朝霞153.2.2 空白符和注释module MUX2_1 (out, a, b, module MUX2_1 (out, a, b, sel sel sel);); // Port declarationsoutput out;input input sel sel sel; // control input; // control input input b, a; / input b, a; /** data inputs data inputs **/ wire wire sel sel sel_, a1, b1;_, a1, b1; / /**The The netlist netlist netlist logic selects input logic selects input logic selects input ””a ” when sel sel sel = 0 and it selects = 0 and it selects = 0 and it selects ””b ” when when sel sel sel = 1. = 1. = 1. **/ not not1 ( not1 (sel sel sel_, _, _, sel sel sel);); and and1 (a1, a, and1 (a1, a, sel sel sel_)_); and and2 (b1, b, and2 (b1, b, sel sel sel); ); or or1 (out, a1, b1);endmodule格式自由使用空白符提高可读性及代码组织。

verilog module语法Verilog Module语法Verilog是一种硬件描述语言,用于设计和建模数字电路。

在Verilog中,模块(Module)是描述电路功能的基本单元。

本文将详细介绍Verilog的模块语法。

1. 模块声明在Verilog中,模块的声明以`module`关键字开头,后面跟着模块的名称,并用括号括起来,括号中是模块的输入和输出端口。

例如:```verilogmodule MyModule(input A, input B, output C);```上述代码定义了一个名为MyModule的模块,有两个输入端口A和B,一个输出端口C。

2. 端口声明在模块的括号中,可以用逗号分隔的方式声明多个端口。

每个端口可以是输入端口(input)、输出端口(output)或双向端口(inout)。

例如:```verilogmodule MyModule(input A, input [7:0] B, output [7:0] C, inout D);```上述代码中,A是一个输入端口,B是一个8位输入端口,C是一个8位输出端口,D是一个双向端口。

3. 内部信号声明在模块中,可以声明内部信号(wire或reg),用于在模块内部进行信号传输或存储。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;reg [7:0] E;// 省略其他代码endmodule```上述代码中,D是一个wire类型的内部信号,E是一个8位reg类型的内部信号。

4. 逻辑表达式在模块中,可以使用逻辑运算符和条件语句来实现电路的逻辑功能。

例如:```verilogmodule MyModule(input A, input B, output C);wire D;assign D = A & B;always @(posedge D)C <= ~C;endmodule```上述代码中,使用`&`逻辑与运算符计算A和B的与运算结果,并将结果赋值给D。

Verilog语言是一种硬件描述语言(HDL),用于描述和设计数字电路。

它广泛应用于数字系统的建模、验证和综合,是数字电路设计领域中的重要工具之一。

在Verilog中,模块是最基本的组织单位,模块中包含了电路的功能和行为描述。

本文将介绍Verilog语言的基本语法和模块写法,以帮助读者更好地理解和应用Verilog语言。

一、Verilog基本语法1. 注释在Verilog中,使用双斜杠(//)进行单行注释,使用/* */进行多行注释。

注释可以提高代码的可读性,便于他人理解和维护。

2. 变量声明Verilog中的变量可以分为寄存器变量(reg)和线网(wire)两种类型。

寄存器变量用于存储状态信息,线网用于连接各个逻辑门的输入和输出。

3. 逻辑运算符和位运算符Verilog中包括逻辑运算符(与、或、非等)和位运算符(与、或、异或等),用于对信号进行逻辑和位级操作。

4. 控制语句Verilog支持if-else语句、case语句等控制语句,用于根据不同条件执行不同的操作。

5. 模拟时钟在Verilog中,时钟是电路中的重要部分,通常使用时钟信号来同步各个元件的动作。

时钟可以通过周期性方波信号来模拟,使用$period 函数可以定义时钟的周期。

6. 仿真指令Verilog提供了多种仿真指令,用于初始化信号、设置仿真时间、输出波形图等操作,有助于仿真和调试电路。

二、模块写法1. 模块定义在Verilog中,一个模块包含了一组功能相关的硬件描述,可以看作是一个小型电路的抽象。

模块通过module关键字进行定义,其中包括模块名、输入输出端口声明等信息。

```verilogmodule adder(input wire [3:0] a,input wire [3:0] b,output reg [4:0] c);// 模块内部逻辑描述endmodule```2. 端口声明模块的端口包括输入端口(input)和输出端口(output),可以通过wire和reg进行声明。

Verilog-A语法实用指南Verilog-A语法是描述模拟电路行为的一种编程语言。

它可以用于描述电路的行为和功能,是数字电路设计中常用的一种语言。

本文将从Verilog-A语法的基本特点、常用语法以及示例应用等方面展开介绍,希望可以为初学者提供一些指导和帮助。

一、Verilog-A语法的基本特点1. 语法简洁明了:Verilog-A语法采用了类似C语言的结构,采用了分号作为语句结束符,使得代码具有良好的可读性。

2. 强大的模块化功能:Verilog-A语法支持模块化的设计,可以将电路设计分为多个模块,每个模块完成不同的功能。

3. 丰富的数据类型:Verilog-A语法支持多种数据类型,包括整型、实型、布尔型等,能够适应不同的应用场景。

4. 可扩展性强:Verilog-A语法可以方便地扩展新的功能和特性,使得它在大型项目中也能够得到应用。

二、Verilog-A语法的常用语法1. 模块定义:使用module关键字定义一个模块,模块内包含输入端口、输出端口以及内部逻辑。

2. 参数定义:使用parameter关键字定义参数,可以在模块中使用这些参数。

3. 时序控制:使用initial关键字定义初始条件,使用always关键字定义条件触发的操作。

4. 信号赋值:使用assign关键字完成信号之间的赋值操作。

5. 行为描述:使用initial和always关键字描述电路的行为。

6. 分支结构:使用if...else...语句完成条件判断。

7. 循环结构:使用for和while等关键字完成循环操作。

三、Verilog-A语法的示例应用1. 模拟电路设计:Verilog-A语法可以用于模拟电路的设计和验证,包括数字电路和模拟电路。

2. 信号处理:Verilog-A语法可以用于实现信号的采集、处理和输出。

3. 控制系统:Verilog-A语法可以用于描述控制系统的行为和功能,包括PID控制、状态空间控制等。

4. 通信系统:Verilog-A语法可以用于描述通信系统的行为和功能,包括调制解调、编解码等。

Verilog语法简易教程Verilog是硬件描述语言(HDL)之一,主要用于硬件设计和仿真。

它于1984年由一家名为Gateway Design Automation的公司开发,并于1985年推出。

Verilog以其简单易学的语法和强大的功能而闻名于世。

本简易教程将向您介绍Verilog的基本语法和常用结构。

它包括模块化设计,数据类型,运算符,条件语句,循环语句和时序建模等内容。

首先,让我们先来了解Verilog中的模块化设计。

在Verilog中,设计是通过定义和连接模块来完成的。

每个模块由输入输出端口和内部逻辑组成。

以下是一个简单的Verilog模块的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```上述代码定义了一个名为adder的模块,它具有两个输入端口A和B,以及一个输出端口sum。

内部逻辑通过assign语句实现,将输入端口A和B相加,并将结果赋值给输出端口sum。

接下来,让我们了解Verilog中的数据类型和运算符。

Verilog支持多种数据类型,包括位向量(bit vector)、整数(integer)、浮点数(real)等。

其中,位向量是最常用的数据类型。

以下是两个位向量相加的例子:```module adder(input [3:0] A, B, output [3:0] sum);assign sum = A + B;endmodule```在这个例子中,输入端口A和B都是4位的位向量,输出端口sum也是4位的位向量。

通过使用+运算符,我们可以对这两个位向量进行相加操作,并将结果赋值给输出端口sum。

除了基本的数据类型和运算符,Verilog还提供了丰富的条件和循环语句。

条件语句允许您在程序中根据一些条件执行不同的操作。

以下是一个简单的条件语句的例子:```beginif (A == B)equal = 1;elseequal = 0;endendmodule```在这个例子中,我们使用了always块来定义一个连续的行为。