Verilog基本语法

- 格式:pdf

- 大小:704.41 KB

- 文档页数:71

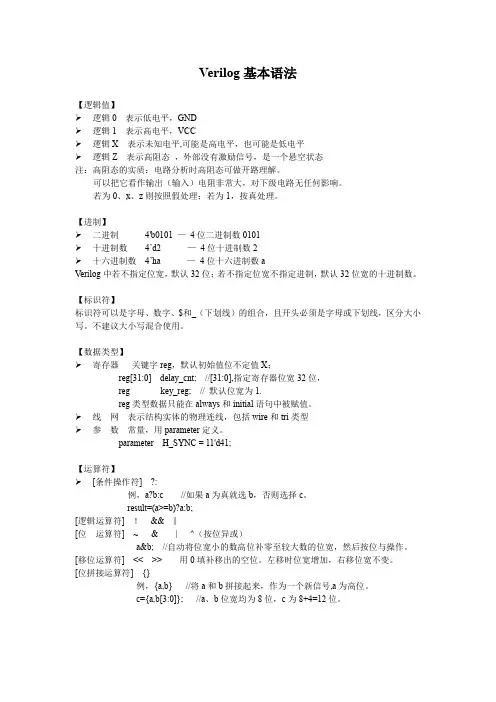

Verilog基本语法【逻辑值】➢逻辑0 表示低电平,GND➢逻辑1 表示高电平,VCC➢逻辑X 表示未知电平,可能是高电平,也可能是低电平➢逻辑Z 表示高阻态,外部没有激励信号,是一个悬空状态注:高阻态的实质:电路分析时高阻态可做开路理解。

可以把它看作输出(输入)电阻非常大,对下级电路无任何影响。

若为0、x、z则按照假处理;若为1,按真处理。

【进制】➢二进制4'b0101 —4位二进制数0101➢十进制数4’d2 —4位十进制数2➢十六进制数4’ha —4位十六进制数aVerilog中若不指定位宽,默认32位;若不指定位宽不指定进制,默认32位宽的十进制数。

【标识符】标识符可以是字母、数字、$和_(下划线)的组合,且开头必须是字母或下划线,区分大小写。

不建议大小写混合使用。

【数据类型】➢寄存器关键字reg,默认初始值位不定值X;reg[31:0] delay_cnt; //[31:0],指定寄存器位宽32位,reg key_reg; // 默认位宽为1.reg类型数据只能在always和initial语句中被赋值。

➢线网表示结构实体的物理连线,包括wire和tri类型➢参数常量,用parameter定义。

parameter H_SYNC = 11'd41;【运算符】➢[条件操作符] ?:例,a?b:c //如果a为真就选b,否则选择c。

result=(a>=b)?a:b;[逻辑运算符] !&& ||[位运算符] ~ & | ^(按位异或)a&b; //自动将位宽小的数高位补零至较大数的位宽,然后按位与操作。

[移位运算符] << >> 用0填补移出的空位。

左移时位宽增加,右移位宽不变。

[位拼接运算符] {}例,{a,b} //将a和b拼接起来,作为一个新信号,a为高位。

c={a,b[3:0]}; //a、b位宽均为8位,c为8+4=12位。

verilog 基本语法Verilog基本语法Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

它具有强大的建模能力,能够描述复杂的数字系统,并用于逻辑设计和硬件验证。

本文将介绍Verilog的基本语法,以帮助读者对这种语言有一个基本的了解。

1. 模块声明在Verilog中,所有的设计都是通过模块来实现的。

模块是Verilog 的基本组织单位,类似于其他编程语言中的函数或类。

模块声明由关键字module开头,后面跟着模块的名称和输入输出端口的定义。

例如:module my_module(input a, b, output c);// 模块的主体endmodule2. 端口声明在模块声明中,使用关键字input和output来声明输入和输出端口。

输入端口用于接收信号,输出端口用于输出信号。

端口可以是单个的信号,也可以是信号的数组。

例如:input a, b; // 单个输入端口output c; // 单个输出端口input [7:0] d; // 输入信号的数组3. 信号声明在Verilog中,使用关键字wire、reg、integer等来声明信号。

wire用于声明连续的信号,reg用于声明时序的信号,integer用于声明整数变量。

例如:wire a, b; // 连续信号reg [7:0] c; // 时序信号,有8位integer d; // 整数变量4. 时钟和复位在数字电路中,时钟和复位信号是非常重要的。

在Verilog中,可以使用关键字input来声明时钟和复位信号,并在模块的输入端口中定义。

例如:input clk; // 时钟信号input rst; // 复位信号5. 运算符Verilog支持各种运算符,包括算术运算符、逻辑运算符、位运算符等。

算术运算符用于执行加减乘除等操作,逻辑运算符用于执行与或非等逻辑操作,位运算符用于执行位操作。

例如:a =b + c; // 加法运算d = ~(a & b); // 与运算和非运算6. 控制结构在Verilog中,可以使用if语句、case语句等控制结构来实现条件判断和多路选择。

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

veriloga语法electrical摘要:一、Veriloga语法简介1.Veriloga的起源与发展2.Veriloga的主要特点二、Veriloga的基本语法1.模块定义2.信号声明3.逻辑表达式4.赋值语句5.条件语句6.循环语句三、Veriloga的高级语法1.参数传递与使用2.函数定义与调用3.任务定义与调用4.结构体与实例化5.生成块与循环块四、Veriloga在电路设计中的应用1.描述数字电路2.描述模拟电路3.混合信号电路设计4.验证与仿真五、Veriloga与其他语言的比较1.Veriloga与Verilog的比较2.Veriloga与VHDL的比较3.Veriloga在实际项目中的应用优势正文:Veriloga是一种基于Verilog的硬件描述语言,它继承了Verilog的优点,并在此基础上进行了改进与拓展。

Veriloga的语法结构清晰,易于学习,被广泛应用于电路设计与验证领域。

一、Veriloga语法简介Veriloga起源于2001年,由Cadence公司推出,以满足日益复杂的电路设计需求。

它具有语法简洁、可读性强、设计效率高等特点,逐渐成为硬件描述语言领域的一股新兴力量。

二、Veriloga的基本语法1.模块定义在Veriloga中,一个设计可以被划分为多个模块。

模块定义的基本格式如下:```module module_name (input wire clk,input wire rst,output reg [7:0] data_out);```其中,`module_name`为模块名称,`clk`和`rst`为时钟和复位信号,`data_out`为输出信号。

1.信号声明信号声明用于定义模块内的信号,包括输入、输出和寄存器。

信号声明的基本格式如下:```input wire clk;input wire rst;output reg [7:0] data_out;```1.逻辑表达式Veriloga支持各种逻辑运算,如与(`&`)、或(`|`)、非(`~`)等。

verilog知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统,它广泛应用于数字系统设计和仿真领域。

本文将总结一些Verilog 的重要知识点,以帮助读者更好地理解和应用Verilog。

一、Verilog的基本语法Verilog的基本语法包括模块声明、端口声明、信号声明、数据类型、运算符等。

Verilog中的模块是设计的基本单元,模块声明包括模块名和端口声明。

端口可以是输入、输出或双向的。

信号声明用于定义内部信号,可以是寄存器或线网类型。

Verilog支持多种数据类型,包括整数、浮点数、向量、数组等。

Verilog还提供了丰富的运算符,包括算术运算符、逻辑运算符、位运算符等。

二、组合逻辑电路描述Verilog可以用来描述各种组合逻辑电路,如与门、或门、非门等。

通过使用逻辑运算符和条件语句,可以很方便地描述组合逻辑电路的功能。

Verilog还提供了多种语法结构,如if语句、case语句等,用于描述复杂的逻辑功能。

三、时序逻辑电路描述时序逻辑电路是一种带有状态的电路,Verilog可以用来描述各种时序逻辑电路,如触发器、计数器、状态机等。

通过使用时钟信号和触发器,可以实现电路的时序行为。

Verilog提供了多种触发器类型,如D触发器、JK触发器、T触发器等,可以根据实际需求选择合适的触发器类型。

四、模块实例化和层次化设计Verilog支持模块的实例化和层次化设计,可以将一个模块实例化为另一个模块的一部分。

通过模块实例化,可以方便地实现模块的复用和层次化设计。

层次化设计可以使整个系统更加清晰和模块化,方便调试和维护。

五、仿真和验证Verilog可以用于对设计进行仿真和验证,以确保设计的正确性。

Verilog提供了仿真器,可以对设计进行时序仿真和波形查看。

通过仿真,可以验证设计的功能和时序行为是否符合要求。

Verilog 还支持测试向量的生成和自动验证,可以自动生成测试向量并进行自动验证。

verilog基本语法

1. 模块:verilog模块用于描述感兴趣的功能系统以及设备行为,从而给出输入和输出之间的关系。

2. 变量:verilog中的变量可以定义为硬件控制的行为或信号路径。

3. 宏定义:verilog使用宏`define`来定义新的字符或文本,可用于

提高程序可读性和管理性。

4. 注释:verilog支持两种注释形式,即行注释和块注释,行注释以

`//`开头,块注释以`/*`开头,以 `*/`结尾。

5. 关键字:verilog使用了一系列关键字来指定硬件控制行为,输入、输出、时序延迟和引用等。

6. 命令:verilog提供了一系列命令来描述功能,包括`initial`,

`always`,`@`和`begin`等等。

7. 模型:verilog中的模型用于定义和控制硬件的输入和输出行为,

这些模型可以被定义为多个状态和条件的序列。

verilog语法基础Verilog语法基础Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

它是一种基于事件的语言,能够描述电路的结构和行为。

本文将介绍Verilog语法的基础知识,包括模块、端口、信号、赋值和运算等。

一、模块(Module)在Verilog中,模块是描述电路的基本单元。

一个模块可以包含多个端口和信号,并定义了电路的功能和结构。

模块的定义使用关键字module,后跟模块的名称和端口列表。

二、端口(Port)Verilog中的端口是模块与外部环境进行通信的接口。

端口可以是输入端口、输出端口或双向端口。

输入端口用于接收外部信号,输出端口用于输出信号至外部,而双向端口则可同时进行输入和输出。

端口的定义使用关键字input、output或inout,后跟端口的类型和名称。

三、信号(Signal)Verilog中的信号用于在模块内部传递和存储数据。

信号可以是寄存器类型或线网类型。

寄存器类型信号用于存储数据,线网类型信号用于传递数据。

信号的定义使用关键字reg或wire,后跟信号的宽度和名称。

四、赋值(Assignment)在Verilog中,使用赋值语句将值分配给信号或变量。

赋值语句可以是阻塞式赋值或非阻塞式赋值。

阻塞式赋值使用等号(=)将右侧的值赋给左侧的信号,而非阻塞式赋值使用双等号(<=)进行赋值。

赋值语句的左侧可以是信号或变量,右侧可以是常数、信号、变量或表达式。

五、运算(Operator)Verilog中支持多种运算,包括算术运算、逻辑运算、位运算和比较运算等。

算术运算包括加法、减法、乘法和除法等;逻辑运算包括与、或、非和异或等;位运算包括位与、位或、位非和位异或等;比较运算包括等于、不等于、大于、小于等。

运算符可以用于常数、信号、变量或表达式之间的运算。

六、条件语句(Conditional Statement)Verilog中的条件语句用于根据条件选择执行不同的操作。

verilog核心语法Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统的行为和结构。

下面我将从多个角度来介绍Verilog的核心语法。

1. 模块声明:Verilog中,模块是描述数字电路的基本单元。

模块声明的语法如下:module 模块名(输入端口声明, 输出端口声明, 内部信号声明);// 模块内部逻辑描述。

endmodule.其中,输入端口声明和输出端口声明指定了模块的接口,内部信号声明定义了模块内部使用的信号。

2. 数据类型:Verilog支持多种数据类型,包括位(bit)、向量(vector)、整数(integer)、实数(real)等。

可以使用`reg`关键字声明寄存器类型,使用`wire`关键字声明线网类型。

例如:reg [7:0] a; // 8位寄存器。

wire [3:0] b; // 4位线网。

integer c; // 整数类型。

real d; // 实数类型。

3. 运算符:Verilog支持常见的运算符,包括算术运算符(+、-、、/、%)、逻辑运算符(&&、||、!)、位运算符(&、|、^、~)等。

此外,还有条件运算符(?:)和赋值运算符(=、<=、>=、+=、-=等)。

4. 语句:Verilog中常用的语句有:过程语句(always),用于描述组合逻辑和时序逻辑。

常见的过程语句有`always @()`和`always @(posedge clk)`,分别表示组合逻辑和时钟上升沿触发的时序逻辑。

条件语句(if-else):用于根据条件执行不同的语句块。

语法如下:if (条件)。

// 条件为真时执行的语句块。

else.// 条件为假时执行的语句块。

循环语句(for、while):用于重复执行一段代码块。

语法如下:for (初始化; 条件; 更新)。

// 循环体。

while (条件)。

// 循环体。

分支语句(case):根据表达式的值选择执行不同的语句块。

verilog语法基本知识Verilog语法基本知识Verilog是一种硬件描述语言,用于设计数字电路和系统。

它是一种结构化的编程语言,具有高度的抽象性和可重用性。

本文将介绍Verilog 的基本语法知识。

1.模块定义在Verilog中,一个模块是一个独立的实体,可以包含多个输入和输出端口以及内部逻辑。

模块定义的基本形式如下:module module_name(input port_list, output port_list);//内部逻辑endmodule其中,module_name为模块名称,input port_list为输入端口列表,output port_list为输出端口列表。

2.端口定义在模块定义中,可以定义多个输入和输出端口。

每个端口都有一个名称和数据类型。

例如:input clk; //定义一个时钟输入端口output reg [7:0] data_out; //定义一个8位输出端口3.数据类型Verilog支持多种数据类型,包括整数、浮点数、布尔值、向量等。

整数类型可以是有符号或无符号的,并且可以指定位宽。

例如:reg signed [7:0] num1; //有符号8位整数类型reg unsigned [15:0] num2; //无符号16位整数类型浮点数类型包括实数和双精度实数。

例如:real num3; //实数类型realtime num4; //双精度实数类型布尔值类型包括true和false。

例如:wire flag; //布尔值类型向量类型可以表示多位数据,例如:reg [7:0] data_in; //8位向量类型4.运算符Verilog支持多种运算符,包括算术运算符、比较运算符、逻辑运算符等。

算术运算符包括加、减、乘、除等。

例如:a =b + c; //加法运算b = d * e; //乘法运算比较运算符包括等于、不等于、大于、小于等。

例如:if(a == b) begin //判断a是否等于b//执行代码end逻辑运算符包括与、或、非等。

verilog语法Verilog一种用于描述电子电路行为的高级硬件描述语言,其灵活的结构、强大的功能和对模块的建模特性,使其在仿真和硬件实现中得到广泛的应用。

Verilog法通常分为两个组成部分:结构语法和功能语法。

一、结构语法Verilog构语法描述了一个电路的框架,提供一种定义、声明及规定关系的有效方法。

Verilog构语法主要由模块、实例、参数、端口、变量、语句和模式组成。

1.模块Verilog块定义了一个电路系统的单元,是一种抽象的概念,用来把一个电路系统分割成各个模块,彼此之间通过端口相连,其中的每一个模块都可以包含有变量、模式、端口以及子模块等元素。

模块又可以分为模块模板(moduletemplate)、仿真模块(simmodule)和电路模块(circuitmodule)。

2.实例每个模块都能被实例化,实例化是指把一个模块变成一个独立的实体,可以通过连接实例间的端口进行连接,形成一个更大的电路系统。

3.参数参数是一种把多个实例统一起来的有效方式,它是一个确定的值,在实例化时用来替换模块的变量。

4.端口端口是模块和实例的接口,是模块实例的输入和输出的点。

5.变量变量是一种值的容器,可以用来存储和更新模块里的数据,包括数字、逻辑类型和指针等。

6.语句Verilog句是实现逻辑功能的主要组成部分。

它是由一条或多条以分号分隔的语句组成,用来执行某种功能或描述模块的行为。

7.模式模式是 Verilog言建模中最重要的部分,用以定义系统模块的行为,模式可以是数字、逻辑或者状态等,可以描述模块的行为以及改变模块的状态等。

二、功能语法功能语法是 Verilog另一个重要组成部分,其主要指令有descriptionaction 两类。

description令用于定义模块的功能,也可以用来实现电路行为。

action令可以控制语句执行顺序以及定义多个模块之间的关系,可以将模块与外部连接及各个模块之间的交互实现。

veriloghdl语法Verilog HDL(硬件描述语言)是一种硬件描述和设计语言,用于描述和设计数字电路和系统。

以下是Verilog HDL的基本语法:1. 模块声明:module module_name (input declaration, output declaration, inout declaration);// 逻辑和/或数据声明// 逻辑和/或数据操作endmodule2. 输入和输出声明:input [width-1:0] input_name;output [width-1:0] output_name;3. 内部信号声明:reg [width-1:0] signal_name;wire [width-1:0] signal_name;4. 运算符:- 逻辑运算符: &&(与)、 ||(或)、 !(非)- 比较运算符: ==(等于)、 !=(不等于)、 <(小于)、 >(大于)- 算术运算符: +(加)、 -(减)、 *(乘)、 /(除)5. 过程块:always @(sensitivity_list)// 过程块中的语句6. 过程块敏感列表:- posedge clk:时钟的上升沿- negedge clk:时钟的下降沿- expression:表达式更新时7.条件语句:if (condition)// 如果条件为真执行的语句else if (condition)// 如果第一个条件不为真,检查第二个条件是否为真else// 如果以上条件均不为真执行的语句8. 选择语句:case (expression)value1: // 如果expression等于value1执行的语句value2: // 如果expression等于value2执行的语句default: // 如果expression不等于任何值执行的语句endcase9. 迭代语句:for (initialization; condition; increment)// 循环体内的语句以上是Verilog HDL的一些基本语法,可以用于描述和设计数字电路和系统。

verilog门电路基本语法Verilog是一种硬件描述语言,用于描述数字电路系统。

它可以用于门电路设计,数字系统设计和集成电路设计等。

Verilog门电路基本语法是初学者必须掌握的知识。

下面将详细讨论Verilog门电路基本语法。

1. 模块定义Verilog中的模块定义是一个模块层次结构的起点。

模块内定义了模块的输入,输出和内部结构。

模块定义的基本语法如下:module module_name(input input_list, output output_list);声明模块的输入和输出,例如:module and_gate(input a, input b, output y);定义了一个and门电路,输入有两个信号a和b,输出为信号y。

2. 线声明在Verilog中,需要声明输入输出信号之间的线。

声明线的关键字是wire。

线的声明基本语法如下:wire signal_name;例如,在and门电路中,需要连接a和b输入信号,连接y输出信号,因此需要声明这三个信号:wire a;wire b;wire y;3. 逻辑语句Verilog中的逻辑语句用于实现门电路逻辑。

逻辑语句中的关键字包括and,or,not和nand等。

基本语法如下:and (output, input1, input2);or (output, input1, input2);not (output, input);nand (output, input1, input2);例如,and (y, a, b)表示将输入信号a和b与and门电路的逻辑电路进行运算,输出结果为y。

4. always块always块是Verilog中一个很关键的语句块,用于模拟门电路的时序行为。

always语句块基本语法如下:always @(posedge clk)begin// code blockend例如,always @(posedge clock)表示在时钟上升沿时执行代码块。