LEdit绘制版图

- 格式:ppt

- 大小:4.79 MB

- 文档页数:200

4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

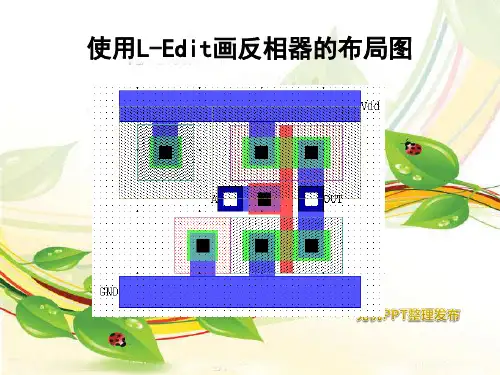

LOGO第2单元绘制版图主讲:赵琳娜LOGO2.4 绘制版图绘制版图CH2LOGO 绘制版图根据手中的0.25um 设计规则,画出反相器中NMOS 管的版图!(Tanner)NMOS:1um/.25um PMOS:2um /.25umLOGO绘制版图画版图时,要严格按照design rule 来画! 软件:tanner14.1 L-Edit软件使用说明详见《集成电路版图设计入门》 好。

Come on !LOGO Layer零距离接触Tanner L-Edit !LOGO零距离接触Tanner L-Edit !LOGO 零距离接触Tanner L-Edit !LOGO零距离接触Tanner L-Edit !LOGO 零距离接触Tanner L-Edit !LOGO绘制版图LOGO LVSDRC 验证通过并不代表Layout 就完全正确了,极端的例子是Layout 中即使什么都没画,DRC 也不会报错,所以我们还需将Layout 和Schematic 作对比,看看是不是该画的器件都画上了,该连的线也都连对了,这样的检查叫LVS(Layout Vs. Schematic) LVS 验证需要的三个文件:GDS2、网表文件(Netlist File )和LVS 命令文件LOGO绘制版图——DRC 检查LOGO 绘制版图——DRC 检查LOGO绘制版图LOGO DRC 检查LOGODRC 检查LOGO DRC 检查LOGO画Schematic ,提取网表文件1)网表文件(Netlist File )1.LOGO 画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件C:\Users\bm\Documents\Tanner EDA\Tanner Tools v15.0\Designs\RingVCO\RingVCO.tannerLOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件iLOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件LOGO导出的网表文件LOGO GDS2LOGOGDS2LOGO GDS2LOGOGDS2LOGO LVS LOGOLVSLOGO LVS LOGOLVSLOGO LVSLOGOLVSLOGO LVS LOGOLVSLOGO 把网表文件里面的nmos W 改为2umLOGO输出文件为inv.out打开inv.out 文件LOGO LVS 验证结果LOGOLVS 验证结果LOGOLVS如果LVS 没有通过,这时需要查看LVS 报告——*.out 。

LOGO第2单元绘制版图主讲:赵琳娜LOGO2.4 绘制版图绘制版图CH2LOGO 绘制版图根据手中的0.25um 设计规则,画出反相器中NMOS 管的版图!(Tanner)NMOS:1um/.25um PMOS:2um /.25umLOGO绘制版图画版图时,要严格按照design rule 来画! 软件:tanner14.1 L-Edit软件使用说明详见《集成电路版图设计入门》 好。

Come on !LOGO Layer零距离接触Tanner L-Edit !LOGO零距离接触Tanner L-Edit !LOGO 零距离接触Tanner L-Edit !LOGO零距离接触Tanner L-Edit !LOGO 零距离接触Tanner L-Edit !LOGO绘制版图LOGO LVSDRC 验证通过并不代表Layout 就完全正确了,极端的例子是Layout 中即使什么都没画,DRC 也不会报错,所以我们还需将Layout 和Schematic 作对比,看看是不是该画的器件都画上了,该连的线也都连对了,这样的检查叫LVS(Layout Vs. Schematic) LVS 验证需要的三个文件:GDS2、网表文件(Netlist File )和LVS 命令文件LOGO绘制版图——DRC 检查LOGO 绘制版图——DRC 检查LOGO绘制版图LOGO DRC 检查LOGODRC 检查LOGO DRC 检查LOGO画Schematic ,提取网表文件1)网表文件(Netlist File )1.LOGO 画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件C:\Users\bm\Documents\Tanner EDA\Tanner Tools v15.0\Designs\RingVCO\RingVCO.tannerLOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件iLOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件LOGO画Schematic ,提取网表文件LOGO 画Schematic ,提取网表文件LOGO导出的网表文件LOGO GDS2LOGOGDS2LOGO GDS2LOGOGDS2LOGO LVS LOGOLVSLOGO LVS LOGOLVSLOGO LVSLOGOLVSLOGO LVS LOGOLVSLOGO 把网表文件里面的nmos W 改为2umLOGO输出文件为inv.out打开inv.out 文件LOGO LVS 验证结果LOGOLVS 验证结果LOGOLVS如果LVS 没有通过,这时需要查看LVS 报告——*.out 。

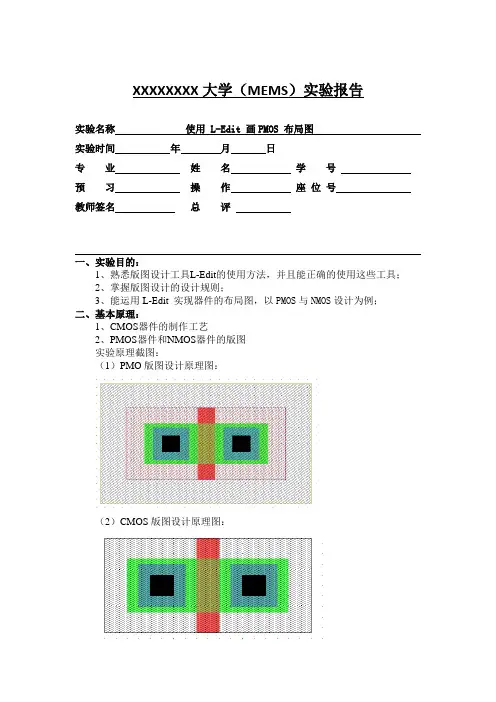

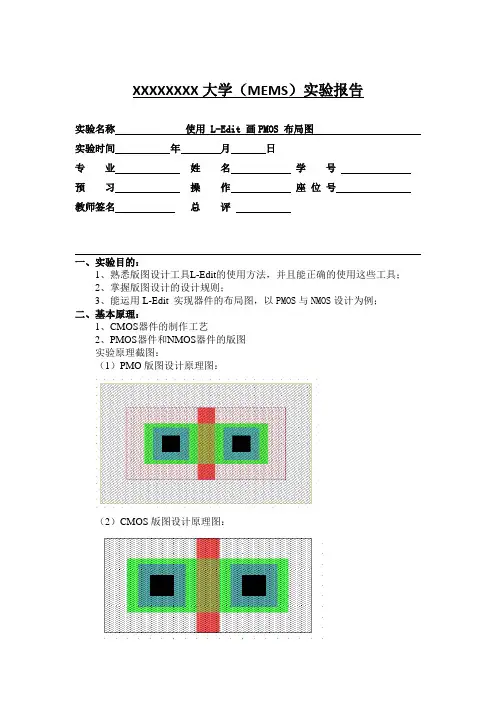

XXXXXXXX大学(MEMS)实验报告实验名称使用 L-Edit 画PMOS 布局图实验时间年月日专业姓名学号预习操作座位号教师签名总评一、实验目的:1、熟悉版图设计工具L-Edit的使用方法,并且能正确的使用这些工具;2、掌握版图设计的设计规则;3、能运用L-Edit 实现器件的布局图,以PMOS与NMOS设计为例;二、基本原理:1、CMOS器件的制作工艺2、PMOS器件和NMOS器件的版图实验原理截图:(1)PMO版图设计原理图:(2)CMOS版图设计原理图:3、设计版图时的注意事项:(1)L-Edit编辑环境是预设在P型基板上,故在P型基板上制作PMOS的第一步是需要做出N Well区,即需设定N阱区;然而对于NMOS则不需要N Well群区。

此外在设计版图时,需要将图绘制在原点之上,否则不利用版图截面的观察。

(2)改变图形大小的方法:“alt+鼠标拖动边框”;移动图形的方法“alt+鼠标拖动图形”;(3)绘制各图层之前需先通过Tools---DRC Setup查看对应的设计规则,从而选择确定图层的大小;绘制完一个图层都需DRC 进行设计规则检查;(4)各图层绘制无先后顺序的规定;(5)绘图时可适当使用“尺子”功能,以确保版图设计的对称性;清除图中的“尺寸”使用“View---Objects---Rules”或者选中后删除。

(6)对版图设计时,要注意时刻遵循设计规则,否则会出错误。

(7)对版图进行截面观察时,应注意选择好文件的路径,并且要设置好适当的界线位置。

三、实验内容及步骤:(1)打开 L-Edit 程序。

(2)另存新文件:选择 File---Save As命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录,在“文件名”文本框中输入新文件名称,例如:exp3。

(3)取代设定:选择File---Replace Setup命令,单击出现的对话框的From file 下拉列表右侧的 Browser按钮,择…:\LEdit83\Samples\SPR\example1\lights.tdb文件,再单击 OK 按钮,就可将 lights.tdb 文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

XXXXXXXX大学(MEMS)实验报告实验名称使用 L-Edit 画PMOS 布局图实验时间年月日专业姓名学号预习操作座位号教师签名总评一、实验目的:1、熟悉版图设计工具L-Edit的使用方法,并且能正确的使用这些工具;2、掌握版图设计的设计规则;3、能运用L-Edit 实现器件的布局图,以PMOS与NMOS设计为例;二、基本原理:1、CMOS器件的制作工艺2、PMOS器件和NMOS器件的版图实验原理截图:(1)PMO版图设计原理图:(2)CMOS版图设计原理图:3、设计版图时的注意事项:(1)L-Edit编辑环境是预设在P型基板上,故在P型基板上制作PMOS的第一步是需要做出N Well区,即需设定N阱区;然而对于NMOS则不需要N Well群区。

此外在设计版图时,需要将图绘制在原点之上,否则不利用版图截面的观察。

(2)改变图形大小的方法:“alt+鼠标拖动边框”;移动图形的方法“alt+鼠标拖动图形”;(3)绘制各图层之前需先通过Tools---DRC Setup查看对应的设计规则,从而选择确定图层的大小;绘制完一个图层都需DRC 进行设计规则检查;(4)各图层绘制无先后顺序的规定;(5)绘图时可适当使用“尺子”功能,以确保版图设计的对称性;清除图中的“尺寸”使用“View---Objects---Rules”或者选中后删除。

(6)对版图设计时,要注意时刻遵循设计规则,否则会出错误。

(7)对版图进行截面观察时,应注意选择好文件的路径,并且要设置好适当的界线位置。

三、实验内容及步骤:(1)打开 L-Edit 程序。

(2)另存新文件:选择 File---Save As命令,打开“另存为”对话框,在“保存在”下拉列表框中选择存储目录,在“文件名”文本框中输入新文件名称,例如:exp3。

(3)取代设定:选择File---Replace Setup命令,单击出现的对话框的From file 下拉列表右侧的 Browser按钮,择…:\LEdit83\Samples\SPR\example1\lights.tdb文件,再单击 OK 按钮,就可将 lights.tdb 文件的设定选择性应用在目前编辑的文件,包括格点设定、图层设定等。

版图工具ledit使用技巧(转)4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具(Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA T ools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。