第3章工艺基础及版图的层分解

- 格式:ppt

- 大小:2.92 MB

- 文档页数:96

工艺流程图识图基础知识工艺流程图是工艺设计的关键文件,同时也是生产过程中的指导工具.而在这里我们要讲的只是其在运用于生产实际中大家应了解的基础知识(涉及化工工艺流程设计的内容有兴趣的师傅可以找些资料来看)。

它以形象的图形、符号、代号,表示出工艺过程选用的化工设备、管路、附件和仪表等的排列及连接,借以表达在一个化工生产中物量和能量的变化过程。

流程图是管道、仪表、设备设计和装置布置专业的设计基础,也是操作运行及检修的指南.在生产实际中我们经常能见到的表述流程的工艺图纸一般只有两种,也就是大家所知道的PFD和P&ID。

PFD实际上是英文单词的词头缩写,全称为Process Flow Diagram,翻译议成中文就是“工艺流程图”的意思.而P&ID也是英文单词的词头缩写,全称为Piping and Instrumentation Diagram,“&"在英语中表示and.整句翻译过来就是“工艺管道及仪表流程图”。

二者的主要区别就是图中所表达内容多少的不同,PFD较P&ID内容简单。

更明了的解释就是P&ID图纸里面基本上包括了现场中所有的管件、阀门、仪表控制点等,非常全面,而PFD图将整个生产过程表述明白就可以了,不必将所有的阀门、管件、仪表都画出来。

另外,还有一种图纸虽不是表述流程的,但也很重要即设备布置图。

但相对以上两类图而言,读起来要容易得多,所以在后面只做简要介绍。

下面就介绍一下大家在图纸中经常看到的一些内容及表示方法。

1 流程图主要内容不管是哪一种,那一类流程图,概括起来里面的内容大体上包括图形、标注、图例、标题栏等四部分,我们在拿到一张图纸后,首先就是整体的认识一下它的主要内容。

具体内容分别如下:a 图形将全部工艺设备按简单形式展开在同一平面上,再配以连接的主、辅管线及管件,阀门、仪表控制点等符号。

b 标注主要注写设备位号及名称、管段编号、控制点代号、必要的尺寸数据等。

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

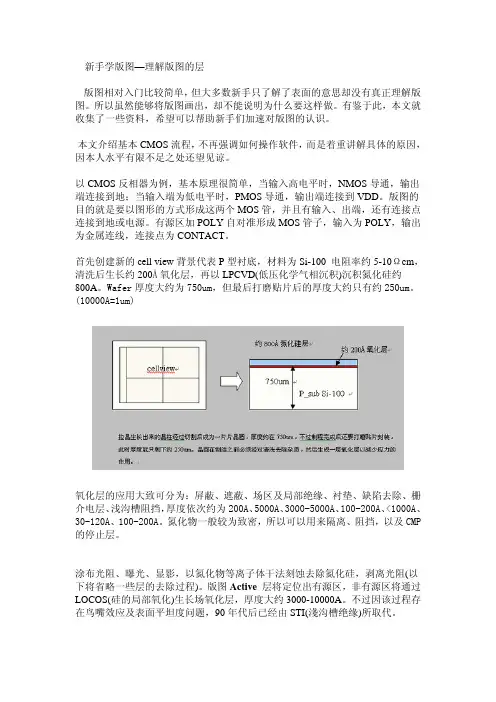

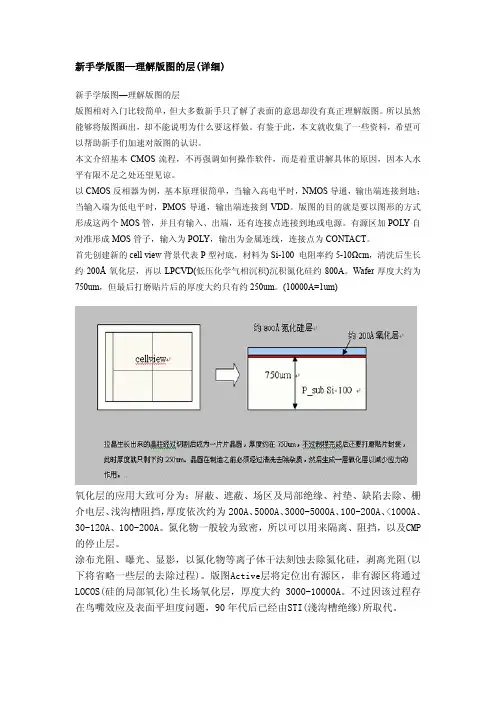

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

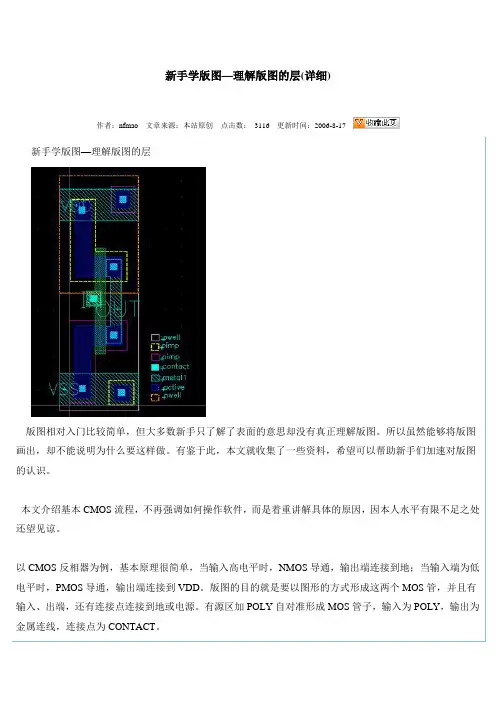

新手学版图—理解版图的层(详细)作者:nfmao 文章来源:本站原创 点击数: 3116 更新时间:2006-8-17新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS 流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS 反相器为例,基本原理很简单,当输入高电平时,NMOS 导通,输出端连接到地;当输入端为低电平时,PMOS 导通,输出端连接到VDD 。

版图的目的就是要以图形的方式形成这两个MOS 管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY 自对准形成MOS 管子,输入为POLY ,输出为金属连线,连接点为CONTACT 。

阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via 1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

基础工艺知识点总结图一、工艺定义及分类1. 工艺概念工艺是指制造、加工、装饰等生产过程中所采用的一定的技术方法和技能。

工艺是指导生产过程的技术规程和技术方法的总称。

2. 工艺分类根据工艺制品的用途和特点,可以将工艺分为装饰工艺、实用工艺、半实用工艺、古代工艺、现代工艺等几类。

二、基础工艺知识点1. 工艺原理工艺原理是指在实际生产过程中,根据材料的性能、结构特点和生产要求,选择合理的工艺方法和工艺流程,实现产品的加工、装饰等目标。

2. 材料与工艺材料是工艺的基础,不同的材料需要不同的工艺方法和技术。

在选材时需要考虑材料的性能、结构和使用要求,合理选择工艺方法和工艺流程。

3. 工艺标准工艺标准是对工艺的技术规范和要求的总称,它包括工艺流程、工艺规程、工艺参数、工艺装备等内容,是保证产品质量的重要依据。

4. 工艺设计工艺设计是指在产品设计的基础上,根据产品的结构、材料和性能要求,选择合适的工艺方法和技术,设计生产加工工艺流程和工艺设备。

5. 工艺装备工艺装备是指实现工艺过程所需要的各种设备和工具,包括粗加工设备、精加工设备、装饰设备、检测设备等。

6. 工艺流程工艺流程是指工件在生产加工过程中经历的一系列工艺操作的总和,包括原材料加工处理、生产加工、装饰处理、质检等环节。

7. 工艺控制工艺控制是指在生产加工过程中,通过控制加工参数、监测产品质量等手段,保证产品的生产过程和产品质量符合要求。

8. 工艺改进工艺改进是指在生产实践中,根据产品改进和生产要求,不断对工艺方法、流程、设备等进行改善和提高,以达到提高产品质量和生产效率的目的。

9. 工艺标准化工艺标准化是指对生产过程和产品质量进行规范管理,确保产品和生产过程符合相关的国家标准和质量要求。

10. 工艺艺术工艺艺术是指在工艺制品生产过程中,根据产品的功能和美学要求,进行装饰、雕刻、绘制等艺术处理,使产品在艺术性和实用性上达到更高的水平。

11. 工艺技术工艺技术是指在生产加工过程中所使用的各种工艺方法、工艺设备和技术手段,包括传统工艺技术和现代工艺技术等。

新手学版图—理解版图的层(详细)新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POL Y自对准形成MOS管子,输入为POL Y,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。