第3章 工艺基础及版图的层

- 格式:ppt

- 大小:2.92 MB

- 文档页数:96

新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

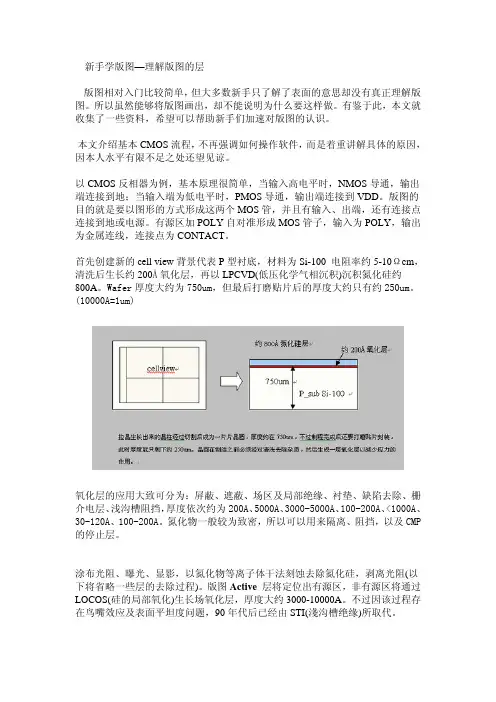

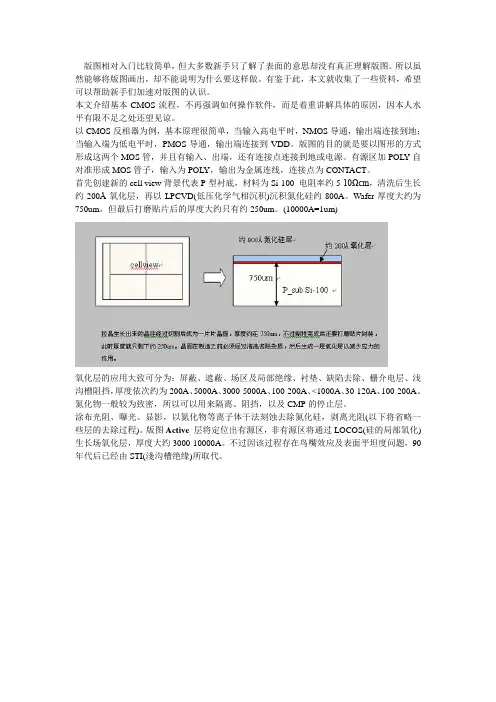

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

新手学版图—理解版图的层(详细)作者:nfmao 文章来源:本站原创 点击数: 3116 更新时间:2006-8-17新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS 流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS 反相器为例,基本原理很简单,当输入高电平时,NMOS 导通,输出端连接到地;当输入端为低电平时,PMOS 导通,输出端连接到VDD 。

版图的目的就是要以图形的方式形成这两个MOS 管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY 自对准形成MOS 管子,输入为POLY ,输出为金属连线,连接点为CONTACT 。

阻,光照射的区域可溶化,以此定位出开孔区域。

孔内金属是以MOCVD(金属有机化学气相沉积CVD)形式沉积金属W(钨),再以CMP方式打磨多余的金属。

濺射第一层金属,并以版图metal1层,刻画出金属连线。

覆盖CMP(介电层),以同样的方式开孔(版图via 1层),刻画第二层金属(版图metal2层)。

如果是完整的项目还要使用版图pass层开出PAD的位置,并进行钝化处理以PECVD(介质等离子体增强化学气相沉积)沉积氮化硅,以达到保护芯片的目的。

现在各层的作用已经有了说明,接下来将利用实际的作用来举例说明,层与层之间的关系。

1,版图P-well层,N-wel l层在衬底形成各自的阱区,它们之间的关系应该不能相互重叠。

2,因为器件形成在阱中,所以器件的图形必须被阱所覆盖,要么在P-well中,要么在N-well中。

3,P-well与P-well,N-well与N-well是否可以相连,取决于特性是否一致,比如相同的电位。

数字集成电路物理设计作者:陈春章艾霞王国雄出版社:科学出版社出版日期:2008年1月页数:285 装帧:开本:16 版次:商品编号:2022071 ISBN:703022031 定价:36元丛书序前言第1章集成电路物理设计方法1.1数字集成电路设计挑战1.2数字集成电路设计流程l.2.1展平式物理设计1.2.2硅虚拟原型设计1.2.3层次化物理设计1.3数字集成电路设计收敛1.3.1时序收敛1.3.2功耗分析1.3.3可制造性分析1.4数字集成电路设计数据库1.4.1数据库的作用与结构1.4.2数据库的应用程序接口1.4.3数据库与参数化设计1.5总结习题参考文献第2章物理设计建库与验证2.1集成电路工艺与版图2.1.1 CMOS集成电路制造工艺简介2.1.2 CMOS器件的寄生闩锁效应2.1.3版图设计基础2.2设计规则检查2.2.1版图设计规则2.2.2 DRC的图形运算函数2.2.3 DRC在数字IC中的检查2.3电路规则检查2.3.1电路提取与比较2.3.2电气连接检查2.3.3器件类型和数目及尺寸检查数字集成电路物理设计2.3.4 LVS在数字IC中的检查2.4版图寄生参数提取与设计仿真2.4.1版图寄生参数提取2.4.2版图设计仿真2.5逻辑单元库的建立2.5.1逻辑单元类别2.5.2逻辑单元电路2.5.3物理单元建库与数据文件2.5.4时序单元建库与数据文件2.5.5工艺过程中的天线效应2.6总结习题参考文献第3章布图规划和布局3.1布图规划3.1.1布图规划的内容和目标3.1.2 I/0接口单元的放置与供电3.1.3布图规划方案与延迟预估3.1.4模块布放与布线通道3.2电源规划3.2.1电源网络设计3.2.2数字与模拟混合供电3.2.3时钟网络3.2.4多电源供电3.3布局3.3.1展平式布局3.3.2层次化布局3.3.3布局目标预估3.3.4标准单元布局优化算法3.4扫描链重组3.4.1扫描链定义3.4.2扫描链重组3.5物理设计网表文件3.5.1设计交换格式文件3.5.2其他物理设计文件3.6总结习题参考文献第4章时钟树综合4.1时钟信号4.1.1系统时钟与时钟信号的生成4.1.2时钟信号的定义4.1.3时钟信号延滞4.1.4时钟信号抖动4.1.5时钟信号偏差4.2时钟树综合方法4.2.1时钟树综合与标准设计约束文件4.2.2时钟树结构4.2.3时钟树约束文件与综合4.3时钟树设计策略4.3.1时钟树综合策略4.3.2时钟树案例4.3.3异步时钟树设计4.3.4锁存器时钟树4.3.5门控时钟4.4时钟树分析4.4.1时钟树与时序分析4.4.2时钟树与功耗分析4.4.3时钟树与噪声分析4.5总结习题参考文献第5章布线5.1全局布线5.1.1全局布线目标5.1.2全局布线规划5.2详细布线5.2.1详细布线目标5.2.2详细布线与设计规则5.2.3布线修正5.3其他特殊布线5.3.1电源网络布线5.3.2时钟树布线5.3.3总线布线数字集成电路物理设计5.3.4实验布线5.4布线算法5.4.1通道布线和面积布线5.4.2连续布线和多层次布线5.4.3模块设计和模块布线5.5总结习题参考文献第6章静态时序分析6.1延迟计算与布线参数提取6.1.1延迟计算模型6.1.2电阻参数提取6.1.3电容参数提取6.1.4电感参数提取6.2寄生参数与延迟格式文件6.2.1寄生参数格式sPF文件6.2.2标准延迟格式SDF文件6.2.3 sDF文件的应用6.3静态时序分析6.3.1时序约束文件6.3.2时序路径与时序分析6.3.3时序分析特例6.3.4统计静态时序分析6.4时序优化6.4.1造成时序违例的因素6.4.2时序违例的解决方案6.4.3原地优化6.5总结习题参考文献第7章功耗分析7.1静态功耗分析7.1.1反偏二极管泄漏电流7.1.2门栅感应漏极泄漏电流7.1.3亚阈值泄漏电流7.1.4栅泄漏电流7.15静态功耗分析第8章信号完整性分析第9章低功耗设计技术与物理实施第10章芯片设计的终验证与签核附录索引数字专用集成电路的设计与验证本书作者:杨宗凯,黄建,杜旭编著第1章概述1.1 引言1.2 ASIC的概念1.3 ASIC开发流程1.4 中国集成电路发展现状第2章Verilog HDL硬件描述语言简介2.1 电子系统设计方法的演变过程2.2 硬件描述语言综述2.3 Verilog HDL的基础知识2.4 Verilog HDL的设计模拟与仿真第3章ASIC前端设计3.1 引言3.2 ASIC前端设计概念3.3 ASIC前端设计的工程规范3.4 设计思想3.5 结构设计3.6 同步电路3.7 ASIC前端设计基于时钟的划分3.8 同步时钟设计3.9 ASIC异步时钟设计4.10 小结第4章ASIC前端验证4.1 ASIC前端证综述4.2 前端验证的一般方法4.3 testbench4.4 参考模型4.5 验证组件的整合与仿真4.6 小结第5章逻辑综合5.1 综合的原理和思路5.2 可综合的代码的编写规范5.3 综合步骤5.4 综合的若干问题及解决……第6章可测性技术第7章后端验证附录A 常用术语表附录B Verilog语法和词汇惯用法附录C Verilog HDL关键字附录D Verilog 不支持的语言结构参考文献yoyobao编号:book194094作者:杨宗凯,黄建,杜旭编著(点击查看该作者所编图书)出版社:电子工业出版社(点击查看该出版社图书)出版日期:2004-10-1ISBN:7121003783装帧开本:胶版纸/0开/ 0页/480000字版次:1原价:¥28VLSI设计方法与项目实施点击看大图市场价:¥43.00 会员价:¥36.55【作者】邹雪城;雷鑑铭;邹志革;刘政林[同作者作品]【丛书名】普通高等教育“十一五”规划教材【出版社】科学出版社【书号】9787030194510【开本】16开【页码】487【出版日期】2007年8月【版次】1-1【内容简介】本书以系统级芯片LCD控制器为例,以数模混合VLSI电路设计流程为线索,系统地分析了VLSI系统设计方法,介绍了其设计平台及流行EDA软件。

版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POL Y自对准形成MOS管子,输入为POL Y,输出为金属连线,连接点为CONTACT。

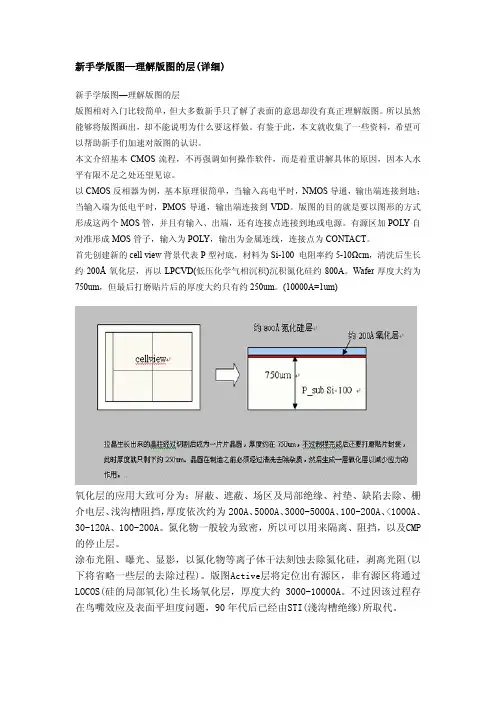

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

用版图N-well层定位N-well区域,离子植入P+/600KeV/2x10^13cm^-2。

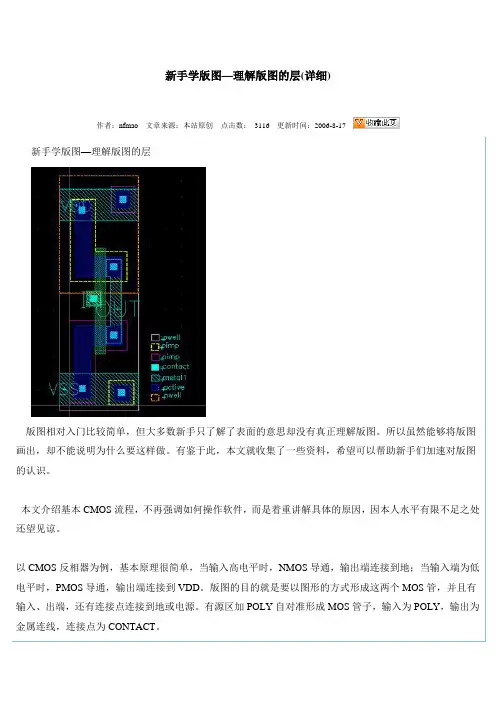

新手学版图—理解版图的层(详细)新手学版图—理解版图的层版图相对入门比较简单,但大多数新手只了解了表面的意思却没有真正理解版图。

所以虽然能够将版图画出,却不能说明为什么要这样做。

有鉴于此,本文就收集了一些资料,希望可以帮助新手们加速对版图的认识。

本文介绍基本CMOS流程,不再强调如何操作软件,而是着重讲解具体的原因,因本人水平有限不足之处还望见谅。

以CMOS反相器为例,基本原理很简单,当输入高电平时,NMOS导通,输出端连接到地;当输入端为低电平时,PMOS导通,输出端连接到VDD。

版图的目的就是要以图形的方式形成这两个MOS管,并且有输入、出端,还有连接点连接到地或电源。

有源区加POLY自对准形成MOS管子,输入为POLY,输出为金属连线,连接点为CONTACT。

首先创建新的cell view背景代表P型衬底,材料为Si-100 电阻率约5-10Ωcm,清洗后生长约200Å氧化层,再以LPCVD(低压化学气相沉积)沉积氮化硅约800A。

Wafer厚度大约为750um,但最后打磨贴片后的厚度大约只有约250um。

(10000A=1um)氧化层的应用大致可分为:屏蔽、遮蔽、场区及局部绝缘、衬垫、缺陷去除、栅介电层、浅沟槽阻挡,厚度依次约为200A、5000A、3000-5000A、100-200A、<1000A、30-120A、100-200A。

氮化物一般较为致密,所以可以用来隔离、阻挡,以及CMP 的停止层。

涂布光阻、曝光、显影,以氮化物等离子体干法刻蚀去除氮化硅,剥离光阻(以下将省略一些层的去除过程)。

版图Active层将定位出有源区,非有源区将通过LOCOS(硅的局部氧化)生长场氧化层,厚度大约3000-10000A。

不过因该过程存在鸟嘴效应及表面平坦度问题,90年代后已经由STI(淺沟槽绝缘)所取代。

版图P-well层定位P-well区域,在这一区域离子植入B+/225KeV/3x10^13cm^-2。

“VLS I设计基础”复与思考题选用教材:VLSI设计基础”李伟华编著电子工业出版社2002 年10 月第一版参考教材半导体集成电路”,张开华编著,东南大学出版社,1995 年7 月第一版。

第1 章“VLS 工设计基础概述” 复与思考题(p.1~3)第2 章“MOS 器件与工艺基础”复习思考题(p.4~9)第3 章“工艺与设计接口”复习思考题(p.10)第4 章“晶体管规则阵列设计技术”复习思考题(p.10~13)第5 章“单元库设计技术”复习思考题(p.13~17)第6 章“微处理器”复习思考题(p.17~22)第7 章“集成电路的测试”复习思考题(p.22~23)第1 章“VLS 工设计基础概述” 复与思考题1. 为什么CMOS(含BiCMOS)工艺成为VLSI主流工艺?其最大特点是什么?在微电子技术领域,集成电路的制造有两个主要的实现技术:双极技术与MOS 技术。

CMOS 以其结构简单,集成度高,耗散功率小等优点,成为当今VLSI制造的主流技术。

其最大特点是耗散功率小。

2. 双极工艺还有用武之地吗?双极技术是以NPN 与PNP 晶体管为基本元件,融合其他的集成元件构造集成电路的技术方法。

双极器件以其速度高和驱动能力大,高频、低噪声等优良特性,在集成电路的设计制造领域,尤其是模拟集成电路的设计制造领域,占有一席之地。

但双极器件的耗散功率比较大,限制了它在VLSI系统中的应用。

3. 以你的体会,你认为集成电路设计师应具备哪些基本技术基础?设计者必须具备下列的技术基础:电路与逻辑没计技术基础,器件与工艺技术基础,版图设计技术基础和集成电路计算机辅助设计技术基础。

除此之外,设计者还应具备对电路、逻辑、器件、工艺和版图的分析能力。

4. 简要说明描述集成电路技术水平5 大指标的含义。

大指标的含义。

当前国内和国际上集成电路产业在特征尺寸及晶园尺寸方面各达到什么水平?寸及晶园尺寸方面各达到什么水平? 1 集成度是以一个IC 芯片所包含的元件(晶体管或门/数)来衡量,集成度特征尺寸特征尺寸定义为器件中最小线条宽度(对MOS 器件而言,通常指器件栅电极所决定的沟道长度的几何长度),芯片芯片面积大小,晶片直径晶片直径大小,封装引脚数封装引脚数多少。

图纸及工艺的理解(工艺部分)一工艺过程生产过程中直接改变对象的形状、尺寸、相对位置和性能的过程,称为工艺过程,可以通过不同的工艺方法来完成。

因而工艺过程又可具体分为铸造、锻造、冲压、焊接、机械加工、特种加工、热处理、表面处理、装配等工艺过程。

采用机械加工方法,直接改变加工对象的形状、尺寸和表面性能,使之成为成品的过程,称为机械加工工艺过程。

机械加工工艺过程是由若干个按一定顺序排列的工序组成。

1.工序工序是指一个或一组工人,在一个工作地对同一个或同时几个工件所连续完成的那一部分工艺过程。

划分工序的主要依据是工作地点是否改变和加工是否连续。

这里的连续,是指工序内的工作需连续完成,不能插入其它工作内容或者阶段性加工。

工序是组成工艺过程的基本单元。

工序又可细分为安装、工位、工步、走刀等组成部分。

2.安装安装是指工件(或装配单元)通过一次装夹后所完成的那一部分工序。

3.工位工位是指在一次装夹中,工件在机床上所占的每个位置上所完成那一部分工序。

4.工步工步是指在加工表面(或装配时的连续表面)不变、加工工具不变和切削用量不变的条件下,所连续完成的那部分工序。

工步是构成工序的基本单元。

5.走刀走刀是指刀具相对工件加工表面进行一次切削所完成的那部分工作。

每个工步可包括一次走刀或几次走刀。

二定位基准的选择一、基准的概念及分类零件上用以确定其它点、线、面的位置所依据的那些点、线、面称为基准。

根据其功用的不同,可分为设计基准、工艺基准两大类。

(1)设计基准在零件图上用以确定其它点、线、面的基准,称为设计基准。

(2)工艺基准零件在加工、测量、装配等工艺过程中使用的基准统称工艺基准。

工艺基准又可分为:1、装配基准在零件或部件装配时用以确定它在机器中相对位置的基准。

2、测量基准用以测量工件已加工表面所依据的基准。

例如以内孔定位用百(千)分表测量外圆表面的径向跳动,则内孔就是测量外圆表面径内跳动的测量基准。

3、工序基准在工序图中用以确定被加工表面位置所依据的基准。