第8章集成电路版图设计

- 格式:ppt

- 大小:2.26 MB

- 文档页数:48

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

集成电路设计综合实验报告班级:微电子学1201班姓名:学号:日期:2016年元月13日一.实验目的1、培养从版图提取电路的能力2、学习版图设计的方法和技巧3、复习和巩固基本的数字单元电路设计4、学习并掌握集成电路设计流程二.实验内容1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

2. 设计一个CMOS结构的二选一选择器。

(1)根据二选一选择器功能,分析其逻辑关系。

(2)根据其逻辑关系,构建CMOS结构的电路图。

(3)利用EDA工具画出其相应版图。

(4)利用几何设计规则文件进行在线DRC验证并修改版图。

三.实验原理1. 反向提取给定电路模块方法一:直接将版图整体提取(如下图)。

其缺点:过程繁杂,所提取的电路不够直观,不易很快分析出其电路原理及实现功能。

直接提取的整体电路结构图方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。

其优点:使电路结构更简洁直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。

CMOS反相器模块CMOS反相器的symbolCMOS传输门模块 CMOS传输门的symbolCMOS三态门模块 CMOS三态门的symbolCMOS与非门模块 CMOS与非门的symbol各模块symbol按版图连接方式组合而成的整体电路经分析可知,其为一个带使能端的D锁存器,逻辑功能如下:①当A=1,CP=0时,Q=D,Q—=D—;②当A=1,CP=1时,Q、Q—保持;③当A=0,Q=0,Q—=1。

2.CMOS结构的二选一选择器二选一选择器(mux2)的电路如图所示,它的逻辑功能是:①当sel=1时,选择输入A通过,Y=A;②当sel=0时,选择输入B通过,Y=B。

二选一选择器(mux2)由三个与非门(nand)和一个反相器(inv)构成(利用实验1 的与非门和反相器symbol即可)。

《集成电路版图设计》课内实验学院:信息学院专业班级:学号:学生姓名:指导教师:模拟集成电路版图设计集成电路版图是电路系统与集成电路工艺之间的中间环节,是一个不可少的重要环节。

通过集成电路的版图设计,可以将立体的电路系统变为一个二维的平面图形,再经过工艺加工还原于基于硅材料的立体结构。

因此,版图设计是一个上承的电路系统,下接集成电路芯片制造的中间桥梁,其重要性可见一斑。

但是,集成电路版图设计是一个令设计者感到困惑的一个环节,我们常常感到版图设计似乎没有什么规矩,设计的经验性往往掩盖了设计的科学性,即使是许多多年版设计经验的人有时候也说不清楚为何要这样或者那样设计。

在此,集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但它更需要设计者的创造性,空间想象力和耐性,需要设计者长期工作的经验和知识的积累,需要设计者对日异月新的集成电路发展密切关注和探索。

一个优秀的版图设计者对于开发超性能的集成电路是极其关键的。

在版图的设计和学习中,我们一直会面临匹配技术降低寄生参数技术熟悉电路作用(功能,频率)电流密度的计算(大电流和小电流的电流路径以及电流流向)等这些基本,它们也是最重要的问题。

版图的设计,从半导体制造工艺,到最后的后模拟过程都是非常关键的,里面所涉及的规则有1500——2000条,一些基本问题的解决方法和设计的调理化都将在下面提及。

模拟集成电路版图设计流程:阅读研究报告理解电路原理图了解电路的作用熟悉电流路径晶大小知道匹配器件明白电路中寄生,匹配,噪声的产生及解决方案对版图模块进行平面布局对整个版图进行平面布局熟练运用cadence软件进行版图绘制Esd的保护设计进行drc与lvs检查整理整个过程中的信息时刻做记录注意在设计过程中的交流集成电路制造工艺双极工艺:Cmos(p阱)工艺:版图设计经验总结:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

集成电路版图设计

集成电路版图设计是指将电子元器件(如晶体管、电阻、电容等)根据电路图的要求进行布局和连线的过程,实现电路功能并将其制作成一张版图以供电路的制造和生产。

集成电路版图设计主要包括以下几个步骤:

1. 电路分析:根据电路的功能及要求,进行电路分析,确定电路的基本结构和模块。

2. 元件选择:根据电路的功能和性能要求,选择合适的元件进行布局。

不同的元件具有不同的特性,如低噪声、快速开关、高频率等,需根据实际要求进行选择。

3. 布局设计:根据电路的结构和模块,将元件进行合理的布局。

布局的目的是使得电路平衡,减少干扰和噪声,并提高电路的稳定性和可靠性。

4. 连线设计:根据电路的功能要求,将各个元件进行连线,形成完整的电路。

连线的设计需要合理安排电路信号的传输路径,避免信号干扰和交叉干扰。

5. 优化设计:对布局和连线进行优化,以提高电路的性能。

例如,优化连线的长度和宽度,减少信号延迟和功耗。

6. 输出版图:将优化后的电路设计转化成计算机可识别的格式,并输出成版图文件。

版图文件可以用于电路的制造和生产。

集成电路版图设计的目的是在满足电路功能要求的前提下,使电路布局和连线达到最佳性能。

对于大规模集成电路(VLSI)设计,还需要考虑功耗、热量和信号完整性等因素,以实现高集成度和高性能的电路设计。

随着技术的不断发展,集成电路版图设计也在不断演进,从传统的手工设计发展到计算机辅助设计(CAD)和自动化设计(EDA),大大提高了设计效率和准确性。

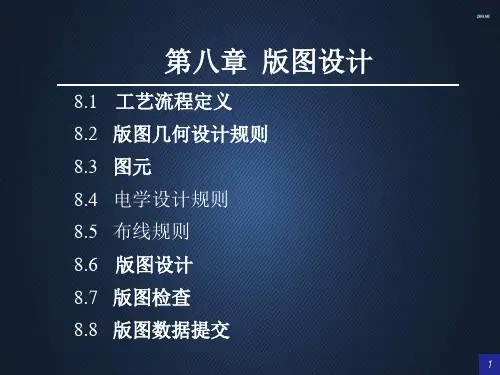

2023-11-04CATALOGUE目录•集成电路布图设计概述•集成电路布图设计的基本要素•集成电路布图设计的技巧和方法•集成电路布图设计的工具与平台•集成电路布图设计的挑战与解决方案•集成电路布图设计的应用案例01集成电路布图设计概述集成电路布图设计是指将电子器件及其连接关系以几何图形的方式在集成电路芯片上分布并按照一定规则布局的技术方案。

定义集成电路布图设计具有高度复杂性、精密性和集成性,要求设计者具备深厚的电子设计自动化(EDA)工具使用技能和专业知识。

特点定义与特点物理设计根据逻辑电路设计,进行布局布线、信号完整性分析等物理设计,生成可制造的版图文件。

设计输入明确设计需求,提供功能描述和性能参数等设计输入信息。

逻辑设计将功能描述转化为逻辑电路,进行功能仿真和调试。

版图验证对版图文件进行功能和性能验证,确保设计与制造的一致性。

制造与测试将版图文件交由半导体制造厂进行芯片制造,并进行测试与验证。

合理的布图设计可以优化芯片的性能、速度和功耗等方面的表现。

提高芯片性能降低制造成本推动产业发展通过优化布图设计,可以提高芯片的可制造性和良品率,降低制造成本。

集成电路布图设计是半导体产业的核心技术之一,对于推动产业发展具有重要意义。

03020102集成电路布图设计的基本要素确定芯片的功能和性能参数,进行逻辑门级设计,实现功能描述到逻辑电路的转换。

逻辑设计进行芯片的物理布局和布线设计,包括信号完整性、电源完整性、时序等。

物理设计通过仿真工具对设计的电路进行功能和性能验证,确保设计的正确性。

仿真验证将电路设计转换为版图设计,需要考虑工艺、制程等因素对电路性能的影响。

抽象层次使用版图编辑工具进行版图的绘制和编辑,实现电路到版图的转换。

版图编辑对版图进行质量检查和验证,确保版图的正确性和可制造性。

版图验证检查版图设计是否符合制造工艺的要求,确保版图的可制造性。

设计规则检查(DRC)分析版图布局对电路性能的影响,以及各种寄生效应对电路性能的影响。

集成电路版图设计习题答案第8章 MOS场效应晶体管【习题答案】1.请画出MOS晶体管的结构示意图。

答:2.请简述MOS晶体管各个版图层的作用。

●答:阱层(Well):阱层定义在衬底上制备阱的区域。

NMOS管制备在P型衬底上,PMOS管制备在N型衬底上。

一块原始的半导体材料,掺入的杂质类型只能有一种,即该衬底不是N型就是P型。

如果不对衬底进行加工处理的话,该衬底只能制备一种MOS晶体管。

CMOS集成电路是把NMOS晶体管和PMOS晶体管制备在同一个硅片衬底上,为了能够制造CMOS集成电路,需要对衬底进行处理,利用掺杂工艺在衬底上形成一个区域,该区域的掺杂类型和衬底的掺杂类型相反,这个区域就称为阱。

●有源区层(Active):有源区层的作用是在衬底上定义制作有源区的区域,该区域包括源区、漏区和沟道。

在衬底上淀积厚氧化层,利用光刻和刻蚀工艺在衬底上开窗口并把厚氧化层除去就可形成有源区,有源区之外的区域是场区。

显然,MOS管必须而且只能制备在有源区内。

●多晶硅层(Poly):多晶硅层的作用是定义制作多晶硅材料的区域。

最早的MOS集成电路制造工艺只能制备一层多晶硅,而现在已经有能够制备两层多晶硅的工艺了。

对于双层多晶硅工艺,第一层多晶硅主要用来制作栅极、导线和多晶硅—多晶硅电容的下极板,第二层多晶硅主要用来制作多晶硅电阻和多晶硅-多晶硅电容的上极板。

双层多晶硅工艺具有多晶硅1和多晶硅2这两个版图层。

●P+注入层和N+注入层(P+implant和N+ implant):P+注入层定义注入P+杂质离子的区域,而N+注入层定义注入N+杂质离子的区域。

由于NMOS晶体管和PMOS晶体管的结构相同,只是源漏区的掺杂类型相反。

同时,有源区层只是定义了源区、漏区和沟道的区域,却没有说明源区和漏区的掺杂类型。

P+注入层和N+注入层说明了注入杂质的类型,也就是说明了有源区的导电类型,实现了NMOS晶体管和PMOS晶体管的区分。