用移位寄存器LS芯片实现扭环形计数器精编版

- 格式:ppt

- 大小:614.50 KB

- 文档页数:16

绪论单元测试1.数字电路研究输入输出的逻辑关系,因此具有逻辑运算能力。

A:对B:错答案:A2.数字电路中,三极管工作在放大状态。

A:错B:对答案:A3.数字电路的工作信号为数字信号。

A:错B:对答案:B4.正弦波是数字信号。

A:对B:错答案:B5.电子信号可分为模拟信号和数字信号两种形式。

A:对B:错答案:A第一章测试1.下面关于数字信号描述错误的是()A:数字信号是只具有0和1两个数码的二进制信号。

B:数字信号是离散的电压或电流信号。

C:数字信号是在时间和数值上连续变化的信号。

答案:C2.二进制数只有两个代码:0和1,因此二进制1+1=()A:2B:1C:10D:0答案:C3.以下代码中为相邻两组码只有一位代码有差异的是()。

A:8421BCD码B:自然二进制码C:格雷码D:余3码答案:C4.十进制数56转换成二进制等于()。

A:111100B:110001C:110000D:111000答案:D5.逻辑运算()。

A:B:0C:1D:A答案:A6.下列异或运算表示式中,正确的表示式是()。

A:1⊕1=1B:0⊕1=1C:1⊕0=0D:0⊕0=1答案:B7.设A、B均为逻辑变量,则下列逻辑关系正确的是()A:B:C:D:答案:B8.4个逻辑变量A、B、C、D组成的最小项的编号是()。

A:m4B:m10C:m11D:m12答案:C9.使逻辑函数为1的变量取值是( )。

A:011B:001C:111D:101答案:A10.具有约束的逻辑函数化简时遵循的原则之一,每个圈中至少含一个新的()。

A:约束项B:最小项C:与项答案:B11.用公式法化简逻辑函数答案:12.用卡诺图法化简带有约束项的逻辑函数(请注意:该题作答需要上传附件,限制50M以内)答案:13.用卡诺图法化简带有约束项的逻辑函数(请注意:该题作答需要上传附件,限制50M以内)答案:第二章测试1.数字电路正逻辑的规定是()A:用1表示低电平,用1表示高电平。

电路中的移位寄存器与计数器的原理与应用在现代科技中,电路是一个不可或缺的组成部分。

电路可以用于各种领域,其中移位寄存器和计数器是最为常见且重要的电路之一。

本文将深入探讨这两种电路的原理与应用。

一、移位寄存器的原理与应用移位寄存器是一种能够将输入数据连续地移位、保留并输出的电路。

其原理主要基于逻辑门电路的组合与连接。

1. 原理移位寄存器通常由多个触发器构成,触发器是一种能够存储一个二进制位的设备。

当输入数据进入移位寄存器时,触发器会按照一定的时序规律将数据进行移位,并输出。

移位寄存器可以实现向左(左移)或向右(右移)移动数据的功能。

2. 应用移位寄存器在数字系统中有广泛的应用。

例如,在串行通信中,移位寄存器可以将并行数据转化为串行数据进行传输;在移位加法器中,移位寄存器可以实现两个二进制数的相加;在移位寄存器阵列中,移位寄存器可以用于存储、处理和传输图像等。

二、计数器的原理与应用计数器是一种能够将输入的时钟信号进行计数并输出的电路。

计数器能够记录输入信号的数量,并根据设定的计数规则输出对应的结果。

1. 原理计数器通常由触发器和逻辑门电路构成。

当计数器接收到时钟信号时,触发器会根据时钟信号的上升沿或下降沿进行状态变换,从而实现计数功能。

计数器可以分为二进制计数器、十进制计数器等,根据不同的计数规则可以实现不同的计数功能。

2. 应用计数器在数字电路中有广泛的应用。

例如,在计算机中,计数器可以用于指示程序执行的步骤;在测量仪器中,计数器可以用于计算输入信号的频率或脉冲个数;在定时器中,计数器可以实现定时功能等。

综上所述,移位寄存器和计数器都是数字电路中重要的组成部分。

移位寄存器可以将输入数据按照一定的规律移位输出,广泛应用于数字系统中;计数器则可以根据输入的时钟信号进行计数输出,实现不同的计数功能。

这两种电路的原理与应用相互关联且互相补充,为数字电路的设计与实现提供了强大的工具与方法。

总之,了解移位寄存器和计数器的原理与应用对于理解和应用数字电路至关重要。

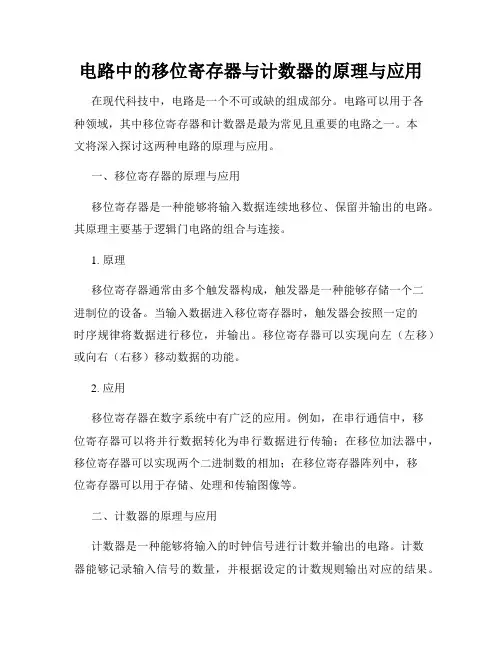

环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图见图23-5-1,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

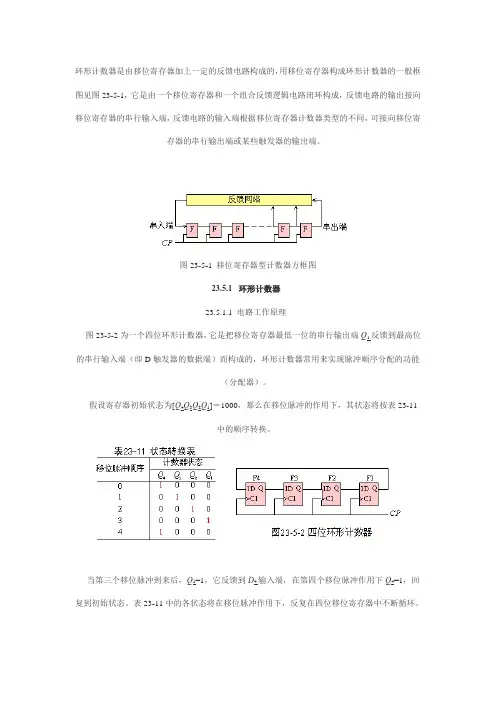

图23-5-1 移位寄存器型计数器方框图23.5.1 环形计数器23.5.1.1 电路工作原理图23-5-2为一个四位环形计数器,它是把移位寄存器最低一位的串行输出端Q1反馈到最高位的串行输入端(即D触发器的数据端)而构成的,环形计数器常用来实现脉冲顺序分配的功能(分配器)。

假设寄存器初始状态为[Q4Q3Q2Q1]=1000,那么在移位脉冲的作用下,其状态将按表23-11中的顺序转换。

当第三个移位脉冲到来后,Q1=1,它反馈到D4输入端,在第四个移位脉冲作用下Q4=1,回复到初始状态。

表23-11中的各状态将在移位脉冲作用下,反复在四位移位寄存器中不断循环。

由上述讲讨论可知,该环形计数的计数长度为N=n。

和二进制计数器相比,它有2n-n个状态没有利用,它利用的有效状态是少的。

23.5.1.2 状态转换图和工作时序表23-11中是以1000为初始状态的,它所对应的状态转换图见图23-5-3。

如果移位寄存器中的初始状态不同,就会有不同的状态转换图。

图23-5-4给出了四位环形计数器可能有的其它几种状态转换图。

图23-5-3 状态转换图(a) (b) (c) (d)图23-5-4 四位环行计数器其它的状态转换图图23-5-4(a)、(b)、(c)三个状态转换图中各状态是闭合的,相应的时序为循环时序。

当计数器处于图23-5-4(d)所示的状态0000或1111时,计数器的状态将不发生变化。

这两个状态称为悬态或死态。

四位环形计数器可能有这么多不同的循环时序,是我们不希望的,只能从这些循环时序中选出一个来工作,这就是工作时序,或称为正常时序,或有效时序。

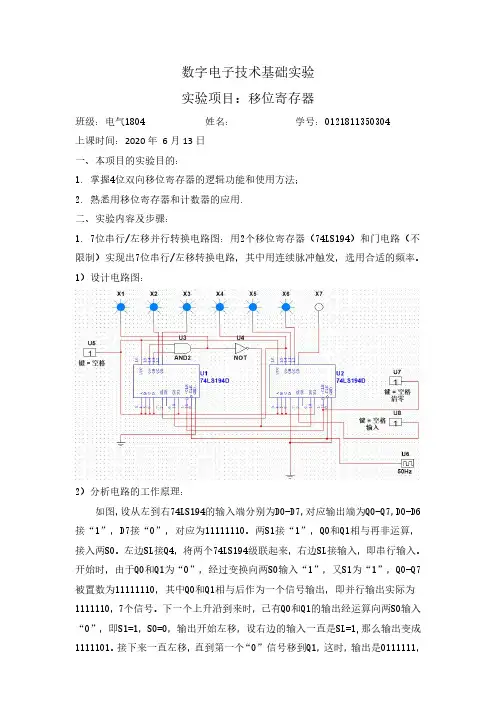

数字电子技术基础实验实验项目:移位寄存器班级:电气1804姓名:学号:0121811350304上课时间:2020年6月13日一、本项目的实验目的:1.掌握4位双向移位寄存器的逻辑功能和使用方法;2.熟悉用移位寄存器和计数器的应用.二、实验内容及步骤:1.7位串行/左移并行转换电路图:用2个移位寄存器(74LS194)和门电路(不限制)实现出7位串行/左移转换电路,其中用连续脉冲触发,选用合适的频率。

1)设计电路图:2)分析电路的工作原理:如图,设从左到右74LS194的输入端分别为D0-D7,对应输出端为Q0-Q7,D0-D6接“1”,D7接“0”,对应为11111110。

两S1接“1”,Q0和Q1相与再非运算,接入两S0。

左边SL接Q4,将两个74LS194级联起来,右边SL接输入,即串行输入。

开始时,由于Q0和Q1为“0”,经过变换向两S0输入“1”,又S1为“1”,Q0-Q7被置数为11111110,其中Q0和Q1相与后作为一个信号输出,即并行输出实际为1111110,7个信号。

下一个上升沿到来时,已有Q0和Q1的输出经运算向两S0输入“0”,即S1=1,S0=0,输出开始左移,设右边的输入一直是SL=1,那么输出变成1111101。

接下来一直左移,直到第一个“0”信号移到Q1,这时,输出是0111111,Q0=1,Q1=0,向两S0输入1,又S1=1,电路重新置数为1111110。

以上为一个循环,一个循环经过7个时钟脉冲,有7个输出状态,并且输出信号左移,也实现了串行输入,并行输出,所以该电路是7位串行/左移并行转换电路。

3)清零后观察输出状态,记录输出结果填入表中。

CP Q0Q1Q2Q3Q4Q5Q6Q7功能000000000清零111111110置数211111101送数311111011411110111511101111611011111710111111801111111911111110置数2.四位环形计数器:用一片移位寄存器(74LS194)及门电路(不限制)设计具有自启动功能的、有效状态分别为1000,0100,0010,0001(Q0Q1Q2Q3)的四位右移环形计数器,其中用连续脉冲触发,选用合适的频率。

实验六项目名称:移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

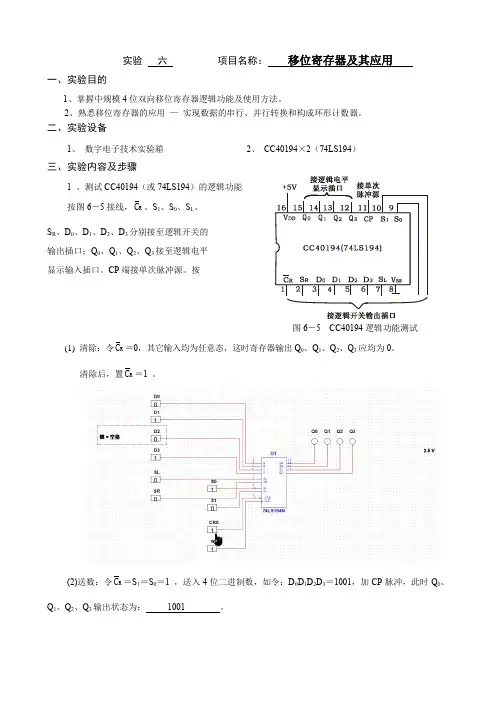

二、实验设备1、数字电子技术实验箱2、CC40194×2(74LS194)三、实验内容及步骤1 、测试CC40194(或74LS194)的逻辑功能按图6-5接线,R C、S1、S0、S L、S R、D0、D1、D2、D3分别接至逻辑开关的输出插口;Q0、Q1、Q2、Q3接至逻辑电平显示输入插口。

CP端接单次脉冲源。

按图6-5 CC40194逻辑功能测试(1)清除:令R C=0,其它输入均为任意态,这时寄存器输出Q0、Q1、Q2、Q3应均为0。

清除后,置R C=1 。

(2)送数:令R C=S1=S0=1 ,送入4位二进制数,如令:D0D1D2D3=1001,加CP脉冲,此时Q0、Q1、Q2、Q3输出状态为:1001 。

(3)右移:令R C=1,S1=0,S0=1,然后右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0100 ;紧接着,右移输入端S R送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:1010 ;紧接着,右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0101 ;紧接着,右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0010 。

(4) 左移:先令R C=0进行清零,再令R C=1,S1=1,S0=0,然后左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0001 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0011 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0111 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:1111 。

电子技术应用实验1(数字电路基础实验)_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.电源电压为5V的TTL门电路的阈值电压最接近以下哪个值?参考答案:1V2.电源电压为5V的CMOS门电路的阈值电压大约为多少?参考答案:2.5V3.用芯片74LS00(4个2输入与非门)实现反相器,未使用的引脚应该如何处理?参考答案:接另一个输入引脚_直接悬空_接5V电源4.在测量电源电压Vcc时,实验箱上指示灯亮,用万用表测量电源电压为5V,但示波器测出为0V,原因可能是示波器探头耦合方式未设置为()。

参考答案:直流5.在Verilog语言中assign语句是?参考答案:连续赋值语句6.关于Verilog语言中的always语句不正确的是?参考答案:只有wire类型数据可以在这个语句中被赋值7.Vivado中仿真文件的后缀为?参考答案:.v8.74LS163工作于计数状态,CP为2KHzTTL信号。

若用四个发光二极管去看74LS163的四个输出端,四个发光二极管看起来。

参考答案:常亮9.示波器探头衰减开关置为时,输入阻抗更大。

参考答案:10X档10.示波器探头设置中,在探头比为10х时的输入电容比探头比为1X时大。

参考答案:错误11.用双踪示波器同时测试频率不同、周期成整数倍的两个时序波形时,当某信号显示不同步时可能需要。

参考答案:调节触发释抑时间_重新选择示波器的触发源_调节示波器的触发电平位置12.用示波器只观察信号中的交流成分时,输入耦合应选择。

参考答案:交流耦合13.若CD4511输入为4位二进制码1011,其驱动的七段显示器显示是参考答案:无显示14.74LS00用作反相器使用时,下列哪种连接方法正确?参考答案:一个输入端接信号,另一个输入端接高电平_一个输入端接信号,另一个输入端悬空_两个输入端并接信号15.用示波器测量某点的直流电压值,示波器需要做以下哪些设置?参考答案:通道探头的设置和探头上的开关设置相对应_输入耦合方式为直流_对应通道的0V标志在屏幕上_能够在屏幕上看到该直流信号16.在测试74X139的逻辑功能实验中,当G'、A1、A0分别接0、1、0时,哪个端口的输出有效()。

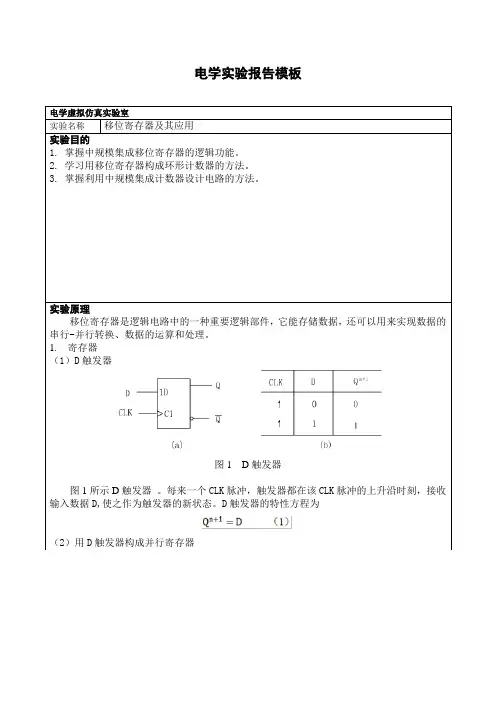

电学实验报告模板实验原理移位寄存器是逻辑电路中的一种重要逻辑部件,它能存储数据,还可以用来实现数据的串行-并行转换、数据的运算和处理。

1.寄存器(1)D触发器图1 D触发器图1所示D触发器。

每来一个CLK脉冲,触发器都在该CLK脉冲的上升沿时刻,接收输入数据D,使之作为触发器的新状态。

D触发器的特性方程为(2)用D触发器构成并行寄存器图2 用D触发器构成并行寄存器图2所示为用D触发器构成四位并行寄存器。

为异步清零控制端,高电平有效。

当时,各触发器输出端Q的状态,取决于CLK上升沿时刻的D端状态。

2.移位寄存器(1)用D触发器构成移位寄存器图3 用D触发器构成4位串行移位寄存器图3所示为用D触发器构成的4位串行移位寄存器。

其中左边第一个触发器的输入端接收输入数据,其余的每一个触发器的输入端均与左边相邻的触发器的Q端连接。

当时钟信号CLK的上升沿时刻,各触发器同时接收输入数据。

四位寄存器的所存数据右移一位。

(2)双向移位寄存器74LS194图4 双向移位寄存器74LS194逻辑框图图4 所示为集成电路芯片双向移位寄存器74LS194逻辑框图。

为便于扩展逻辑功能,在基本移位寄存器的基础上增加了左右移控制、并行输入、保持和异步清零等功能。

74LS194的逻辑功能如表1所列。

表13.用移位寄存器构成计数器(1)环形计数器图5 环形计数器如果将移位寄存器的串行移位输出端接回到串行移位输入端,如图5所示。

那么,在时钟CLK的作用下,寄存器里的数据将不断循环右移。

例如,电路的初始状态为,则电路的状态转换图如图6所示。

可以认为,这是一个模4计数器。

图6 环形计数器状态转换图实验内容及步骤1. 用两片74LS74构成四位移位寄存器(1)74LS74引脚图图10 74LS74引脚图(2)用74LS74构成四位移位寄存器图11 用74LS74构成四位移位寄存器实验电路按照图11连接电路。

首先设置,使寄存器清零。

然后,设置,在CLK输入端输入单次脉冲信号当作时钟信号,通过输出端的发光二极管观察的状态,判断移位的效果。

实验八 移位寄存器及其应用一、实验目的1.熟悉移位寄存器的结构及工作原理 2.了解移位寄存器的应用。

二、实验原理移位寄存器是具有移位功能的寄存器。

它是一种由触发器链型连续组成的同步时序网络。

代码的移位是在统一的位移脉冲CP 控制下进行的。

每来一个移位位脉冲,原存贮于寄存器的信息代码就按规定的方向(左方或右方)同步移一位。

移位寄存器的类型,按移位的方式可分为左移﹑右移和双向移位寄存器;按其输入输出方式可分为并行输入—并行输出﹑并行输入—串行输出﹑串行输入—并行输出和串行输入—串行输出等几种。

移位寄存器应用较广。

利用移位寄存器可以构成计数分频电路﹑序列信号发生器、串/并行代码转换器、延时电路等。

移位寄存器的状态转移是按移存规律进行的,一般称为移存型计数器。

常用的移存型计数器有环行计数器和扭环形计数器。

下面介绍几种常用的MSI 移位寄存器及其应用。

74LS195为4位并行存取移位寄存器;74LS194为4位双向通用移位寄存器,它具有左移﹑右移﹑并行输入数据﹑保持及清除等五种功能。

它们的功能表及管脚图见附录. 应用举例:(一)移存型计数器 (1) 环形计数器环形计数器的特点是环形计数器的计数模数M=移位寄存器位数N ,且工作状态是依次循环出1或0,如4为环形计数器状态为0001-0010-0100-1000或1110-1101-1011-0111。

设计该类计数器往往要求电路能自启动。

(2) 扭环计数器扭环计数器又称为约翰逊计数器。

其特点是四位扭环计数器具有N=2n=8个有效计数状态,且相邻两状态间只有一位代码不同,因此扭环计数器的输出所驱动的组合网络不会产生功能竞争。

(3) 任意进制移存型计数器只要状态转移关系符合移存规律的计数器,就称为移存型计数器。

移存型计数器只要M ≠2N 时,就要考虑计数器的自启动问题。

移存型计数器子启动的方法有两种:①、 改变移位寄存器串行输入D 0的反馈方程,例如:让循环出“1”的4位环形计数器的D 0=012Q Q Q ++,使全“0”状态时的的D 0=1;如果是循环出“0”的4位环形计数器,则0120Q Q Q D =,使全“1”状态时的D 0=0,从而实现自启动。

基于集成移位寄存器的扭环形计数器自启动设计马敬敏【期刊名称】《浙江大学学报(理学版)》【年(卷),期】2013(40)1【摘要】Both state transition in twisted ring counters and logic function in shift registers are analyzed.Some new schemes for design of twisted ring counters based on shift register 74LS194 are purposed.State transition of shift registers is kept right shift or input numbers are accord with right shift rules,and the feedbacks carry out reverse circulation shift.Based on these rules,logic modification to the excitation function of any flip-flop could realize selfcorrection in twisted ring counters.The innovation of this method is that a logic modification method is proposed to change the application direction of MSI shift register.%分析了扭环形计数器工作时的状态转换过程,分析了集成移位寄存器的逻辑功能,提出了用集成移位寄存器74LS194构成扭环形计数器的一些新的设计方案,即移位寄存器的状态变化在右移移位或并行输入符合右移规律的数码、反馈实现取反循环移位的基础上,对任何一位触发器的激励函数进行逻辑修改,可实现扭环形计数器自启动设计.所述方法的创新点是提出了MSI集成移位寄存器改变应用方向的逻辑修改方法.【总页数】4页(P47-50)【作者】马敬敏【作者单位】渤海大学实验管理中心,辽宁锦州121000【正文语种】中文【中图分类】TP332.1+2【相关文献】1.扭环型计数器自启动设计的逻辑修改方案 [J], 任骏原2.基于74LS161的扭环形计数器自启动设计 [J], 马敬敏;伦淑娴3.基于扭环形计数器设计交通信号灯自动控制电路 [J], 杨海明;孔维成;李悦;王宏干;曹学军4.基于次态卡诺图的移位寄存器型计数器的自启动设计 [J], 腾香5.基于FPGA的环形计数器与扭环形计数器 [J], 张铭郎;于业弘;解宇;李恩来;刘丽娟因版权原因,仅展示原文概要,查看原文内容请购买。